DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS CHENNAI - 600036

# ELLIPTIC CURVE CRYPTO PROCESSOR

A Project Report

Submitted by

# PATWARDHAN VINOD VIDYADHAR EE19M055

In the partial fulfilment of requirements

For the award of the degree

Of

MASTER OF TECHNOLOGY

June 2021

**CERTIFICATE**

This is to undertake that the Project report titled ELLIPTIC CURVE CRYPTO PRO-

**CESSOR**, submitted by me to the Indian Institute of Technology Madras, for the award

of M.Tech, is a bona fide record of the research work done by me under the supervision

of **Prof Veezhinathan Kamakoti**. The contents of this Project report, in full or in parts,

have not been submitted to any other Institute or University for the award of any degree

or diploma.

In order to effectively convey the idea presented in this Thesis, the following work

of other authors or sources was reprinted in the Thesis with their permission:

• Rebeiro, C.(2009). ARCHITECTURE EXPLORATIONS FOR ELLIPTIC CURVE-CRYPTOGRAPHY ON FPGAS. Doctoral thesis, DEPARTMENT OF COM-

PUTER SCIENCE AND ENGINEERING, IIT-Madras, Chennai – 600036

Place: Chennai 600 036

**Date: 18 June 2021**

PATWARDHAN VINOD VIDYADHAR

EE19M055

Prof Veezhinathan Kamakoti

Research Guide

Dr. Anbarasu Maniyannan

Research Co-Guide

©2021 Indian Institute of Technology Madras

#### **ACKNOWLEDGEMENTS**

Foremost, I would like to thank my guide Prof Veezhinathan Kamakoti, who gave me an opportunity to be a part of Shakti Project.

I would also like to thank Dr. Anbarasu Manivannan for being my co-guide, which me gave an opportunity for taking up the project outside of Electrical department.

I am grateful to Project Associates Arjun and Varun for their encouragement, advice, and help whenever needed. I appreciate their constant involvement in my project from the scratch.

I would like to take this opportunity to acknowledge my friends for providing all the emotional support and entertainment. I would like to thank my family for their love and encouragement, without their support this M.Tech program would not have been possible.

Patwardhan Vinod Vidyadhar

#### **ABSTRACT**

Communications have grown at a breakneck pace in the modern era. Online banking, personal digital assistants, mobile communication, smart-cards, and other applications have highlighted the importance of security in resource-constrained contexts. Despite there being protocols for security purposes such as RSA, the ECC is gaining popularity for its smaller key sizes offering the same level of security.

Hardware efficient architectures are put together to form the processor. For finite field multiplication, General Karatsuba which efficient for smaller bit size multiplications and Simple Karatsuba suitable for large bit size multiplications, are combined together as Hybrid Karatsuba, to gives best performance.

Multiplicative inverse being another crucial operation in ECC, is implemented using Quad-Itoh Tsujii algorithm instead of the conventional Itoh-Tsujii algorithm. This ensures least time for computation.

The above two proposed hardware primitives in Chester's work are implemented to form an accelerator. The performance of this accelerator is significantly enhanced due to these proposed primitives. Further, this accelerator is modified to be resistant from Simple timing and Power analysis side channel attacks.

# TABLE OF CONTENTS

|        |         |                                      | Page |

|--------|---------|--------------------------------------|------|

| ACKN   | OWLED   | GEMENTS                              | i    |

| ABSTE  | RACT .  |                                      | ii   |

| LIST C | F TABI  | LES                                  | v    |

| LIST C | F FIGU  | URES                                 | vi   |

| ABBRI  | EVIATIO | ONS                                  | vii  |

| CHAP   |         | INTRODUCTION                         | 1    |

| 1.1    | Motiva  | ntion                                | 2    |

| СНАР   | ΓER 2:  | Mathematical Background              | 3    |

| 2.1    | Binary  | Finite Fields                        | 4    |

| 2.2    |         | Curves                               | 7    |

|        | 2.2.1   | Projective Coordinate Representation | 10   |

| CHAP   | ΓER 3:  | Finite Field Multiplier              | 12   |

| 3.1    | Karats  | uba Multiplication                   | 12   |

| 3.2    | Karats  | uba Multipliers in ECC               | 14   |

| CHAP   | ΓER 4:  | Finite Field Inversion               | 17   |

| 4.1    | Itoh-Ts | sujii Algorithm                      | 17   |

| 4.2    | Quad I  | toh-Tsujii Algorithm                 | 19   |

| 4.3    | Quad I  | Block                                | 21   |

| CHAP   | ΓER 5:  | Elliptic Curve Crypto Processor      | 23   |

| 5.1    | Blocks  | of Cryptoprocessor                   | 24   |

|        | 5.1.1   | Register Bank                        | 24   |

|        | 5.1.2   | Arithmetic Unit                      | 26   |

|        | 5.1.3   | Control Unit                         | 27   |

| 5.2               | Implen                                   | nenting Point Arithmetic           | 27                   |

|-------------------|------------------------------------------|------------------------------------|----------------------|

|                   | 5.2.1                                    | Point Doubling                     | 27                   |

|                   | 5.2.2                                    | Point Addition                     | 28                   |

| 5.3               | Finite S                                 | State Machine                      | 30                   |

| 5.4               | Results                                  |                                    | 34                   |

|                   | 5.4.1                                    | BSV Simulation results             | 34                   |

| 5.5               | Synthe                                   | sis Report                         | 35                   |

|                   | 5.5.1                                    | Arithmetic Unit                    | 36                   |

|                   | 5.5.2                                    | Register Module                    | 38                   |

|                   |                                          |                                    |                      |

| СНАРТ             | ER 6:                                    | Side Channel Attack Resistant ECCP | 39                   |

| <b>CHAPT</b> 6.1  |                                          | Side Channel Attack Resistant ECCP | 39<br>39             |

|                   | Timing                                   |                                    |                      |

| 6.1               | Timing Solutio                           | analysis                           | 39                   |

| 6.1<br>6.2        | Timing<br>Solutio<br>Modifie             | analysis                           | 39<br>40             |

| 6.1<br>6.2<br>6.3 | Timing<br>Solutio<br>Modifie             | analysis                           | 39<br>40<br>41       |

| 6.1<br>6.2<br>6.3 | Timing<br>Solutio<br>Modified<br>Results | analysis                           | 39<br>40<br>41<br>45 |

# LIST OF TABLES

| <b>Fable</b> | Title                                                           | Page     |

|--------------|-----------------------------------------------------------------|----------|

| 2.1          | Left to right algorithm illustration                            | 10       |

| 4.1<br>4.2   | Generic ITA for $GF(2^{233})$                                   | 19<br>20 |

| 5.1          | Role of Registers                                               | 25       |

| 5.2          | Scheduling of Point Doubling operations                         | 28       |

| 5.3          | Parallel LD Point Additionon the ECCP                           | 30       |

| 5.4          | Register Module Input and Outputs,[Mukhopadhyay and Chakraborty |          |

|              | (2014)]                                                         | 32       |

| 5.5          | Control Words,[Mukhopadhyay and Chakraborty (2014)]             | 33       |

| 6.1          | Control Words when the preceding key bit is 1                   | 43       |

| 6.2          | Control Words when the preceding key bit is 0                   | 44       |

# LIST OF FIGURES

| Figure | Title                                                         | Page |

|--------|---------------------------------------------------------------|------|

| 2.1    | Hierarchy                                                     | 3    |

| 2.2    | Squarer                                                       | 5    |

| 2.3    | Modular Reduction                                             | 6    |

| 2.4    | Inverse of an elliptic curve point                            | 7    |

| 2.5    | Double of an elliptic curve point                             | 8    |

| 2.6    | Addition of elliptic curve points                             | 9    |

| 3.1    | Computing M $'(x)$                                            | 13   |

| 3.2    | Hybrid Karatsuba Multiplier for 233 bits                      | 14   |

| 4.1    | Quad block                                                    | 22   |

| 5.1    | Elliptic Curve Crypto Processor                               | 23   |

| 5.2    | Register File for Elliptic Curve Crypto Processor             | 24   |

| 5.3    | Arithmetic Unit                                               | 26   |

| 5.4    | FSM for ECCP                                                  | 31   |

| 5.5    | Simulation result for $key = 2 \dots \dots \dots \dots$       | 34   |

| 5.6    | Simulation result for $key = 2^{233} - 1 \dots \dots \dots$   | 35   |

| 5.7    | ECCP resource utilisation                                     | 35   |

| 5.8    | AU resource utilisation                                       | 36   |

| 5.9    | Hybrid Karatsuba Multiplier resource utilisation              | 37   |

| 5.10   | Quad block resource utilisation                               | 37   |

| 5.11   | Squarer circuit resource utilisation                          | 38   |

| 5.12   | Register module resource utilisation                          | 38   |

| 6.1    | Always Add Method to Prevent SPA                              | 40   |

| 6.2    | Modified FSM                                                  | 42   |

| 6.3    | Modified Register Module                                      | 42   |

| 6.4    | Simulation result for $key = 2 \dots \dots \dots \dots \dots$ | 45   |

| 6.5    | Simulation result for $key = 2^{233} - 1 \dots \dots \dots$   | 45   |

| 6.6    | Modified Register Module resource utilisation                 | 46   |

| 6.7    | SR-ECCP resource utilisation                                  | 46   |

# **ABBREVIATIONS**

AU Arithmetic Unit

ASIC Application Specific Integrated Circuit

ECC Elliptic Curve Cryptography

ECCP Elliptic Curve Crypto Processor

EEA Extended Euclid's Algorithm

FPGA Field Programmable Gate Array

FSM Finite State Machine

GF Galois Field

ITA Itoh-Tsujii Algorithm

LD Lopez-Dahab

LUT Look Up Table

RSA Rivest Shamir Adleman

SPA Simple Power Analysis

SR-ECCP SPA Resistant Elliptic Curve Crypto Processor

BSV Bluespec System Verilog

#### **CHAPTER 1**

#### INTRODUCTION

Communications across wired and wireless networks have increased dramatically in this period. With people preferring online shopping, the daily transactions have increased. These transactions involve sensitive data such as account details, which need to be kept private, and also authorised users should only be able to initiate these transactions. Also, there has been recent rise in *Cryptocurrency* investment, there is a need to ensure that funds can only be spent by their rightful owners. Hence, there is need of robust security framework.

Cryptology is the science concerned with data communication and storage in encrypted form. This ensures only authorised users with the right key can decrypt the encrypted data. Cryptology comprises of Cryptography and Cryptanalysis. The former entails the study and application of techniques, which encrypt the data, making it accessible only to the intended user. Cryptanalysis, on the other hand, is the study of decrypting crypto systems and recovering the hidden data.

Based on the key, cryptography can be classified as *Symmetric* and *Asymmetric*. In *Symmetric key* algorithms, a single key is use for both encryption and decryption. This ensures fast process but the secret key has to be shared between parties for communication. On the other hand, *Asymmetric key* algorithms uses two keys, public and private. The former is used to encrypt the data and also it is generally known whereas the latter is used to decrypt and is kept confidential. Hence, asymmetric key algorithms are complex and slow but, the underlying primitives used are based on integer factorization and discrete logarithm problems which are hard to crack. ECC also belongs to this category.

Another component of Cryptology, Cryptanalysis deals with exploiting the cryptographic algorithms weakness to get the secured data. Conventional brute force method to get the encrypted data isn't feasible anymore as it would require large data and also computation time. Hence, recent Cryptanalysis techniques focus on implementation of algorithms to attack. These techniques include gathering information from timing, power, acoustic, radiation characteristics of the systems and using them to get the secret key. Optimised architectures are more prone to these side channel attacks. Hence, we need to take care of these side channel attacks while designing our cryptographic systems.

#### 1.1 Motivation

Efficient implementation of algorithms is required to take care of the complex mathematical computations. There are two ways to achieve this: *Software* and *Hardware*. *Software* implementation [Rebeiro *et al.* (2006)] is low cost and easy to tweak. However, due to architecture limitations of microprocessor on which this is implemented, this scheme cannot perform certain large computations efficiently. Therefore, a dedicated *Hardware* implementation is suitable for public key cryptographic algorithms which involve such large computations. However, design of hardware is expensive and time consuming process, also memory being the problem. Hence, design which can utilise the resources of *FPGA* efficiently and as well take care of timing constraints, be preferred. With the increasing security threats there is also a need to design architectures and algorithms which are not susceptible to attacks.

## **CHAPTER 2**

# **Mathematical Background**

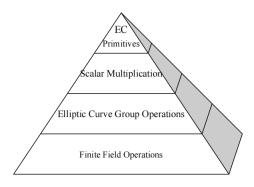

To understand *Elliptic Curve Cryptography* (ECC) we need to know about the underlying mathematical operations of *Finite field*, *Elliptic curve group*, *scalar multiplication* and *ECC primitives*. Fig. 2.1 shows the various operations involved in building ECCP.

Fig. 2.1: Hierarchy Rebeiro (2009)

First of all, we need a *field* (or commutative ring) which has finite number of elements to work upon. Hence, we choose finite fields also known as *Galois* fields denoted by  $GF(p^m)$ . Here p(prime number) is known as the *characteristic* of the field and  $m \geq 0$ . The *Order* of finite field is the number of elements present in that field and is equal to  $p^m$ .

There are two kinds of finite field which are popular in Cryptography: *Prime field* and *Binary finite field*. In prime fields, m=1, whereas in binary fields, p=2. Binary Galois field ( $GF(2^m)$ ) elements can be represented using m bits, which is not possible in prime fields. Also, in binary fields the hardware required for arithmetic operations like addition and squaring is quite simpler. Therefore, we choose to work on binary fields.

## 2.1 Binary Finite Fields

Any  $GF(2^m)$  element can be expressed as,  $a(x) = a_{m-1} x^{m-1} + \dots + a_1 x + a_0$ , where the coefficients belong to GF(2).

Alternatively, a(x) can be represented as binary number  $(a_{m-1},...,a_1,a_0)$  which allows for easy storage and computation. Consider the polynomial in the field  $GF(2^{12})$ ,  $x^{11} + x^8 + x^5 + x^3 + x + 1$ . This can also be represented as  $(100100101011)_2$ .

Various arithmetic operations can be performed with ease in Binary finite field. Addition and Subtraction are similar in GF(2) as there is no carry forwarding involved, hence these are computed using XOR operation. Some of the arithmetic operations are discussed below.

**Addition/Subtraction :** Consider two elements in the field  $GF(2^m)$  as shown below,

$$c(x) = \sum_{i=0}^{m-1} c_i x^i$$

$d(x) = \sum_{i=0}^{m-1} d_i x^i$

the addition/subtraction of these is given by

$$c(x) \pm d(x) = \sum_{i=0}^{m-1} (c_i \oplus d_i) x^i$$

(2.1)

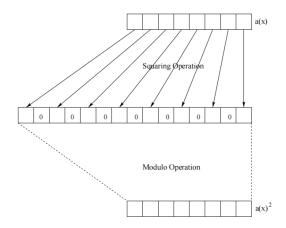

**Squaring :** Considering the same element  $c(x) \in GF(2^m)$  mentioned above, its square is given as follows.

$$c(x)^{2} = \sum_{i=0}^{m-1} c_{i} x^{2i} \mod p(x)$$

(2.2)

After squaring the length of the input increases such that, for m bits input the output would be of 2m-1 bits as shown in Fig. 2.2.

Fig. 2.2: Squarer Rebeiro (2009)

Multiplication is not so straightforward as addition and squaring. Multiplying the above elements c(x) and d(x) would give,

$$c(x).d(x) = (\sum_{i=0}^{n-1} d(x)c_i x^i) \mod p(x)$$

(2.3)

We will look at finite field multiplier and inversion with great detail in the following chapters.

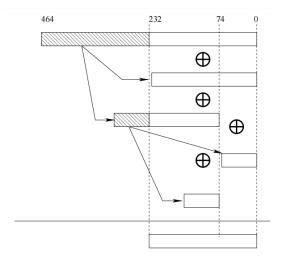

**Modular Reduction:** The squaring and multiplication results have bit sizes greater than m for  $GF(2^m)$ . Hence, to get back the result to intended number of bits a modular operation is required. This is done by dividing the output with an irreducible polynomial. [Mahboob (2004)]

Fig. 2.3: Modular Reduction Rebeiro (2009)

Consider the irreducible trinomial  $x^m + x^n + 1$ , which has a root  $\alpha$  (1 < n < m/2), giving  $\alpha^m + \alpha^n + 1 = 0$ . Therefore,

$$\alpha^{m} = 1 + \alpha^{n}$$

$$\alpha^{m+1} = \alpha + \alpha^{n+1}$$

$$\vdots$$

$$\alpha^{2m-3} = \alpha^{m-3} + \alpha^{m+n-3}$$

$$\alpha^{2m-2} = \alpha^{m-2} + \alpha^{m+n-2}$$

$$(2.4)$$

For example, consider the irreducible trinomial  $x^{233} + x^{74} + 1$  [National Institute of Standards and Technology (1994)]. The multiplication or squaring of the elements in  $GF(2^{233})$  would result in maximum of 465 bits. These 465 bits can be reduced to 233 bits as shown in Fig. 2.3 using Equation 2.4.

# 2.2 Elliptic Curves

**Definition 2.2.1** The simplified form of the *Weierstrass* equation yields an elliptic curve (in  $GF(2^m)$ ). The Weierstrass equation in its simplest form is :

$$y^2 + xy = x^3 + ax^2 + b (2.5)$$

with the coefficients a and b in  $GF(2^m)$  and if  $b \neq 0$  it is known as non-singular curve.

Elements of Elliptic curve doesn't form a group as such, unless, we introduce one more element known as *point at infinity* ( $\mathcal{O}$ ). It also acts as an identity element of the group. Given below are the operations that can be performed on this group.

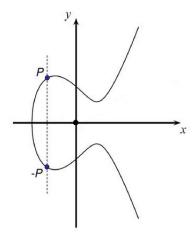

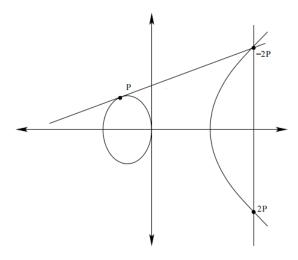

**Point Inversion :** The inverse of a point  $P(x_1, y_1)$  is found as shown in Fig. 2.4. The coordinates of -P are  $(x_1, x_1 + y_1)$ .

Fig. 2.4: Inverse of an elliptic curve point.

Rebeiro (2009)

**Point Doubling:** To compute the double of a point  $P(x_1, y_1)$  on an elliptic curve, a tangent to the curve is drawn passing through this point. The tangent would intersect the curve at another point which is -2P as shown in Fig. 2.5 taking the inverse of this point would give us the required result. The equations for  $2P(x_3, y_3)$  are as follows:

$$x_3 = \lambda^2 + \lambda + a = x_1^2 + \frac{b}{x_1^2}$$

$$y_3 = x_1^2 + \lambda x_3 + x_3$$

(2.6)

where  $\lambda = x_1 + (y_1/x_1)$ .

Fig. 2.5: Double of an elliptic curve point Rebeiro (2009)

**Point Addition :** The addition of points on elliptic curve say  $P(x_1, y_1)$  and  $Q(x_2, y_2)$  is found out as shown in Fig. 2.6. A line is drawn passing through these points, intersecting the curve at a third point, which is the inverse of (P + Q). Taking the inverse of this point would give us the result. Suppose  $R(x_3, y_3) = (P + Q)$ , then

$$x_3 = \lambda^2 + \lambda + x_1 + x_2 + a$$

$$y_3 = \lambda(x_1 + x_3) + x_3 + y_1$$

(2.7)

where  $\lambda = (y_1 + y_2)/(x_1 + x_2)$ . For P = -Q, the addition would result in  $\mathcal{O}$ .

Fig. 2.6: Addition of elliptic curve points

Rebeiro (2009)

**Scalar/Point Multiplication :** Point multiplication of a point(P) on elliptic curve with a scalar(k) is nothing but adding P with itself k-1 times. Since this would take a lot of time to compute, many algorithms are suggested in literature. Among these we are implementing *Left to Right* or *MSB first* algorithm, given in Algorithm 2.1.

#### **Algorithm 2.1:** Left to Right algorithm

**Input**: Basepoint  $P = (p_x, p_y)$  and Scalar  $k = (k_{m-1}, k_{m-2}, ..., k_0)_2$ , where  $k_{m-1} = 1$

**Output:** Point on the curve Q + kP

1 Q = P

2 **for** i = m-2 **to** 0 **do**

$Q = 2 \cdot Q$

4 if  $k_i = 1$  then

Q = Q + P

6 end

7 end

#### Mukhopadhyay and Chakraborty (2014)

The Table 2.1 illustrates Algorithm 2.1, considering k = 25 or  $(11001)_2$ .

Table 2.1: Left to right algorithm illustration

| i | $k_i$ | Operation      | Q   |

|---|-------|----------------|-----|

| 3 | 1     | Double and Add | 3P  |

| 2 | 1     | Double only    | 6P  |

| 1 | 1     | Double only    | 12P |

| 0 | 0     | Double and Add | 25P |

For every iteration i doubling operation takes place, while addition is carried out only when  $k_i = 1$ . From Equations 2.6 and 2.7 we can see that doubling as well as addition require 2 multiplications along with 1 inversion. The number of additions is directly proportional to the number of 1's present in the scalar key, which would also mean the number of inversions going up.

#### 2.2.1 Projective Coordinate Representation

Finite field inversion is the most complicated operation. So, there is need to reduce these operations to the extent possible. The equations discussed till now in section 2.2 dealt with only two point coordinate system (x, y) also known as *Affine* coordinates. By, introducing a third point in the coordinate system i.e (X, Y, Z) there is a scope to reduce the number of Inversions. This coordinate system is known as *Projective* representation. In general, x and y are replaced with  $\frac{X}{Z^c}$  and  $\frac{Y}{Z^d}$  respectively. Various representations are suggested in literature to make one to one correspondence from affine to projective representations by changing the values of c and d. In this work, c = 1 and d = 2 and the resulting points are known as  $L \acute{o}pez-Dahab(LD)$  coordinates[Menezes et al. (1996)].

Equations 2.5, 2.6 and 2.7 are modified accordingly  $(x \to \frac{X}{Z^c}, y \to \frac{Y}{Z^d})$  to get Equation 2.8, 2.9 and 2.10.

$$Y^2 + XYZ = X^3 + aX^2Z^2 + bZ^4 (2.8)$$

For *Point Inversion*, with  $P(X_1, Y_1, Z_1)$ , the inversion point -P has coordinates  $(X_1, X_1Z_1 + Y_1, Z_1)$ . In LD, the point at infinity,  $\mathcal{O}$  is represented as (1, 0, 0).

When the point P in LD is doubled, the result is the point 2P with coordinates  $(X_3, Y_3, Z_3)$ , given by the equations below. The number of multiplications have gone up by 3 whereas the inversions have reduced to zero.

$$Z_{3} = X_{1}^{2}.Z_{1}^{2}$$

$$X_{3} = X_{1}^{4} + b.Z_{1}^{4}$$

$$Y_{3} = b.Z_{1}^{4}.Z_{3} + X_{3}.(a.Z_{3} + Y_{1}^{2} + b.Z_{1}^{4})$$

(2.9)

The equations for *Addition* involving one point in affine,  $Q(x_2, y_2)$  and another in LD coordinate systems,  $P(X_1, Y_1, Z_1)$ ,  $P + Q = (X_3, Y_3, Z_3)$  (with  $Q \neq \pm P$ ) are given as follows:

$$A = y_2 \cdot Z_1^2 + Y_1$$

$$B = x_2 \cdot Z_1 + X_1$$

$$C = Z_1 \cdot B$$

$$D = B^2 \cdot (C + a \cdot Z_1^2)$$

$$Z_3 = C^2$$

$$E = A \cdot C$$

$$X_3 = A^2 + D + E$$

$$F = X_3 + x_2 \cdot Z_3$$

$$G = (x_2 + y_2) \cdot Z_3^2$$

$$Y_3 = (E + Z_3) \cdot F + G$$

(2.10)

The number of multiplications have gone up by 7 whereas the inversions have reduced to zero.

The advantage of using LD coordinates is that, no intermediate inversions are required other than one inversion at the end to convert the LD to affine coordinate representation.

## **CHAPTER 3**

# Finite Field Multiplier

We have increased the number of finite field multiplications by opting LD coordinate system. So, we have to choose the multiplier which is efficient, as the multiplier has longest latency and it decides the operating frequency. Finite field multiplication essentially involves two steps. Firstly, multiplying two elements of field which results in output not belonging to  $GF(2^m)$ . Secondly, the result produced is reduced using an irreducible polynomial to get the output in  $GF(2^m)$ .

Consider C(x), D(x) and  $P(x) \in GF(2^m)$ , where P(x) is an irreducible polynomial. Let M'(x) = C(x). D(x). The result  $M'(x) \notin GF(2^m)$ , hence it is reduced as shown below.

$$M(x) = M'(x) \operatorname{mod} P(x)$$

$$= C(x).D(x) \operatorname{mod} P(x)$$

(3.1)

After going through a lot of literature work, Karatsuba Multiplier was found to be efficient for high performance applications as it has a sub-quadratic space complexity  $(O(m^{\log_2 3}), m \text{ being the number of operand bits})$ . The same was implemented in Rebeiro (2009)

## 3.1 Karatsuba Multiplication

This multiplier performs small bit size multiplications by splitting the operands and finally combining the partial results appropriately. The m bit multiplicands C(x) and D(x) are split into two m/2 bits as shown in Equation 3.2.  $C_h$ ,  $C_l$ ,  $D_h$  and  $D_l$  are of m/2 bits each.

$$C(x) = C_h x^{m/2} + C_l$$

$D(x) = D_h x^{m/2} + D_l$  (3.2)

As we can see from Equation 3.3, we don't need m bit multiplication to get the result rather using three m/2 multiplications would get the job done.

$$M'(x) = (C_h x^{m/2} + C_l)(D_h x^{m/2} + D_l)$$

$$= C_h D_h x^m + (C_h D_l + C_l D_h) x^{m/2} + C_l b_l$$

$$= C_h D_h x^m$$

$$+ ((C_h + C_l)(D_h + D_l) + C_h D_h + C_l D_l) x^{m/2}$$

$$+ C_l D_l$$

(3.3)

The generated partial products are then combined to get the final result as shown below in the Fig. 3.1.

Fig. 3.1: Computing M ′(x)

Rebeiro (2009)

This M '(x) is further reduced by irreducible polynomial as given in Section 2.1. This splitting of multiplicands can be further carried out with m/4 bits each. Then we would require a total of nine m/4 multiplications. This recursive application of Karatsuba multiplication can be applied till the multiplicands are of 2 bits. Then the final recursion can be achieved using AND gates. Hence, m being a power of 2 would be best suited for Karatsuba multiplication and is known as Basic Karatsuba Multiplier.

## 3.2 Karatsuba Multipliers in ECC

Since the fields used in ECC have a prime degree, the Basic Karatsuba cannot be applied for finite field multiplication. There are two ways to use this multiplication technique for our ECCP:

- Sequential circuit approach, where the output is fed back into the same circuit

at every clock cycle. This approach requires less hardware but at the expense of

consuming more clock cycles.

- Combinational circuit approach, which can produce the output in one clock cycle at the expense of large area.

Second approach is implemented in this work as we are interested in making a performance optimised ECC processor.

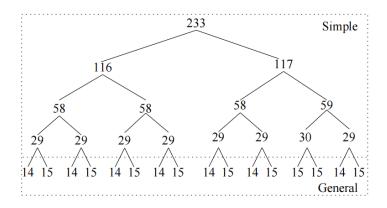

The *Simple Karatsuba multiplier*[Weimerskirch and Paar (2006)] is similar to basic Karatsuba multiplier. The m bit multiplicands are divided as shown in Equation 3.1. Hence, we need three m/2 bit multiplications to generate partial products.

*General Karatsuba multiplier*[Weimerskirch and Paar (2006)], does follow recursion but instead of splitting the multiplicands into two terms it does it in more than two.

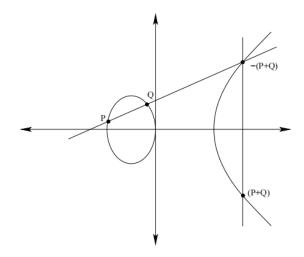

The proposed multiplier in [Rebeiro (2009)] is a combination of the above two variants, which I too have implemented. This combined multiplier is known as *Hybrid Karatsuba Multiplier*. For, multiplicands with bits sizes < 29, the general Karatsuba algorithm is applied as it ensures maximum LUT's utilisation. And for bit sizes greater than 29, simple Karatsuba is invoked as it makes sure least gate count for higher bi multiplications. The recursion for 233 bit Hybrid Karatsuba multiplier is as shown below in Fig. 3.2.

Fig. 3.2: Hybrid Karatsuba Multiplier for 233 bits Rebeiro (2009)

Algorithms for implementing general Karatsuba and Hybrid Karatsuba are given below in Algorithm 3.1 ad 3.2 respectively.

Algorithm 3.1: gkmul (General Karatsuba Multiplier)

```

Input: A and B \Longrightarrow m bits

Output: C \Longrightarrow (2m-1) bits

/* Define : M_x \rightarrow A_x B_x */

/* Define : M_{(x,y)} \to (A_x + A_y)(B_x + B_y) */

begin

1

for i = 0 to m - 2 do

C_i = C_{2m-2-i} = 0

3

for j = 0 to [i/2] do

4

if i = 2j then

5

C_i = C_i + M_i

6

C_{2m-2-i} = C_{2m-2-i} + M_{m-1-i}

7

else

8

C_i = C_i + M_i + M_{i-1} + M_{i,i-1}

C_{2m-2-i} = C_{2m-2-i} + M_{m-1-i} + M_{m-1-i+j} + M_{m-1-j,m-1-i+j}

10

end

11

12

end

end

13

C_{m-1} = 0

14

for j = 0 to [(m-1)/2] do

15

if m-1 = 2j then

16

C_{m-1} = C_{m-1} + M_i

17

else

18

C_{m-1} = C_{m-1} + M_i + M_{m-1-i} + M_{(i,m-1-i)}

19

end

20

end

21

end

```

Mukhopadhyay and Chakraborty (2014)

#### Algorithm 3.2: hmul (Hybrid Karatsuba Multiplier)

```

Input: A and B \Longrightarrow m bits

Output: C \Longrightarrow (2m-1) bits

begin

if m < 29 then

return gkmul (A,B,m)

3

else

4

1 = [m/2]

5

A' = A_{[m-1,...,l]} + A_{[l-1,...,0]}

B' = B_{[m-1,...,l]} + B_{[l-1,...,0]}

7

C_{p1} = \operatorname{hmul} \left( A_{[l-1,\dots,0]}, B_{[l-1,\dots,0]}, \mathbf{l} \right)

8

C_{p2} = hmul (A ',B ',l)

C_{p3} = \text{hmul} (A_{[m-1,...,l]}, B_{[m-1,...,l]}, \text{m-l})

return (C_{p3} << 21) + (C_{p1} + C_{p2} + C_{p3}) << 1 + C_{p1}

11

/* < < indicates left shift */

end

12

13

end

```

Mukhopadhyay and Chakraborty (2014)

#### **CHAPTER 4**

#### **Finite Field Inversion**

In  $GF(2^m)$ , the inverse of any non zero element a is such that  $a \cdot a^{-1} = a^{-1} \cdot a = 1$ , with  $a^{-1} \in GF(2^m)$ . In spite of reducing the number of inversions by introducing LD coordinate system, we cannot completely eliminate field inversion operation. Therefore, it is necessary to design an efficient multiplicative inverse technique. *Extended Euclidean algorithms* (EEA) and the *Itoh-Tsujii* (ITA) are the most widely used algorithms to compute multiplicative inverse. In this work, Itoh-Tsujii algorithm is implemented as it is faster compared to EEA, but at the expense of using multiplier which consumes large area . Since we require finite field multiplier in our ECCP, we don't need extra multiplier for computing inversion separately. The same multiplier unit can be used to compute inversion. Hence, ITA is the best choice.

# 4.1 Itoh-Tsujii Algorithm

According to Fermat's little theorem, the inverse of an element  $a \in GF(2^m)$  can be determined as given in Equation 4.1. This forms the basis for ITA.

$$a^{-1} = a^{2m-2} (4.1)$$

Implementing  $a^{-1}$  using the rudimentary method necessitates (m-1) squares and (m-2) multiplications. The number of multiplications need to be reduced as it has the longer latency. This can be achieved by using *addition chains*. A sequence of integers  $(n \in N)$  can form an *addition chain* if the following properties are satisfied.

$$U = (u_0 \ u_1 \ u_2 \ . \ . \ u_r).$$

- $u_o = 1$

- $\mathbf{u}_r = \mathbf{n}$

- $u_i = u_j + u_k$ , where  $k \le j < i$

If j = i - 1 in above condition then the addition chains are known as *Brauer chains*. There are many ways to form an addition chain for given n but the one with minimum length is said to be optimal.

Reusing the notations from [Rodríguez-Henríquez *et al.* (2007)] for  $\beta_k(a)$ , Equation 4.1 can be expressed as below.

$$a^{-1} = (a^{2^{m-1}-1})^2$$

$$\beta_k(a) = a^{2^k-1} \in GF(2^m), k \in \mathbb{N}$$

$$a^{-1} = [\beta_{m-1}(a)]^2$$

$\beta_{k+j}(a) \in GF(2^m)$  can be resolved as shown in Equation 4.2. This property along with addition chain is used in recursive manner to compute multiplicative inverse. (Note:  $\beta_k(a)$  is denoted as  $\beta_k$ )

$$\beta_{k+j}(a) = (\beta_j)^{2k} \beta_k = (\beta_k)^{2j} \beta_j \tag{4.2}$$

For  $a \in GF(2^{233})$ , the inverse is obtained by squaring  $\beta_{232}(a)$ , where  $\beta_{232}(a) = a^{2^{232}-1}$ . A Brauer chain for 232 is as considered below.

$$U_1 = (1 \ 2 \ 3 \ 6 \ 7 \ 14 \ 28 \ 29 \ 58 \ 116 \ 232)$$

(4.3)

$\beta_{232}(a)$  computation is shown in Table 4.1. It requires a total of 231 squarings and 10 multiplications.

In general for  $GF(2^m)$ , with addition chain of length l, we need a total of m-1 squarings and l-1 multiplications. The addition chain length, l is related to m as  $l \leq \lfloor log_2 m \rfloor$ . As a result, the ITA requires a substantially smaller number of multiplications than the conventional technique.

Table 4.1: Generic ITA for  $GF(2^{233})$

|    | $\beta_{ui}$ (a) | $\beta_{u_j+u_k}$ (a) | Exponentiation                                         |

|----|------------------|-----------------------|--------------------------------------------------------|

| 1  | $\beta_1(a)$     |                       | a                                                      |

| 2  | $\beta_2(a)$     | $\beta_{1+1}(a)$      | $(\beta_1)^{2^1}\beta_1 = a^{2^2 - 1}$                 |

| 3  | $\beta_3(a)$     | $\beta_{2+1}(a)$      | $(\beta_2)^{2^1}\beta_1 = a^{2^3 - 1}$                 |

| 4  | $\beta_6(a)$     | $\beta_{3+3}(a)$      | $(\beta_3)^{2^3}\beta_3 = a^{2^6 - 1}$                 |

| 5  | $\beta_7(a)$     | $\beta_{6+1}(a)$      | $(\beta_6)^{2^1}\beta_1 = a^{2^7 - 1}$                 |

| 6  | $\beta_{14}(a)$  | $\beta_{7+7}(a)$      | $(\beta_7)^{2^7}\beta_7 = a^{2^{14}-1}$                |

| 7  | $\beta_{28}(a)$  | $\beta_{14+14}(a)$    | $(\beta_{14})^{2^{14}}\beta_{14} = a^{2^{28}-1}$       |

| 8  | $\beta_{29}(a)$  | $\beta_{28+1}(a)$     | $(\beta_{28})^{2^1}\beta_1 = a^{2^{29}-1}$             |

| 9  | $\beta_{58}(a)$  | $\beta_{29+29}(a)$    | $(\beta_{29})^{229}\beta_{29} = a^{2^{58}-1}$          |

| 10 | $\beta_{116}(a)$ | $\beta_{58+58}(a)$    | $(\beta_{58})^{258}\beta_{58} = a^{2^{116}-1}$         |

| 11 | $\beta_{232}(a)$ | $\beta_{116+116}(a)$  | $(\beta_{116})^{2^{116}}\beta_{116} = a^{2^{232} - 1}$ |

# 4.2 Quad Itoh-Tsujii Algorithm

The generic ITA discussed earlier uses squarer circuits for computation, but we can also use any  $2^n$  circuit in that place. In general, for any  $a \in GF(2^m)$ ,  $k \in \mathbb{N}$ , we define

$$\alpha_k(a) = a^{2^{nk} - 1}$$

The following properties are used to compute the inverse.

• For any element  $\mathbf{a} \in \mathrm{GF}(2^m), \ \alpha_{k_1}(a) = a^{2^{nk_1}-1} \ \mathrm{and} \ \alpha_{k_2}(a) = a^{2^{nk_2}-1} \ \mathrm{then}$

$$\alpha_{k_1+k_2}(a) = (\alpha_{k_1}(a))^{2^{n^{k_2}}} \alpha_{k_2}(a)$$

where  $k_1$ ,  $k_2$  and  $n \in \mathbb{N}$

• For any element  $a \in GF(2^m)$ , its inverse is given by

$$a^{-1} = \begin{cases} [\alpha_{\frac{m-1}{n}}(a)]^2 & \text{when } n | (m-1) \\ [(\alpha_q(a))^{2^r} \beta_r(a)]^2 & \text{when } n \nmid (m-1) \end{cases}$$

where nq + r = m - 1 and n, q and  $r \in \mathbb{N}$ .

In Quad ITA, we set n=2, such that  $\alpha_k(a)=a^{4^k-1}$ . Now to compute the inverse of any element  $a\in GF(2^{233})$ , we need to compute  $[\alpha_{\frac{233-1}{2}}(a)]^2=[\alpha_{116}(a)]^2$  (by property mentioned above).

The computation of  $[\alpha_{116}(a)]$  is given in Table 4.2. Squaring this would result in the final inverse. The algorithm to compute this is also given below in Algorithm 4.1.

Table 4.2: Quad-Itoh Tsujii for  $GF(2^{233})$

|    | $\alpha_{ui}$ (a) | $\alpha_{u_j+u_k}$ (a) | Exponentiation                                       |

|----|-------------------|------------------------|------------------------------------------------------|

| 1  | $\alpha_1(a)$     |                        | $a^3$                                                |

| 2  | $\alpha_2(a)$     | $\alpha_{1+1}(a)$      | $(\alpha_1)^{4^1}\alpha_1 = a^{4^2 - 1}$             |

| 3  | $\alpha_3(a)$     | $\alpha_{2+1}(a)$      | $(\alpha_2)^{4^1}\alpha_1 = a^{4^3 - 1}$             |

| 4  | $\alpha_6(a)$     | $\alpha_{3+3}(a)$      | $(\alpha_3)^{4^3}\alpha_3 = a^{4^6 - 1}$             |

| 5  | $\alpha_7(a)$     | $\alpha_{6+1}(a)$      | $(\alpha_6)^{4^1}\alpha_1 = a^{4^7 - 1}$             |

| 6  | $\alpha_{14}(a)$  | $\alpha_{7+7}(a)$      | $(\alpha_7)^{47}\alpha_7 = a^{4^{14}-1}$             |

| 7  | $\alpha_{28}(a)$  | $\alpha_{14+14}(a)$    | $(\alpha_{14})^{414} \ \alpha_{14} = a^{4^{28} - 1}$ |

| 8  | $\alpha_{29}(a)$  | $\alpha_{28+1}(a)$     | $(\alpha_{28})^{4^1}\alpha_1 = a^{4^{29}-1}$         |

| 9  | $\alpha_{58}(a)$  | $\alpha_{29+29}(a)$    | $(\alpha_{29})^{429}\alpha_{29} = a^{4^{58}-1}$      |

| 10 | $\alpha_{116}(a)$ | $\alpha_{58+58}(a)$    | $(\alpha_{58})^{458}\alpha_{58} = a^{4^{116}-1}$     |

In general, for l length addition chain Quad-ITA would require (l-1) multiplications and 2 multiplications for precomputation. Therefore, a total of l+1 multiplications and  $\lfloor \frac{m-1}{2} - 1 \rfloor$  quad operations are required to compute inverse.

#### **Algorithm 4.1:** qitmia (*Quad-ITA*)

```

Input: The element a \in GF(2^m) and the Brauer chain

U = \{1, 2, \ldots, \frac{m-1}{2}, m-1\}

Output: The multiplicative inverse a^{-1}

begin

l = length (U)

2

a^2 = hmul(a, a);

/* hmul : Hybrid Karatsuba multiplier */

3

\alpha_{u_1} = a^3 = a^2. a

4

\textbf{for each} \ \mathit{u_i} \in U \ (2 \leq i \leq l\text{--}1) \ \ \textbf{do}

5

6

p = u_{i-1}

q = u_i - u_{i-1}

7

\alpha_{u_i} = \text{hmul} (\alpha_p^{4^q}, \alpha_q)

8

end

9

\alpha^{-1} = \text{hmul} \left( \alpha_{u_{i-1}}, \alpha_{u_{i-1}} \right)

10

end

11

```

Mukhopadhyay and Chakraborty (2014)

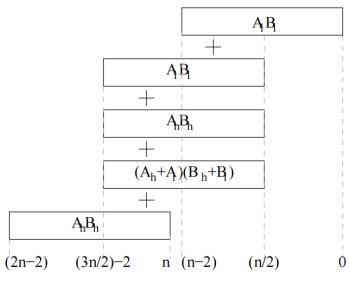

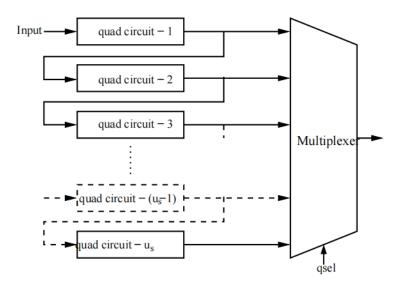

# 4.3 Quad Block

The Hardware architecture for Quad block is as shown in Fig. 4.1. The quad circuits are cascaded and the individual quad circuit outputs are connected to the multiplexer inputs. The *qsel* decides which of the 14 powers gets selected as output. The number of cascades id decided such that the delay of all the cascades can be at max equal to that of Karatsuba multiplier.

Let  $(Delay)_q$  be the delay of one quad circuit and let us consider  $u_s$  number of such cascades. Let  $(Delay)_m$  be the multiplier delay. Then,

$$(Delay)_a.u_s < (Delay)_m$$

Fig. 4.1: Quad block Rebeiro (2009)

Each quad circuit is as simpler as squarer circuit discussed before. Here, the input to is spread out by inserting three zeros in between adjacent bits which would result in the output  $\notin GF(2^{233})$ .

Therefore, to get the result in  $GF(2^{233})$  modular reduction needs to be performed on the result obtained after inserting zeros.

## **CHAPTER 5**

# **Elliptic Curve Crypto Processor**

The basis for any cryptography application involving elliptic curves is the *Scalar/Point multiplication*. So, the main purpose of this work is to design a hardware which computes that. The elliptic curve is chosen from the National Institute of Standards and Technology (1994) standard curves over  $GF(2^{233})$ .

$$y^2 + xy = x^3 + ax^2 + b ag{5.1}$$

The same can be represented in LD coordinate system as follows.

$$Y^2 + XYZ = X^3 + aX^2Z^2 + bZ^4 (5.2)$$

The Algorithm 2.1 discussed earlier is implemented in this Processor using the primitive operations such as point doubling, point addition.

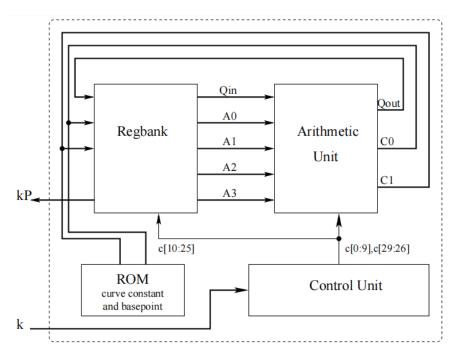

Fig. 5.1: Elliptic Curve Crypto Processor Rebeiro (2009)

The block diagram of the processor is shown in Fig. 5.1. It takes key, k and basepoint, P as the inputs and produces kP as the output after performing scalar multiplication. The elliptic curve constants such as x and y coordinates of *basepoint*, P and constant, b are stored in ROM. At every clock cycle, control signals are generated which determine the following:

- Data that should be fed to Arithmetic unit (AU).

- Computation that should be performed by the AU on the data it received.

- AU results to be stored in which registers.

# 5.1 Blocks of Cryptoprocessor

## 5.1.1 Register Bank

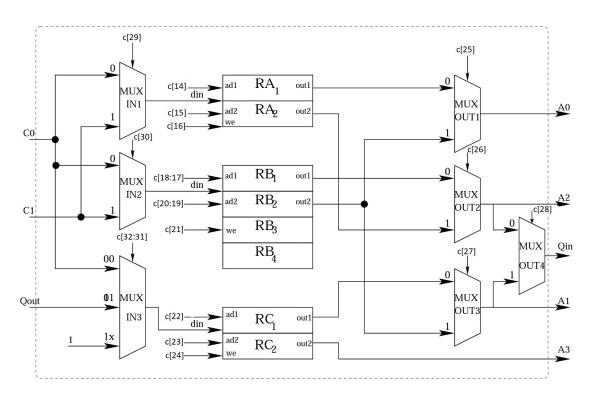

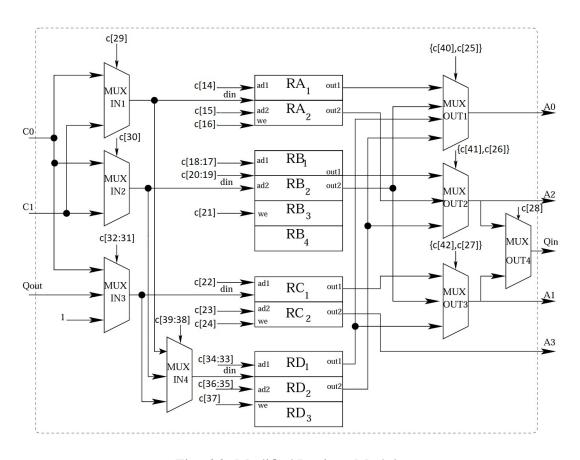

Fig. 5.2: Register File for Elliptic Curve Crypto Processor

The register bank can be divided into three banks, bank A, bank B, and bank C as shown in above Fig. 5.2. Since, this processor is designed to implement ECC algorithm for

233 bits, all the eight registers are of 233 bits size.

**Reading**: Each register is a dual ported which can facilitate *asynchronous* read. The values on *out1* and *out2* correspond to the addresses on *ad1* and *ad2*.

**Writing**: A value *din* can be written into register only if *we* signal is high. The address line *ad1* decides which register gets written.

At every clock cycle, this register module gives out five values A0, A1, A2, A3, Qin depending on the select lines of out multiplexers. It also takes three inputs from Arithmetic unit which are then passed on for updation of registers based on select lines of input multiplexers.

Table 5.1 describes the role of each register.

Table 5.1: Role of Registers

| Register | Description                                      |  |

|----------|--------------------------------------------------|--|

| $RA_1$   | 1. Initially to store $P_x$ .                    |  |

|          | 2. Stores the x coordinate of the result.        |  |

|          | 3. Intermediate result storage.                  |  |

| $RA_2$   | Stores $P_x$                                     |  |

| $RB_1$   | 1. Initially to store $P_y$ .                    |  |

|          | 2. Stores the y coordinate of the result.        |  |

|          | 3. Intermediate result storage.                  |  |

| $RB_2$   | Stores $P_y$                                     |  |

| $RB_3$   | Intermediate result storage.                     |  |

| $RB_4$   | Stores the curve constant b.                     |  |

| $RC_1$   | 1. Initialised to 1.                             |  |

|          | 2. Stores z coordinate of the projective result. |  |

|          | 3. Intermediate result storage.                  |  |

| $RC_2$   | Intermediate result storage.                     |  |

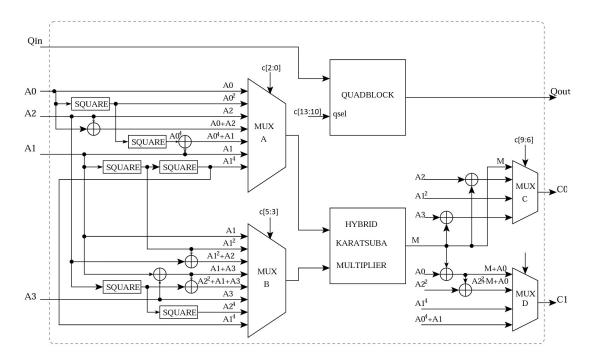

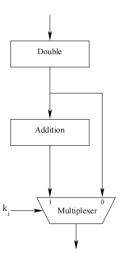

#### 5.1.2 Arithmetic Unit

It is capable of performing finite field operations discussed in previous chapters. It comprises of the following blocks:

- Squarer

- Adder: which performs bitwise XOR operation

- Hybrid Karatsuba multiplier

- Quad block: comprising of 14 cascade quad circuits as shown in Fig. 4.1.

The quad block is used only during the final conversion of result. The AU takes five inputs from the register bank and produce three results namely, C0, C1 and Qout.

Fig 5.3 shows the AU structure. Select lines of mux A and B, decide which data should be fed into Karatsuba multiplier. And the select lines of mux C and D, decide which data is output.

Fig. 5.3: Arithmetic Unit

#### 5.1.3 Control Unit

The control unit generates 33 bits control word(c) every clock cycle depending on the operation to be performed. The data flow is controlled by these control words, which also determine the operations that are done on the data. The Arithmetic unit is controlled by bits c[13:0] and the remaining bits control the reading and writing of register bank.

# **5.2** Implementing Point Arithmetic

### **5.2.1** Point Doubling

As mentioned in chapter 2, the doubling operation is performed in projective representation. The Equation 5.3 are implemented here. We need a total of five multiplications but since the value of a is 1 in our chosen elliptic curve, we need only four multiplications. As we have only one multiplier in our design and to ensure its high utilisation efficiency, we need to schedule a multiplication operation every clock cycle. Hence, we require atleast four clock cycles to finish the doubling operation. The Algorithm 5.1 depicts this implementation.

$$Z_{3} = X_{1}^{2}.Z_{1}^{2}$$

$$X_{3} = X_{1}^{4} + b.Z_{1}^{4}$$

$$Y_{3} = b.Z_{1}^{4}.Z_{3} + X_{3}.(a.Z_{3} + Y_{1}^{2} + b.Z_{1}^{4})$$

(5.3)

**Algorithm 5.1:** Implementation of Point Doubling

Input: LD Point  $P(X_1, Y_1, Z_1) \Longrightarrow (RA_1, RB_1, RC_1)$ The curve constant  $b \Longrightarrow RB_4$ .

Output: LD Point  $2P(X_3, Y_3, Z_3) \Longrightarrow (RA_1, RB_1, RC_1)$ .  $RB_3 = RB_3 \cdot RC_1^4$   $RC_1 = RA_1^2 \cdot RC_1^2$   $RA_1 = RA_1^4 \cdot RB_3$   $RB_1 = RB_3 \cdot RC_1 + RA_1 \cdot (RC_1 + RB_1^2 + RB_3)$  The operations mentioned in above algorithm can be parallelised as shown in Table 5.2. Since, AU is capable of giving out three outputs, one of these can give out multiplication result and the others can give out quad or squarer or adder results.

Table 5.2: Scheduling of Point Doubling operations

| Clock | Operation 1 (C0)                                | Operation 2 (C1)         |

|-------|-------------------------------------------------|--------------------------|

| 1     | $RC_1 = RA_1^2.RC_1^2$                          | $RB_3 = RC_1^4$          |

| 2     | $RB_3 = RB_3.RB_4$                              |                          |

| 3     | $RC_2 = (RA_1^4 + RB_3).(RC_1 + RB_1^2 + RB_3)$ | $RA_1 = (RA_1^4 + RB_3)$ |

| 4     | $RB_1 = RB_3.RC_1 + RC_2$                       |                          |

### **5.2.2** Point Addition

The following Equation 5.4 are implemented in ECCP. The equations involve point addition of two points, among which one is in affine coordinate and the other in projective coordinate system.

$$A = y_2 \cdot Z_1^2 + Y_1$$

$$B = x_2 \cdot Z_1 + X_1$$

$$C = Z_1 \cdot B$$

$$D = B^2 \cdot (C + a \cdot Z_1^2)$$

$$Z_3 = C^2$$

$$E = A \cdot C$$

$$X_3 = A^2 + D + E$$

$$F = X_3 + x_2 \cdot Z_3$$

$$G = (x_2 + y_2) \cdot Z_3^2$$

$$Y_3 = (E + Z_3) \cdot F + G$$

(5.4)

#### **Algorithm 5.2:** Implementation of Point Addition

**Input:** LD point

$$P(X_1, Y_1, Z_1) \Longrightarrow (RA_1, RB_1, RC_1)$$

.

Affine point  $Q(x_2, y_2) \Longrightarrow (RA_2, RB_2)$ .

Output: LD Point P+Q= $(X_3, Y_3, Z_3) \Longrightarrow (RA_1, RB_1, RC_1)$ .

$$1 RB_1 = RB_2.RC_1^2 + RB_1$$

$$2 \qquad RA_1 = RA_2.RC_1 + RA_1$$

$$3 RB_3 = RC_1.RA_1$$

$$4 RA_1 = RA_1^2 . (RB_3 + RC_1^2)$$

$$RC_1 = RB_3^2$$

$$6 RC_2 = RB_1.RB_3$$

$$7 RA_1 = RB_1^2 + RA_1 + RC_2$$

$$RB_3 = RA_1 + RA_2 \cdot RC_1^2$$

9

$$RB_1 = (RA_2 + RB_2).RC_1^2$$

10

$$RB_1 = (RC_2 + RC_1).RB_3 + RB_1$$

The Algorithm 5.2 depicts the implementation of point addition. The total number of multiplications involved according to Equation 5.4 are nine, but since *a* is 1 we need only eight multiplication operations. And these are scheduled in eight clock cycles. Similar to point doubling, operations in addition algorithm can also be parallelised as shown in Table 5.3.

Table 5.3: Parallel LD Point Additionon the ECCP

| Clock | Operation 1 (C0)                      | Operation 2 (C1)                      |

|-------|---------------------------------------|---------------------------------------|

| 1     | $RB_1 = RB_2 \cdot RC_1^2 + RB_1$     | -                                     |

| 2     | $RA_1 = RA_2.RC_1 + RA_1$             | -                                     |

| 3     | $RB_3 = RC_1.RA_1$                    | -                                     |

| 4     | $RA_1 = RA_1^2 \cdot (RB_3 + RC_1^2)$ | -                                     |

| 5     | $RC_2 = RB_1.RB_3$                    | $RA_1 = RB_1^2 + RA_1 + RB_1.RB_3$    |

| 6     | $RC_1 = RB_3^2$                       | $RB_3 = RA_1 + RA_2 \cdot RB_3^{\ 2}$ |

| 7     | $RB_1 = (RA_2 + RB_2).RC_1^{\ 2}$     | -                                     |

| 8     | $RB_1 = (RC_2 + RC_1).RB_3 + RB_1$    | -                                     |

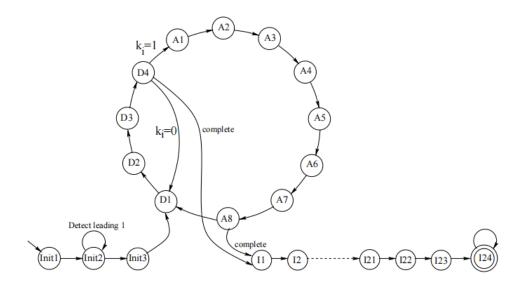

### **5.3** Finite State Machine

The ECCP involves the following steps:

- *Initialisation*: In this state, the curve constants such as x & y coordinates of base point and constant b are stored in registers. This operation takes three clock cycles depicted by three different states. Also, the position of leading '1' in the scalar key is found out.

- *Point Double*: We need four clock cycles for this operation, which are shown as four states in Fig. 5.4.

- *Point Addition*: This operation require eight clock cycles for computation and hence shown using eight different states.

- *Inversion*: Final scalar multiplication result is obtained in LD coordinates and to get back the result in affine coordinate we need this operation. This involves 24 clock cycles in total.

Once the initialisation is done, the scalar multiplication algorithm starts with state D1. Once the state D4 is reached, the current bit of key,  $k_i$  is checked.

If its 1 then the next state would be A1 else D1. This flow is continued until the last bit of key is reached. If last bit is 0 then after D4 the next state would be inversion I1. If the last bit is 1 after completing the addition the next state would be I1.

Fig. 5.4: FSM for ECCP Rebeiro (2009)

Consider the following example to know how to compute the number of clock cycles required.

Let scalar key, k = 8'b00101001.

The leading '1' is found at position i = 5. Hence the algorithm starts from i = 4. There are five bits after the leading one. And for each bit doubling is performed. There are only two 1's so the addition states are traversed twice. 3 clock cycles for initialisation and 24 clock cycles at the end for inversion.

$$ClockCycles = 3 + 4(5) + 8(2) + 24$$

= 63 (5.5)

The register module outputs and inputs at each state of FSM are given in Table 5.4. The corresponding control words generated for these states are given in Table 5.5.

Table 5.4: Register Module Input and Outputs,[Mukhopadhyay and Chakraborty (2014)]

| State | A0     | <b>A</b> 1 | A2     | A3     | Qin    | Register Module Inputs                                             |

|-------|--------|------------|--------|--------|--------|--------------------------------------------------------------------|

| Init1 | -      | -          | -      | -      | -      | <b>C0</b> : $RA_1 = P_x$ ; <b>C1</b> : $RB_1 = P_y$ ; $RC_1 = 1$   |

| Init2 | _      | -          | -      | -      | -      | $C0:RA_2=P_x;C1:RB_2=P_y$                                          |

| Init3 | _      | -          | -      | -      | -      | $\mathbf{C1}:RB_4=b$                                               |

| D1    | $RA_1$ | $RC_1$     | -      | -      | -      | $\mathbf{C0}:RC_1=RA_1^2:RC_1^2;\mathbf{C1}:RB_3=RC_1^4$           |

| D2    | _      | $RB_4$     | $RB_3$ | -      | -      | <b>C0</b> : $RB_3 = RB_3.RB_4$                                     |

| D3    | $RA_1$ | $RB_3$     | $RB_1$ | $RC_1$ | -      | $\mathbf{C0}: RC_2 = (RA_1^4 + RB_3).(RC_1 + RB_1^2 + RB_3)$       |

|       |        |            |        |        |        | <b>C1</b> : $RA_1 = (RA_1^4 + RB_3)$                               |

| D4    | $RB_3$ | $RC_1$     |        | $RC_2$ | -      | <b>C0</b> : $RB_1 = RB_3$ . $RC_1 + RC_2$                          |

| A1    | $RB_2$ | $RC_1$     | $RB_1$ | -      | -      | $\mathbf{C0}: RB_1 = RB_2.RC_1^2 + RB_1$                           |

| A2    | $RA_1$ | $RC_1$     | $RA_2$ | -      | -      | $\mathbf{C0}: RA_1 = RA_2.RC_1 + RA_1$                             |

| A3    | $RA_1$ | -          | -      | $RC_1$ | -      | $\mathbf{C0}: RB_3 = RC_1.RA_1$                                    |

| A4    | $RA_1$ | $RC_1$     | $RB_3$ | -      | -      | $\mathbf{C0}: RA_1 = RA_1^2 \cdot (RB_3 + RC_1^2)$                 |

| A5    | $RA_1$ | $RB_3$     | $RB_1$ | -      | -      | $\mathbf{C0}:RC_2 = RB_1.RB_3$                                     |

|       |        |            |        |        |        | $\mathbf{C1}: RA_1 = RB_1^2 + RA_1 + RB_1.RB_3$                    |

| A6    | $RA_1$ | $RB_3$     | $RA_2$ | -      | -      | $\mathbf{C0}:RC_1 = RB_3^2; \mathbf{C1}:RB_3 = RA_1 + RA_2.RB_3^2$ |

| A7    | $RB_2$ | $RC_1$     | $RA_2$ | -      | -      | $\mathbf{C0}: RB_1 = (RA_2 + RB_2).RC_1^{2}$                       |

| A8    | $RB_3$ |            |        | $RC_2$ | -      | $\mathbf{C0}: RB_1 = (RC_2 + RC_1).RB_3 + RB_1$                    |

| I1    | _      | $RC_1$     | -      | -      | -      | $\mathbf{C0}: RC_1 = RC_1^2.RC_1$                                  |

| I2    | _      | $RC_1$     | -      | -      | -      | $\mathbf{C0}:RB_3 = RC_1^{\ 4} \cdot RC_1$                         |

| I3    | _      | $RC_1$     | $RB_3$ | -      | -      | $C0:RB_3 = RB_3^4 . RC_1$                                          |

| I4    | _      | -          | -      | -      | $RB_3$ | $\mathbf{Qout}: RC_2 = RB_3^3$                                     |

| I5    | _      | _          | $RB_3$ | -      | -      | $\mathbf{C0}$ : $RB_3$ = $RC_2$ . $RB_3$                           |

| I6    | _      | $RC_1$     | $RB_3$ | -      | -      | $\mathbf{C0}: RB_3 = RB_3^4 . RC_1$                                |

| I7    | _      | -          | -      | -      | $RB_3$ | $\mathbf{Qout}: RC_2 = RB_3^{\ 7}$                                 |

| I8    | -      | $RC_2$     | $RB_3$ | -      | -      | $\mathbf{C0}:RB_3=RC_2.RB_3$                                       |

| I9    | -      | -          | -      | -      | $RB_3$ | <b>Qout</b> : $RC_2 = RB_3^{-1}4$                                  |

| I10   | _      | _          | $RB_3$ | -      | -      | $\mathbf{C0}$ : $RB_3$ = $RC_2$ . $RB_3$                           |

| I11   | _      | $RC_1$     | $RB_3$ | -      | -      | $\mathbf{C0}:RB_3=RB_3^4.RC_1$                                     |

| I12   | -      | -          | -      | -      |        | $\mathbf{Qout}: RC_2 = RB_3^{-14}$                                 |

| I13   | -      | -          | -      | -      | $RC_2$ | <b>Qout</b> : $RC_2 = RC_2^{-14}$                                  |

| I14   | _      | $RC_2$     | $RB_3$ | -      | -      | $\mathbf{C0}:RB_3=RC_2{}^4.RB_3$                                   |

| I15   | _      | -          | -      | -      | $RB_3$ | $\mathbf{Qout}: RC_2 = RB_3^{-14}$                                 |

| I16   | _      | -          | -      | -      | $RC_2$ | $\mathbf{Qout}: RC_2 = RC_2^{-14}$                                 |

| I17   | _      | -          | -      | -      | $RC_2$ | $\mathbf{Qout}: RC_2 = RC_2^{-14}$                                 |

| I18   | -      | -          | -      | -      | $RC_2$ | <b>Qout</b> : $RC_2 = RC_2^{-14}$                                  |

| I19   | -      | -          | -      | -      | $RC_2$ | $\mathbf{Qout}: RC_2 = RC_2^{2}$                                   |

| I20   | _      | $RC_2$     | $RB_3$ | -      | -      | $\mathbf{C0}:RB_3=RC_2.RB_3$                                       |

| I21   | _      | $RB_3$     | -      | -      | -      | $\mathbf{C0}:RC_1=RB_3^2$                                          |

| I22   | $RA_1$ | $RC_1$     | -      | -      | -      | $\mathbf{C0}:RA_1=RA_1.RC_1$                                       |

| I23   | $RB_1$ | $RC_1$     | -      | -      | -      | $\mathbf{C0}: RB_1 = RB_1 . RC_1^2$                                |

Table 5.5: Control Words,[Mukhopadhyay and Chakraborty (2014)]

| State | Regfile MUXIN     | Regfile MUXOUT    | Regbank signals   | Quadblock         | AU Mux C and D | AU MUX A and B |

|-------|-------------------|-------------------|-------------------|-------------------|----------------|----------------|

|       | $[c_{32}:c_{29}]$ | $[c_{28}:c_{25}]$ | $[c_{24}:c_{14}]$ | $[c_{13}:c_{10}]$ | $[c_9 : c_6]$  | $[c_5:c_0]$    |

| Init1 | 1010              | 00xx              | 1x01xx001x0       | xxxx              | 0000           | 000000         |

| Init2 | 1010              | 00xx              | 0xx1xx011x1       | xxxx              | XXXX           | xxxxxx         |

| Init3 | 1x10              | xxxx              | 0xx1xx110xx       | xxxx              | XXXX           | xxxxxx         |

|       |                   |                   |                   |                   |                |                |

| D1    | 001x              | 00x0              | 1x01xx100x0       | xxxx              | 1000           | 001001         |

| D2    | 000x              | x10x              | 0xx111100xx       | xxxx              | xx00           | 000010         |

| D3    | 00x1              | 0100              | 101010001x0       | xxxx              | 1100           | 100100         |

| D4    | 000x              | 00x1              | 010110000xx       | xxxx              | xx11           | 000000         |

|       |                   |                   |                   |                   |                |                |

| A1    | 000x              | 0001              | 0x0101000xx       | xxxx              | xx01           | 001000         |

| A2    | 00x1              | 0010              | 0x00xx00110       | xxxx              | 00xx           | 000010         |

| A3    | 00xx              | 00x0              | 00x1xx100x0       | xxxx              | xx00           | 101000         |

| A4    | 00x0              | 0000              | 0100xx101x0       | xxxx              | xx00           | 010001         |

| A5    | 00x1              | 0100              | 1x1010001x0       | xxxx              | 0100           | 000010         |

| A6    | 001x              | 0100              | 1x011010010       | xxxx              | 0010           | 001010         |

| A7    | 000x              | 0011              | 0x01010001x       | xxxx              | xx00           | 001011         |

| A8    | 000x              | 0001              | 010110000xx       | xxxx              | xx01           | 011000         |

|       |                   |                   |                   |                   |                |                |

| I1    | 00xx              | 00xx              | 1x0xxxxx0xx       | xxxx              | xx00           | 001101         |

| I2    | 000x              | 000x              | 0x01xx100xx       | xxxx              | xx00           | 000110         |

| I3    | 000x              | 000x              | xx01xx100xx       | xxxx              | xx00           | 110101         |

| I4    | 01xx              | 000x              | 1x10xx100xx       | 0011              | XXXX           | xxxxxx         |

| I5    | 000x              | 000x              | 0x11xx100xx       | xxxx              | xx00           | 000010         |

| I6    | 000x              | 000x              | 0x01xx100xx       | xxxx              | xx00           | 110101         |

| I7    | 01xx              | 000x              | 1x10xx100xx       | 0111              | XXXX           | xxxxxx         |

| I8    | 000x              | 00xx              | 0x11xx100xx       | xxxx              | xx00           | 000010         |

| I9    | 01xx              | 000x              | 1x10xx100xx       | 1110              | XXXX           | xxxxxx         |

| I10   | 000x              | 00xx              | 0x11xx100xx       | xxxx              | xx00           | 000010         |

| I11   | 000x              | 000x              | 0x01xx100xx       | xxxx              | xx00           | 110101         |

| I12   | 01xx              | 000x              | 1x10xx100xx       | 1110              | XXXX           | xxxxxx         |

| I13   | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | XXXX           | xxxxxx         |

| I14   | 000x              | 000x              | 0x11xx100xx       | xxxx              | xx00           | 111010         |

| I15   | 01xx              | 000x              | 1x10xx100xx       | 1110              | XXXX           | xxxxxx         |

| I16   | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | XXXX           | xxxxxx         |

| I17   | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | XXXX           | xxxxxx         |

| I18   | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | XXXX           | xxxxxx         |

| I19   | 01xx              | 100x              | 1x10xxxx0xx       | 0010              | XXXX           | xxxxxx         |

| I20   | 000x              | 000x              | 0x11xx100xx       | xxxx              | xx00           | 000010         |

| I21   | 000x              | 010x              | 1x0010xx0xx       | xxxx              | xx10           | xxxxxx         |

| I22   | 00x0              | 00x0              | 0x00xxxx1x0       | xxxx              | xx00           | 000000         |

| I23   | 000x              | 00x1              | 0x0100xx0xx       | xxxx              | xx00           | 001000         |

| I24   | 000x              | 0000              | 0xx0xx000x0       | xxxx              | XXXX           | xxxxxx         |

## 5.4 Results

The Elliptic Curve chosen for the implementation is given below along with base-point and constants. National Institute of Standards and Technology (1994)

$$y^2 + xy = x^3 + ax^2 + b$$

where,

a = 1

$\begin{aligned} x &= 233\text{'h}06\text{ac}9\text{dfcbac}8313\text{bb}2139\text{f1bb}755\text{fef}65\text{bc}391\text{f8b}36\text{f8f8eb}7371\text{fd}558\text{b} \\ y &= 233\text{'h}1006\text{a}08\text{a}41903350678\text{e}58528\text{bebf}8a0\text{beff}867a7\text{ca}36716\text{f}7\text{e}01\text{f}81052 \end{aligned}$

b = 233'h066647ede6c332c7f8c0923bb58213b333b20e9ce4281fe115f7d8f90ad

The design was simulated using Bluespec Compiler and synthesised using Xilinx Vivado. The results for both are reported subsequently.

#### **5.4.1** BSV Simulation results

The design was implemented using BSV. The simulation results for key values 2 and  $2^{233} - 1$  are given below in Fig 5.5 and Fig 5.6 respectively.

Fig. 5.5: Simulation result for key = 2

Fig. 5.6: Simulation result for  $key = 2^{233} - 1$

We can see from the above simulation results that the number of clock cycles required to compute the scalar multiplication varies with the key value. We can conclude that this design is prone to timing attacks. This issue is addressed in next chapter and architecture is modified accordingly.

# 5.5 Synthesis Report

The implemented BSV code was converted to verilog and then synthesised using *Xilinx Vivado* software. The resources utilised by the Elliptic curve crypto processor are as shown below in Fig. 5.7.

Overall, 22296 LUTs and 1713 Flip-flops are required for this design.

```

report utilization -hierarchical

Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

Tool Version : Vivado v.2018.2 (lin64) Build 2258646 Thu Jun 14 20:02:38 MDT 2018

: Sat Jun 12 23:58:41 2021

: vinod-Dell-System-XPS-L502X running 64-bit Ubuntu 16.04.7 LTS

Date

Host

Command

: report_utilization -hierarchical

Design

: 7al00tcsg324-l

Design State : Synthesized

Utilization Design Information

Table of Contents

1. Utilization by Hierarchy

1. Utilization by Hierarchy

| Instance | Module | Total LUTs | Logic LUTs | LUTRAMs | SRLs | FFs | RAMB36 | RAMB18 | DSP48 Blocks |

```

Fig. 5.7: ECCP resource utilisation

The resources utilised by the individual blocks within this processor are discussed in following sections.

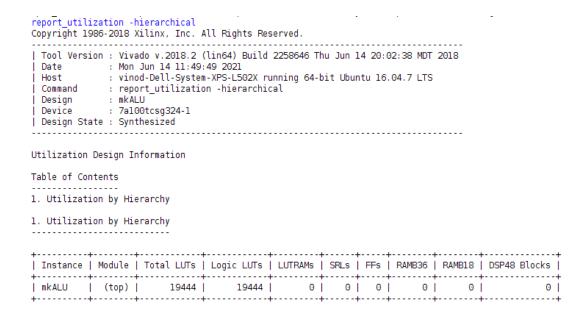

#### 5.5.1 Arithmetic Unit

The designed AU is a combinational circuit capable of giving the output within a clock cycle. However, the clock cycle is dictated by the Hybrid Karatsuba Multiplier as it has the longest latency. The overall AU consumes **19444 LUTs** for its operation. The synthesis report is shown in Fig. 5.8.

The resources utilised by constituents of AU are given below:

- Hybrid Karatsuba Multiplier consumes a total of 12804 LUTs. Its synthesis report is shown in Fig. 5.9.

- Quad block which comprises of 14 cascade quad circuits require **3505 LUTs** as shown in Fig. 5.10.

- Squarer block require **79 LUTs** for computation as shown in Fig. 5.11.

Fig. 5.8: AU resource utilisation

```

report_utilization -hierarchical

Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

| Tool Version : Vivado v.2018.2 (lin64) Build 2258646 Thu Jun 14 20:02:38 MDT 2018 |

| Date : Sat Jun 12 11:27:29 2021 |

| Host : vinod-Dell-System-XPS-L502X running 64-bit Ubuntu 16.04.7 LTS |

| Command : report_utilization -hierarchical |

| Design : mkHkmul |

| Device : 7al00tcsg324-1 |

| Design State : Synthesized |

Utilization Design Information

Table of Contents

1. Utilization by Hierarchy

1. Utilization by Hierarchy

| Instance | Module | Total LUTs | Logic LUTs | LUTRAMs | SRLs | FFs | RAMB36 | RAMB18 | DSP48 Blocks |

| mkHkmul | (top) | 12804 | 12804 | 0 | 0 | 0 | 0 | 0 | 0 |

```

Fig. 5.9: Hybrid Karatsuba Multiplier resource utilisation

Fig. 5.10: Quad block resource utilisation

Fig. 5.11: Squarer circuit resource utilisation

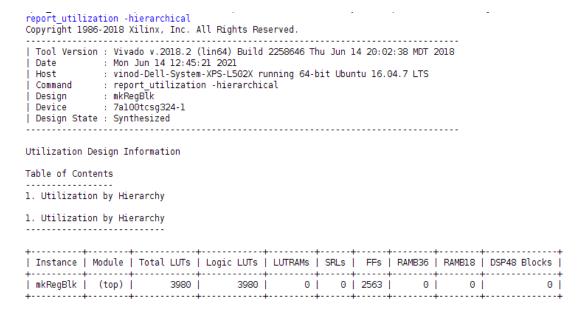

## 5.5.2 Register Module

Register module is a sequential block which has storage elements. It requires **2340 LUTs** and **1864 FFs** as shown in Fig. 5.12.

Fig. 5.12: Register module resource utilisation

## **CHAPTER 6**

### **Side Channel Attack Resistant ECCP**

Side channel attack on systems can be of many types. In this work, attack based on *sim*ple power analysis(SPA)/timing is analysed and rectified. To make our design resistant to this attack, the architecture is tweaked to result in a new version of existing processor called as SPA resistant ECCP(SR-ECCP).

# **6.1** Timing analysis

From the FSM discussed in last chapter, we can see that the changing of states depend on the key bit(0 or 1), which makes the design prone to attacks. To demonstrate this, lets consider the example for two different key values.

1. key,  $k_1$ =8'b00101001 Double states are traversed five times while addition states twice (since there are two 1's after leading MSB 1). Hence the number of clock cycles required for this key is given below.

$$ClockCycles = 3 + 4(5) + 8(2) + 24$$

= 63 (6.1)

2. key,  $k_2$ =8'b00111101 Double states are traversed five times while addition states four times (since there are four 1's after leading MSB 1). Hence the number of clock cycles required for this key is given below.

$$ClockCycles = 3 + 4(5) + 8(4) + 24$$

= 79

Therefore, we can see that in spite of the key lengths being of same size, the number of clock cycles required vary. Hence, this design is prone to timing attacks or even in terms of power consumption, as more computation is involved for  $k_i = 1$  than  $k_i = 0$ .

# 6.2 Solution for timing attack

To overcome the timing attacks, we need to make the FSM free from key bit dependency. This can be done by performing addition for every bit as doubling is done and considering the double or addition result based on the value of bit in process. For this we need to have an intermediate registers to store double result. This solution is shown pictorially in Fig 6.1.

Fig. 6.1: Always Add Method to Prevent SPA Rebeiro (2009)

The above proposed solution works only if the leading MSB '1' is at the same position. Since the left to right algorithm for scalar multiplication starts after the leading MSB '1'. To illustrate this problem consider the following example.

1. key,  $k_1$ =8'b01001001 Here the leading 1 is fount at  $6^{th}$  bit position. So the double and addition states are traversed six times. Hence the number of clock cycles required for this key is given below.

$$ClockCycles = 3 + 4(6) + 8(6) + 24$$

= 99

2. key,  $k_1$ =8'b00101001 Here the leading 1 is fount at  $5^{th}$  bit position. So the double and addition states are traversed five times. Hence the number of clock cycles required

for this key is given below.

$$ClockCycles = 3 + 4(5) + 8(5) + 24$$

= 87 (6.4)

We can see from the above example that just removing bit dependency from FSM doesn't make the design side channel resistant.

To overcome this we require dummy double and addition operations for the bits preceding the leading MSB '1'. Only initialisation of the register bank takes place when the leading 1 is being processed. Therefore, for key length l, l-1 times double and addition takes place. Thus ensuring same clock cycle requirement for all key of same size. For 8 bit key sizes,

$$ClockCycles = 3 + 4(7) + 8(7) + 24$$

= 111

irrespective of the key value the 111 clock cycles are required.

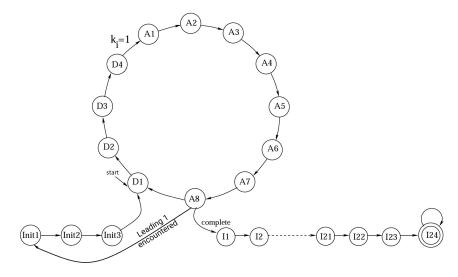

## **6.3** Modified ECCP

The above proposed solution is implemented in this modified version. To store the intermediate double result, bank D is added to the Register module. These registers store double result for every bit. When the current bit is 0, the next cycle would require the values stored in bank D, else the addition result from bank A, B and C are read. The modified bit independent FSM is shown in Fig. 6.2. Dummy double and additions are performed unless a leading '1' is detected. Once the leading '1' is detected, the state sequence is changed to Init1....Init3 for register initialisation and again back to D1. Once all bits are processed, inversion starts with the values stored in bank A, B and C if the last bit is 1 else from the values stored in bank D.

Fig. 6.2: Modified FSM Rebeiro (2009)

The modified register module is shown in Fig. 6.3 . Additional muxes are required to read and write the appropriate values into registers.

Fig. 6.3: Modified Register Module

Since additional muxes are introduced, the control words which were of 33 bits earlier, would now be of 43 bits size. The extra 10 MSB bits correspond to the additional hardware. Control words vary for each state depending on the preceding bit. If the preceding bit is 1, then we have to read from bank A, B and C. If the preceding bit is 0, then we have to read from bank D. These control words are given in Table 6.1 and 6.2.

Table 6.1: Control Words when the preceding key bit is 1

| State | Additional lines  | Regfile MUXIN     | Regfile MUXOUT    | Regbank signals   | Quadblock         | AU Mux C and D | AU MUX A and B |

|-------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------|----------------|

|       | $[c_{42}:c_{33}]$ | $[c_{32}:c_{29}]$ | $[c_{28}:c_{25}]$ | $[c_{24}:c_{14}]$ | $[c_{13}:c_{10}]$ | $[c_9:c_6]$    | $[c_5:c_0]$    |

| Init1 | xxx001xx00        | 1010              | 00xx              | 1x01xx001x0       | XXXX              | 0000           | 000000         |

| Init2 | xxx011xx01        | 1010              | 00xx              | 0xx1xx011x1       | XXXX              | xxxx           | xxxxxx         |

| Init3 | xxx101xx10        | 1x10              | XXXX              | 0xx1xx110xx       | xxxx              | xxxx           | xxxxxx         |

|       |                   |                   |                   |                   |                   |                |                |

| D1    | 0x0101xx10        | 001x              | 0010              | 1x01xx100x0       | XXXX              | 1000           | 001001         |

| D2    | 00xxx0xxxx        | 000x              | x10x              | 0xx111100xx       | xxxx              | xx00           | 000010         |

| D3    | 000001xx00        | 00x1              | 0100              | 101010001x0       | xxxx              | 1100           | 100100         |

| D4    | 000011xx01        | 000x              | 00x1              | 010110000xx       | xxxx              | xx11           | 000000         |

|       |                   |                   |                   |                   |                   |                |                |

| A1    | xxxxxxxxx         | 000x              | 0001              | 0x0101000xx       | XXXX              | xx01           | 001000         |

| A2    | xxxxxxxxx         | 00x1              | 0010              | 0x00xx00110       | xxxx              | 00xx           | 000010         |

| A3    | xxxxxxxxx         | 00xx              | 00x0              | 00x1xx100x0       | xxxx              | xx00           | 101000         |

| A4    | xxxxxxxxx         | 00x0              | 0000              | 0100xx101x0       | XXXX              | xx00           | 010001         |

| A5    | xxxxxxxxx         | 00x1              | 0100              | 1x1010001x0       | XXXX              | 0100           | 000010         |

| A6    | xxxxxxxxx         | 001x              | 0100              | 1x011010010       | xxxx              | 0010           | 001010         |

| A7    | xxxxxxxxx         | 000x              | 0011              | 0x01010001x       | xxxx              | xx00           | 001011         |

| A8    | xxxxxxxxx         | 000x              | 0001              | 010110000xx       | XXXX              | xx01           | 011000         |

|       |                   |                   |                   |                   |                   |                |                |

| I1    | 000xxxxxxx        | 00xx              | 00xx              | 1x0xxxxx0xx       | xxxx              | xx00           | 001101         |

| I2    | 000xx0xxxx        | 000x              | 000x              | 0x01xx100xx       | xxxx              | xx00           | 000110         |

| I3    | 000xx0xxxx        | 000x              | 000x              | xx01xx100xx       | xxxx              | xx00           | 110101         |

| I4    | 000xx0xxxx        | 01xx              | 000x              | 1x10xx100xx       | 0011              | xxxx           | xxxxxx         |

| I5    | 000xx0xxxx        | 000x              | 000x              | 0x11xx100xx       | xxxx              | xx00           | 000010         |

| I6    | 000xx0xxxx        | 000x              | 000x              | 0x01xx100xx       | xxxx              | xx00           | 110101         |

| I7    | 000xx0xxxx        | 01xx              | 000x              | 1x10xx100xx       | 0111              | xxxx           | xxxxxx         |

| I8    | 000xx0xxxx        | 000x              | 00xx              | 0x11xx100xx       | XXXX              | xx00           | 000010         |

| I9    | 000xx0xxxx        | 01xx              | 000x              | 1x10xx100xx       | 1110              | xxxx           | xxxxxx         |

| I10   | 000xx0xxxx        | 000x              | 00xx              | 0x11xx100xx       | XXXX              | xx00           | 000010         |

| I11   | 000xx0xxxx        | 000x              | 000x              | 0x01xx100xx       | xxxx              | xx00           | 110101         |

| I12   | 000xx0xxxx        | 01xx              | 000x              | 1x10xx100xx       | 1110              | xxxx           | xxxxxx         |

| I13   | 000xx0xxxx        | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | xxxx           | xxxxxx         |

| I14   | 000xx0xxxx        | 000x              | 000x              | 0x11xx100xx       | XXXX              | xx00           | 111010         |

| I15   | 000xx0xxxx        | 01xx              | 000x              | 1x10xx100xx       | 1110              | XXXX           | xxxxxx         |

| I16   | 000xx0xxxx        | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | xxxx           | xxxxxx         |

| I17   | 000xx0xxxx        | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | xxxx           | xxxxxx         |

| I18   | 000xx0xxxx        | 01xx              | 100x              | 1x10xxxx0xx       | 1110              | xxxx           | xxxxxx         |

| I19   | 000xx0xxxx        | 01xx              | 100x              | 1x10xxxx0xx       | 0010              | xxxx           | xxxxxx         |

| I20   | 000xx0xxxx        | 000x              | 000x              | 0x11xx100xx       | xxxx              | xx00           | 000010         |