# **ReRAM Modelling**

A THESIS

Submitted by

# L Harshit Reddy

for the award of the degree

of

# **Bachelor of Technology**

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS CHENNAI-600036

**JAN-MAY 2020**

THESIS CERTIFICATE

This is to certify that the thesis entitled "ReRAM Modelling" submitted by Lingireddy Harshit

Reddy to the Indian Institute of Technology, Madras for the award of the degree of Bachelor of

Technology is a bonafide record of research work carried out by him under our supervision. The

contents of this thesis, in full or in parts, have not been submitted to any other Institute or University

for the award of any degree or diploma.

Prof. Bhaswar Chakrabarti

Assistant Professor Department of Electrical Engineering Indian Institute of Technology Madras Chennai – 600 036. Prof. Anjan Chakravorty

Professor

Department of Electrical Engineering Indian Institute of Technology Madras Chennai – 600 036.

Place: Chennai

Date: 11<sup>th</sup> June 2020

#### **ACKNOWLEDGEMENTS**

I would like to express my deep gratitude to Professor Bhaswar Chakrabarti and Professor Anjan Chakravorty, my research guides, for their patient guidance and constructive feedback. I would also like to thank them for providing encouragement during my research project and for also holding regular meetings and providing valuable suggestions.

Finally, I wish to thank my family for supporting me during my research project.

# **TABLE OF CONTENTS**

| ACKN | IOWLEDGEMENTS                                                       | 3  |

|------|---------------------------------------------------------------------|----|

| TABL | E OF FIGURES                                                        | 5  |

| ABBR | EVIATIONS                                                           | 7  |

| СНАР | TER 1-INTRODUCTION                                                  | 8  |

| CHAP | TER 2 - LITERATURE REVIEW                                           | 9  |

| 2.1  | Introduction to ReRAM                                               | 9  |

| 2.2  | Filamentary ReRAMs                                                  | 10 |

| 2.3  | Interfacial ReRAMs                                                  | 11 |

| 2.4  | AsymmetricReRAMs                                                    | 12 |

| 2.5  | Unipolar vs BipolarReRAMs                                           |    |

| 2.6  | Advantages of ReRAM                                                 |    |

| 2.7  | GIG Devices                                                         |    |

| 2.8  | Researched Models of ReRAM                                          |    |

| 2.8. |                                                                     |    |

| 2.8. | .2 Stanford Model[9]                                                | 15 |

| 2.8. | .3 Physics Based Model[10]                                          | 15 |

| 2.8. | .4 Motivation for New Model for GIG devices                         | 15 |

| СНАР | TER 3 - MODEL-I AND SIMULATION RESULTS                              | 16 |

| 3.1  | Conductive Filaments Model                                          | 16 |

| 3.2  | Current Conduction Equations                                        | 19 |

| 3.3  | Thermal Model                                                       | 21 |

| 3.4  | Simulation Results and Motivation from Single to Multiple Filaments | 22 |

| СНАР | TER 4 - MODEL-II AND SIMULATION RESULTS                             | 28 |

| 4.1  | Conductive Filaments Model                                          | 28 |

| 4.2  | Current Conduction Model                                            | 29 |

| 4.3  | Thermal Model                                                       | 30 |

| 4.4  | Simulation Results                                                  | 31 |

| CHAP | PTER 5 – ASYMMETRY IN DEVICE                                        | 35 |

| 5.1  | Asymmetry in Device                                                 | 35 |

| 5.2  | Reason for Asymmetry                                                | 35 |

| 5.3  | Modelling of Asymmetry                                              | 38 |

| СНАР | TER 6 – CONCLUSIONS AND FUTURE WORKS                                | 39 |

| 6.1  | Conclusions                                                         | 39 |

| 6.2  | Future Works to improve the Models                                  | 39 |

| REFE | RENCES                                                              | 40 |

# **TABLE OF FIGURES**

| FIGURE 1: A) STRUCTURE OF RERAM B) IV CHARACTERISTICS OF A RERAM                 | 9          |

|----------------------------------------------------------------------------------|------------|

| FIGURE 2: ILLUSTRATION OF THE SWITCHING MECHANISM                                | 11         |

| FIGURE 3: IV CHARACTERISTICS OF AN ASYMMETRIC RERAM                              | 12         |

| FIGURE 4: UNIPOLAR AND BIPOLAR RERAM                                             | 13         |

| FIGURE 5: COMPARISION OF RRAM WITH OTHER NVM DEVICES.                            | 13         |

| FIGURE 6: STRUCTURE OF GIG DEVICE                                                | 14         |

| FIGURE 8: EXPERIMENTAL DATA FOR 450NA COMPLIANCE CURRENT. NON LINEAR CU          | JRVE       |

| CAN BE SEEN IN LRS.                                                              | 16         |

| FIGURE 7: ILLUSTRATION OF CF IN A) HRS B) LRS                                    | 16         |

| FIGURE 9: ILLUSTRATION OF HOPPING OF IONS                                        | 17         |

| FIGURE 10: ELECTRICAL EQUIVALENT CIRCUIT OF THE DEVICE                           | 19         |

| FIGURE 11: ILLUSTRATION OF TAT CURRENT                                           | 20         |

| FIGURE 12: TRAP ASSISTED TUNELLING LINEAR FIT IN HRS. COMPLIANCE CURRENT =       | = 450NA 21 |

| FIGURE 13: A) THERMAL MODEL B) THERMAL CIRCUIT                                   | 22         |

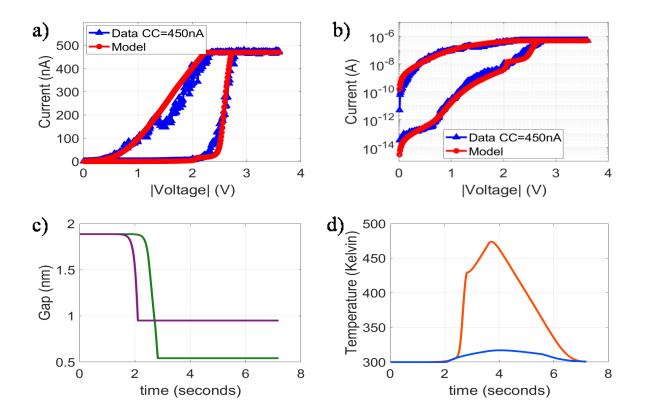

| FIGURE 14: SIMULATED RESULT FOR SET PROCESS CC = 450NA A) IV CHARACTERISTI       | CS B) LOG  |

| PLOT C) GAP LENGTH D) TEMPERATURE                                                | 22         |

| FIGURE 15:SIMULATED RESULT FOR RESET PROCESS A) IV CHARACTERISTICS B) LOC        | PLOT C)    |

| GAP LENGTH                                                                       | 23         |

| FIGURE 16: ILLUSTRATION OF TWO CONDUCTIVE FILAMENTS. HERE THE $2^{ND}$ FILAMENTS | NT (BLUE)  |

| DESTROYS A LITTLE LATER THAN THE 1ST FILAMENT (RED)                              | 24         |

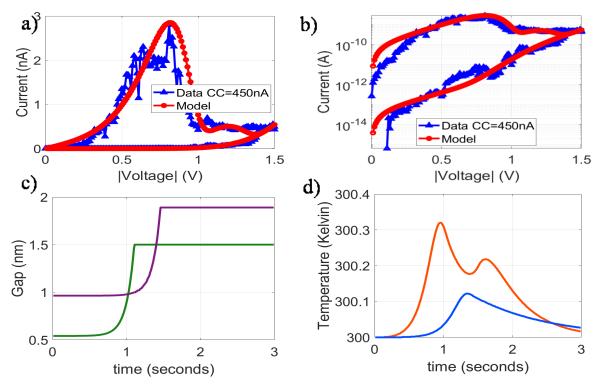

| FIGURE 17:SIMULATED RESULT FOR SET PROCESS WITH2 FILAMENTS CC = 450NA A) I       | V          |

| CHARACTERISTICS B) LOG PLOT C) GAP LENGTH D) TEMPERATURE                         | 24         |

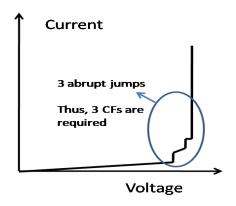

| FIGURE 19: ILLUSTRATION FOR NUMBER OF FILAMENTS TO BE USED                       | 25         |

| FIGURE 18:SIMULATED RESULT FOR RESET PROCESS WITH 2 FILAMENTS A) IV              |            |

| CHARACTERISTICS B) LOG PLOT C) GAP LENGTHS D) TEMPERATURES                       | 25         |

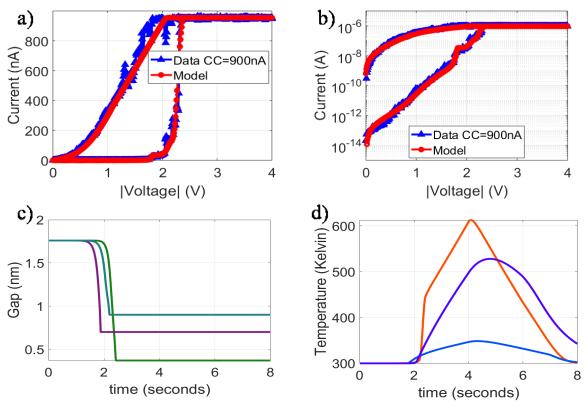

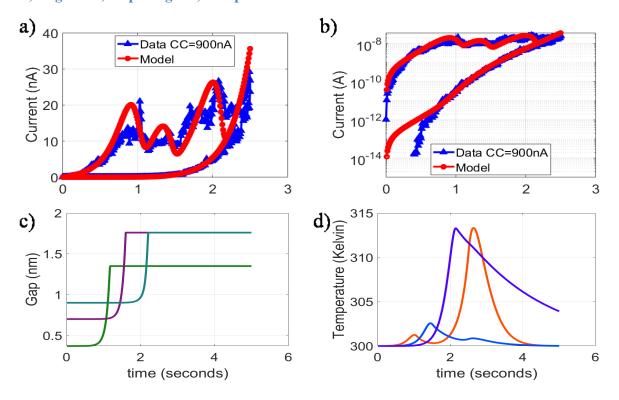

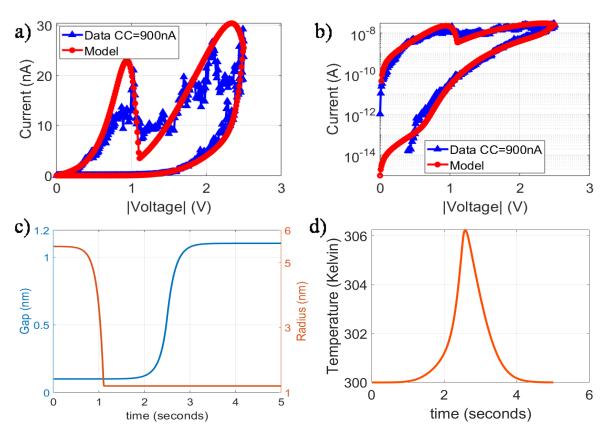

| FIGURE 20: SIMULATED RESULT FOR SET PROCESS WITH 3 FILAMENTS CC = 900NA A)       | IV         |

| CHARACTERISTICS B) LOG PLOT C) GAP LENGTH D) TEMPERATURE                         | 26         |

| FIGURE 21:SIMULATED RESULT FOR RESET PROCESS WITH 3 FILAMENTS A) IV              |            |

| CHARACTERISTICS B) LOG PLOT C) GAP LENGTHS D) TEMPERATURES                       | 26         |

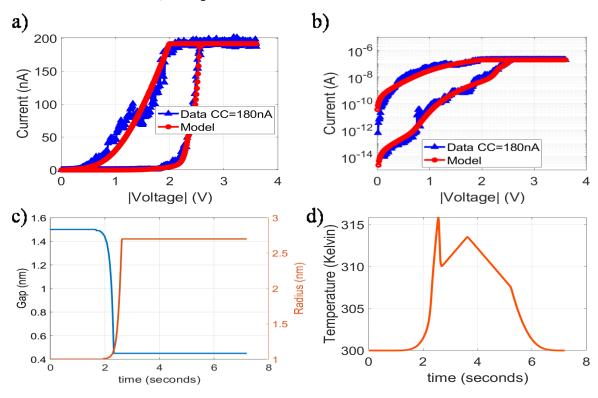

| FIGURE 22:SIMULATED RESULT FOR SET PROCESS WITH 2 FILAMENTS CC = 180NA A)        | IV         |

| CHARACTERISTICS B) LOG PLOT C) GAP LENGTH D) TEMPERATURE                         | 27         |

| FIGURE 23: SIMULATED RESULT FOR RESET PROCESS WITH 2 FILAMENTS CC = 180NA        | A) IV      |

| CHARACTERISTICS B) LOG PLOT C) GAP LENGTH D) TEMPERATURE                         | 27         |

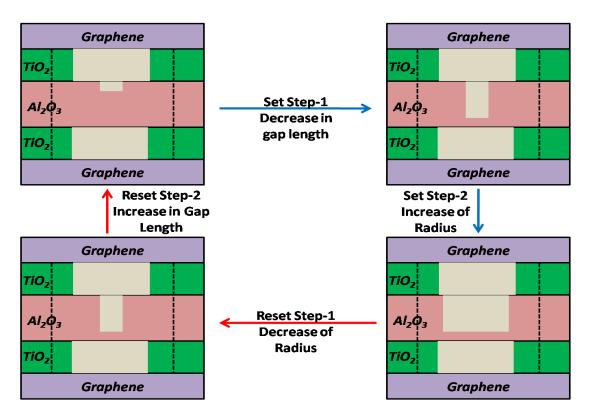

| FIGURE 24: ILLUSTRATION OF MODEL 2                                               | 28         |

| FIGURE 25: ILLUSTRATION OF 2 GAP CURRENTS                                        | 30         |

| FIGURE 26:SIMULATED RESULT FOR SET PROCESS CC = 450NA A) IV CHARACTERISTIC       | CS B) LOG  |

| PLOT C) GAP LENGTH AND RADIUS D) TEMPERATURE                                     | 31         |

| FIGURE 27: SIMULATED RESULT FOR RESET PROCESS CC = 450NA A) IV CHARACTERIS       | STICS B)   |

| LOG PLOT C) GAP LENGTH AND RADIUS D) TEMPERATURE                                 | 32         |

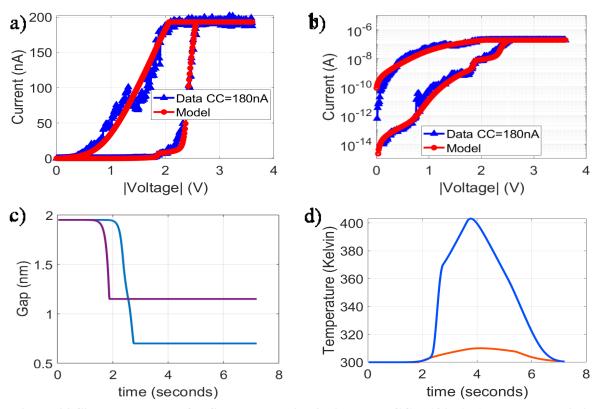

| FIGURE 28: SIMULATED RESULT FOR SET PROCESS CC = 900NA A) IV CHARACTERISTI       | CS B) LOG  |

| PLOT C) GAP LENGTH AND RADIUS D) TEMPERATURE                                     | 32         |

| FIGURE 29:SIMULATED RESULT FOR RESET PROCESS CC = 900NA A) IV CHARACTERIS        | TICS B)    |

| LOG PLOT C) GAP LENGTH AND RADIUS D) TEMPERATURE                                 | 33         |

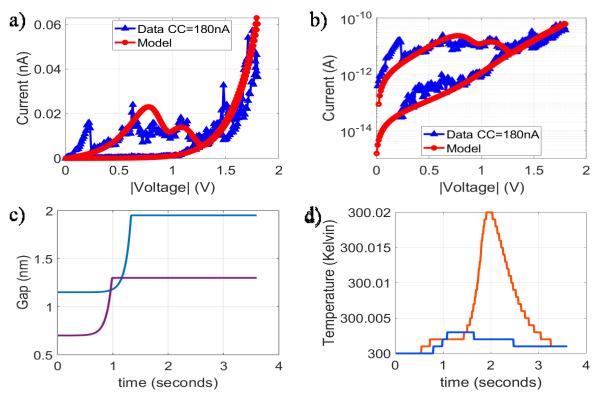

| FIGURE 30: SIMULATED RESULT FOR SET PROCESS CC = 180NA A) IV CHARACTERISTI       | CS B) LOG  |

| PLOT C) GAP LENGTH AND RADIUS D) TEMPERATURE                                     | 33         |

| FIGURE 31: SIMULATED RESULT FOR RESET PROCESS CC = 180NA A) IV CHARACTERIS       | STICS B)   |

| LOG PLOT C) GAP LENGTH AND RADIUS D) TEMPERATURE                                 | 34         |

| FIGURE 32: ILLUSTRATION OF ASYMMETRY IN DEVICE                                   | 35         |

| FIGURE 33: DEVICE IN HRS                         | 36 |

|--------------------------------------------------|----|

| FIGURE 34: BAND ENERGY DIAGRAM IN ZERO-BIAS      | 36 |

| FIGURE 35: BAND ENERGY DIAGRAM IN POSITIVE BIAS  | 36 |

| FIGURE 36: DEVICE IN LRS                         | 37 |

| FIGURE 37: ENERGY BAND DIAGRAM IN RESET ON STATE | 37 |

# **ABBREVIATIONS**

ReRAM – Resitive Random Access Memory

CF – Conductive Filament

CC – Compliance Current

GIG – Graphene Insulator Graphene

$NVM-Non\ Volatile\ Memory$

TE – Top Electrode

$BE-Bottom\ Electrode$

LRS – Low Resistance State

HRS – High Resistance State

TAT – Trap Assisted Tunelling

# **CHAPTER 1-INTRODUCTION**

Resistive Random-Access Memory(ReRAM) is anemerging non-volatile memory (NVM) technology that has recently attracted widespread attention due to its potential applications in data storage as well as in-memory computational frameworks. ReRAMs have a simple metal-insulator-metal structure and can offer high switching speed (ns), high device density, multibit storage and robust endurance[1]. Due to these attractive attributes ReRAMs are being actively used in the development of hardware accelerators for next-generation neural networks.

Clearly, large-scale applications of ReRAMs necessitates development of robust compact model for such devices. This project is aimed at building a Verilog-A model of a Graphene-Insulator-Graphene (G-I-G) ReRAM device. The G-I-G ReRAM operates at ultra-low power with ~ 200 nA ON current and sub-nA OFF current. Such devices can therefore be particularly useful for neuromorphic circuits where energy cost for computation can be serious constraint. This work reports successful development of a compact model of the G-I-G ReRAMs. The model is implemented in Qucs using Verilog-A language. The developed compact model can be used to analyzequasic-DC and dynamic characteristics of the G-I-G ReRAMs. In addition, the model can be beneficial for simulation neuromorphic networks with ReRAM arrays.

Thenext chapters of this thesis are organized as follows. <u>Chapter2</u> provides details of the device structure, operating principle and different types of ReRAM devices. Chapter 2 also discusses some of the previous works on the development of compact models for ReRAM devices. <u>Chapter 3</u> and <u>4</u> deal with the development of the compact model for G-I-G ReRAM and the simulation results.

# CHAPTER 2 - LITERATURE REVIEW

#### 2.1 Introduction to ReRAM

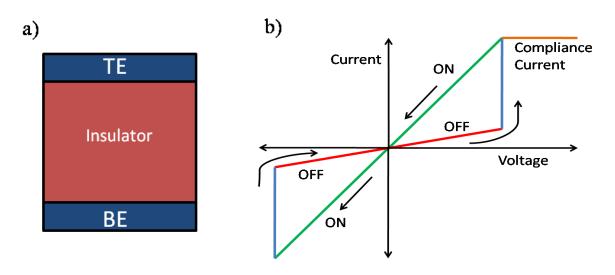

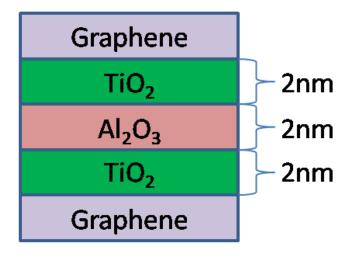

Figure 1(a) shows the cross-section of a ReRAM device. It has a simple metal-insulator-metal structure. The two metal electrodes are denoted as the top electrode (TE) and the bottom electrode (BE), respectively. A widely variety of metals have been used as electrodes. These include noble metals such as Pt and Au, transition metals such as Hf, Zr and Ti and others (such as Al). The insulating layer is typically a metal-oxide or chalcogenide thin film. The basic operating principle relies on change of resistance under electrical excitation. A ReRAM device can switch between at least two different resistance states, namely the ON (low resistance) and the OFF (high resistance) state[1]. The structure and *I-V* characteristics of a simple ReRAM device are shown in Figure 1 (b).

Figure 1: a) Structure of ReRAM b) IV characteristics of a ReRAM

The basic operation of a ReRAM is as follows. Typically, an as-fabricated device will be in the High Resistance State (HRS) or OFF state. On applying a voltage of a particular amplitude and polarity (positive in this case), the device switches from the OFF to the ON state or the Low Resistance State (LRS). The change of state from HRS to LRS is called Set process. The voltage at which the device switches to the ON state is referred to as  $V_{on}$  or  $V_{set}$ . The device can be switched to the OFF state or the HRS by applying another voltage of appropriate amplitude ( $|V_{off}|$  or  $|V_{reset}|$ ) and polarity (negative in this case). The change of state from LRS to HRS is called the Reset process. As a NVM device a ReRAM will retain its

resistance state (either LRS or HRS) until a switching voltage ( $V_{off}$  or  $V_{on}$ ) is applied to change its state. Note that intermediate resistance states between  $R_{off}$  and  $R_{on}$  can also be by appropriate programming strategies[2].

#### 2.2 Filamentary ReRAMs

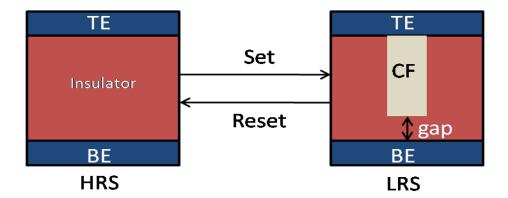

In Filamentary ReRAM devices, the switching of the device from high Resistance State (HRS) to Low Resistance State (LRS) and vice versa depends on the formation and rupture of conductive paths or filaments (CF). Conductive filaments are the high current density paths. Formation of a CF through the insulating layer is a soft dielectric-breakdown processdriven by ionic drift (underapplied electric field) and diffusion(due to concentration gradient and Joule heating). [3]During such an operation the device is protected from permanent damage by using a current compliance which limits the maximum current flow (Figure 2). Previous experimental studies indicate that such CFs typically have tapered cylindrical shapes and have a radius ranging from 0.5 nm to 5 nm. The RESET process ruptures the CF (partially), creating a tunnel barrier for the charge carriers and increasing the resistance of the device (Figure 3). The RESET process is also driven by drift-diffusion of ionic species. The device can be turned ON again by applying a positive voltage which causes the filament to regrow and close the tunneling gap. Consequently, formation of the CF through the device for the first time typically requires a higher voltage compared to the subsequent SET operations. The operation for creating the CF in a native or as-fabricated device is known as the "Forming" process[1]. It is possible to engineer a ReRAM device to become "forming-free". In such a case the voltage required for the first SET operation is the same as the subsequent V<sub>on</sub>. This can be possible if the as-fabricated device has a partially formed conductive path through the insulating layer.

Figure 2: Illustration of the Switching Mechanism

Filamentary ReRAMs can be categorized into two main groups depending on the type of ionic species that control the CF formation. Conductive bridge memories (CBRAMs) have an electrochemically active electrode (such as Ag or Cu), a solid electrolyte and an inert electrode. The CF formation is an electrochemical reaction driven by cation migration from the active electrode. In contrast, OxRAMsare driven by oxygen ion migration in a metal oxide switching layer.

The switching process in a filamentary device is typically abrupt. This is due to the fact that the drift-diffusion driven ion migration, Joule heating and defect generation create a positive feedback process which generates switching processes will be abrupt. The current will have sharp jumps in the IV characteristics. This sudden jump is an important aspect to identify the filamentary type switching devices.

#### 2.3 Interfacial ReRAMs

Interfacial resistive swithing is not a local breakdown phenomenon like a filamentary process. Instead the resistance switching involves changes at the insulator/electrode interface. For example, modulation of a potential barrier at the interface can result in the change of device resistance. Such phenomenon has been extensively observed in oxide perovskites such  $SrTiO_3$  (STO).Both  $R_{on}$  and  $R_{off}$  are dependent on device area in this case as the entire interfacial area is involved in the switching event. In addition, the switching event is typically a less abrupt process in comparison to filamentary switching.

It can be noted that filamentary and interfacial resistance switching phenomena can co-exist in a ReRAM device.

#### 2.4 AsymmetricReRAMs

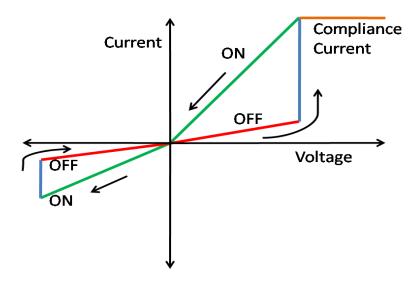

In Asymmetric ReRAM, the IV characteristics exhibit a rectifying nature like in diode. The IV characteristics of an asymmetric ReRAM is drawn in Figure 3.

Figure 3: IV characteristics of an Asymmetric ReRAM

We can see that the ON resistances in the first and the third quadrant are not the same. The reasons for asymmetric nature in ReRAMs can be because of the asymmetric structure of the device, for example, using different electrodes at top and bottom[4], [5] or because of asymmetric dielectric stacks. The other source of asymmetry is additional barriers at some specific interfaces in the device[4], [5].

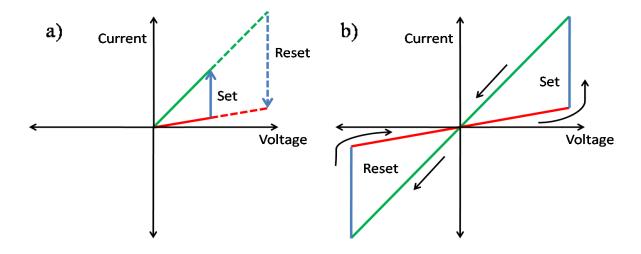

#### 2.5 Unipolar vs BipolarReRAMs

In Unipolar ReRAM, the switching depends on the amplitude of the voltage but not on the polarity[1]. Both the Set and reset operation will occur in the same quadrant, as drawn in Figure 4a. In unipolar RRAMs the filament formation/rupture process is dominated by ionic diffusion due to Joule heating. As a result the direction of the applied electric field does not play a role. In Bipolar ReRAM, the reset and set process happen in different polarity (Figure 4b) as ionic transport has contribution from both drift and diffusion phenomena.

Figure 4: Unipolar and Bipolar ReRAM

# 2.6 Advantages of ReRAM

The features of ReRAM are their low power consumption, highly scalable, 3-D integrable, and fast switching time. The high scalability of ReRAM arises from the crossbar architecture as well as nanometer size of the conductive filaments. ReRAM can also exhibit multilevel cell storage. Figure 5 shows the advantages of RRAM as an NVM device compared to other NVM devices.

|                 | FLASH     | PCM           | MRAM          | RRAM      |

|-----------------|-----------|---------------|---------------|-----------|

| Endurance       | High      | Moderate      | Very High     | High      |

| Retention       | Low       | High          | Very High     | High      |

| Fabrication     | CMOS      | New Materials | New Materials | · CMOS ·  |

| Voltage         | Very High | High          | High          | Low       |

| Power           | Moderate  | High          | Low           | Moderate  |

| Scalability     | High      | Moderate      | High          | Very High |

| Variability     | Moderate  | High          | High          | High      |

| Switching Speed | High      | Low           | Very High     | Very High |

Figure 5: Comparision of RRAM with other NVM devices. Adapted from [6]

Another central aspect of ReRAM is its use in neuromorphic computing. ReRAMscan simulate the behaviour Synapse in neurons. Synapse is a connection between two neurons for communication purposes. ReRAM, along with the leaky integrate and fire model, exhibit Spiking Time Dependent Plasticity, an essential feature in Synapse.

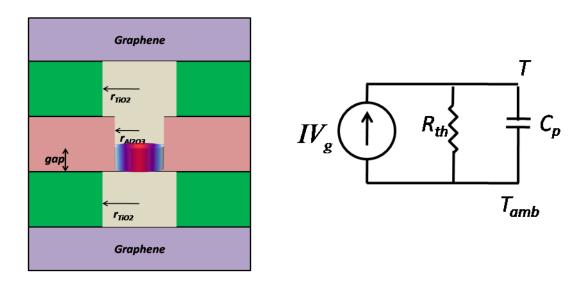

#### 2.7 GIG Devices

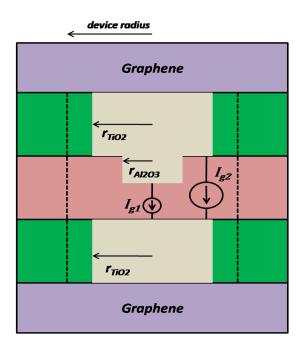

Graphene was the first 2D material to use for research in the ReRAM devices[7]. Graphene is ultrathin, which makes scaling of the devices very easy. Also, with 2D materials as electrodes, it was found that the ON/OFF ratio, the ratio of ON-state resistance to OFF state resistance, will be very high. Graphene is also a flexible material that is essential for making flexible devices. Also, because of the high out of plane resistance of Graphene, the operating current will be low, and thus the power consumption will also be low. These advantages of Graphene make it one of the actively researched 2D materials for ReRAM devices. The particular device structure as shown in Figure 6 uses a tri-layer dielectric with CVD-grown graphene as the top and bottom electrode material [8]. The device operates at extremely low compliance current of 180 nA and has sub-nA reset current. In addition, the device demonstrates non-linearity in the ON state and a "forming-free" behavior.[8].

Figure 6: Structure of GIG device

#### 2.8 Researched Models of ReRAM

#### 2.8.1 Introduction

There are many compact models designed to simulate the characteristics of ReRAM [9]–[11]. The models presented in [9]–[11] deal with Conductive Filaments, and the state variables used are gap length and radius of conductive filaments.

Gap length, g, is defined as the length from the tip of conductive filament to the bottom electrode and r is the radius of the conductive filament. Zero gap length leads to Ohmic conduction in LRS, and a small gap in the device will lead to non-linear current in the device. The conduction in the non-linear device in LRS can be tunneling or hopping or a combination of both phenomena, and in HRS also the conduction can be of various phenomena.

#### 2.8.2 Stanford Model[9]

In this model the resistive switching arises from the change in the gap length in the dielectric layer. The gap length is the only state variable for this model. The radius of Conductive Filament is constant in this model. The change in gap length is explained by the movement of oxygen ions through migration barrier and the modeling equation is based on Arrhenius Law. A 1-D thermal model is used to simulate the change in Temperature of the device. A constant thermal capacitance and thermal resistance are used for thermal circuit. A compact model is used for current in the gap which models all the different mechanisms of the current.

#### 2.8.3 Physics Based Model[10]

In this model there are two state variables, gap length and the radius which define the resistance of the device. In this model Set process occurs in two steps. In step 1,the conductive filament grows in length,i.e., the gap length reduces and in step 2 the radius of the conductive filament increases. The Reset process is one step process. During reset the length of the conductive filament decreases. The thermal model uses a constant thermal resistance and the thermal capacitance is neglected. The current through the gap is modeled by the compact equation as described in Stanford Model.

#### 2.8.4 Motivation for New Model for GIG devices

For Stanford Model and Physics based Model the ON Resistances during Set and Reset operations will be same whereas G-I-G device shows a rectifying nature which the cannot be captured by above models.

# **CHAPTER 3 - MODEL-I AND SIMULATION RESULTS**

#### 3.1 Conductive Filaments Model

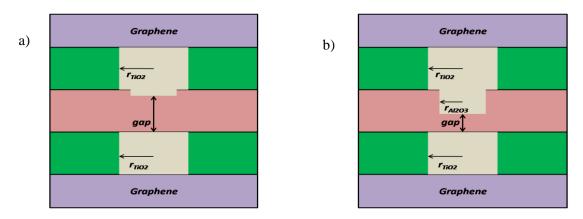

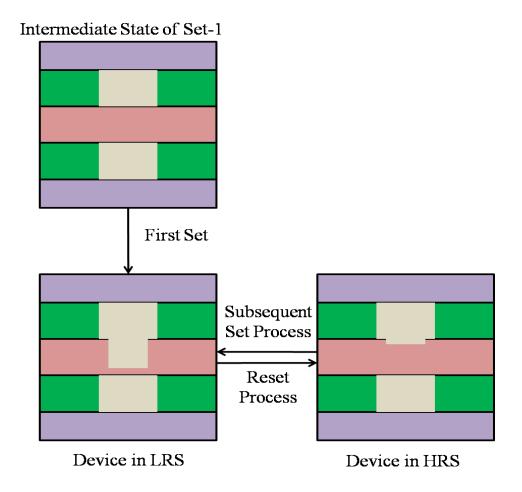

In this model, it is assumed that there will be fully grown cylindrical conductive filaments in TiO<sub>2</sub> layers in both LRS and HRS and, the conductive filament in Al<sub>2</sub>O<sub>3</sub> layers plays a crucial role in resistive switching and this layer acts as a tunnel barrier. The illustration of CF is shown in Figure 7. In both HRS and LRS, Figure 7a,b, the CFs (grey color) in TiO<sub>2</sub> layers are fully grown (no gap), and in HRS,the Al<sub>2</sub>O<sub>3</sub> layer has a small conductive filament. In LRS, Figure 7b, the length of the conductive filament in Al<sub>2</sub>O<sub>3</sub> is increased.

Figure 7: Illustration of CF in a) HRS b) LRS

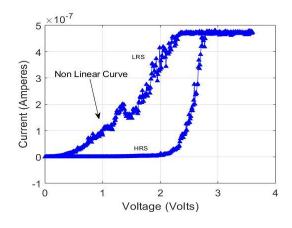

Another assumption made in this model is that the radius of conductive paths is constant. Also, in LRS, there is a gap in Al<sub>2</sub>O<sub>3</sub> instead of full-grown filament because the experiment shows current-voltage characteristics have a non-linear trend as in Figure 8, to model this non-linearity we need to have a small gap in the LRS. If there is no gap, the IV curve in LRS shows an ohmic nature as opposed to non-linear IV data.

Figure 8: Experimental Data for 450nA Compliance Current. Non Linear curve can be seen in LRS.

To model, the change in gap length the following equation is used [9]

**Equation 1: Modelling Equation for Gap change in Model 1**

$$\frac{dg}{dt} = -v_0 exp\left(\frac{-E_a}{k_b T}\right) \sinh\left(\frac{\gamma a q V_g}{L k_b T}\right)$$

$$\gamma = \gamma_0 - b\left(\frac{g}{g_{ini}}\right)^c$$

Where  $v_0$  is a velocity containing an attempt to escape frequency,  $E_a$  is the activation energy for migration of oxygen ion,  $k_b$  is Boltzmann constant, T is the current temperature of the device,  $\gamma$  is the local electric field enhancement factor, a is the hopping distance, q is the electron charge,  $V_g$  is the voltage across the gap, L is the thickness of the dielectric.  $\gamma_0$  Furthermore, b, c are fitting constants.  $g_{ini}$  is the initial gap distance.

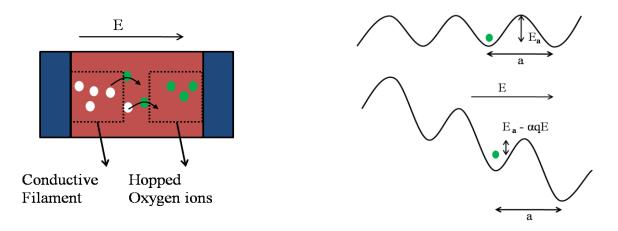

During the Set operation, when a positive voltage is applied between the TE (top electrode) and the BE (bottom electrode), the drift-diffusion of oxygen ions and generation of oxygen vacancies due to Joule heating creates a localized region rich of oxygen vacancies. The filament formation initiates at the grain-boundary regions which have higher initial concentration of defects. The oxygen ion migration reduces the gap length within the Al<sub>2</sub>O<sub>3</sub> layer as shown in Figure 9. During the reset, when a negative voltage applied between the TE and the BE, the oxygen ions occupy the vacancies created in the set process, thus increasing the gap length. Equation 1 models this change in the gap.

Equation 1 is based on the Arrhenius Law. The *sinh* term models the change in activation energy during the hopping of oxygen ion, as shown in Figure 9. It models both forward propagation and backward movement of ionswith forward hopping having a higher probability than the backward hopping.

Figure 9: Illustration of Hopping of ions

#### **Justification for the CF model in Figure 7**

The fabricated G-I-G devices demonstrate "forming-free" behavior: i.e the voltage required for the first SET process is the same as the subsequent SET operations. This indicates that the as-fabricated device has partially formed filament through the insulator. For simplicity, we assume that both the TiO<sub>2</sub> layers have conductive filament in the initial state whereas the Al<sub>2</sub>O<sub>3</sub> layer does not have any localized conductive path. During first set the filaments will form in the Al<sub>2</sub>O<sub>3</sub> layer and the device will switch to LRS. The conductive filament in Al<sub>2</sub>O<sub>3</sub> is not fully formed. This can be concluded from the non-linear experimental data in LRS, indicative of a small tunneling gap present even in LRS. In Reset process, the conductive filament in Al<sub>2</sub>O<sub>3</sub> would ruptureunder an opposite electric field. The local electric field in the gap region will be very high as most of the applied voltage appears across this gap region. This high electric field in gap region(in Al<sub>2</sub>O<sub>3</sub>) along with Joule heating will cause the recombination of oxygen ions with the vacancies formed during Set process thus rupturing of filament in Al<sub>2</sub>O<sub>3</sub> first. In subsequent Set and Reset processes it is possible that the CF in Al<sub>2</sub>O<sub>3</sub> only will formed and ruptured while CF's in TiO<sub>2</sub> would have been intact.

# 3.2 Current Conduction Equations

The conductive filaments can be modeled as resistors [10], [11]. For a conductive filament of length L, radius r and resistivity  $\rho$  its resistance is

$$R_{cf} = \frac{\rho L}{\pi r^2}$$

Arrhenius Law models the temperature dependence of resistivity[10]

$\rho = \rho_0 exp\left(\frac{E_{ac}}{k_b T}\right)$  Where Eac is the activation energy for conduction.

A compact equation models the current through the gap[9]

**Equation 2: Compact Model for Gap Current**

$$I_g = I_0 \exp\left(\frac{-g}{g_0}\right) \sinh\left(\frac{V_g}{V_0}\right)$$

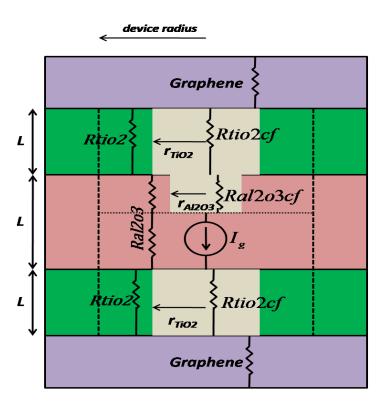

Where g is the gap length,  $V_g$  is the voltage across the gap.  $I_0$ ,  $g_0$ ,  $V_0$  are the fitting parameters. The illustration of the current conduction is shown in Figure 10.

Figure 10: Electrical Equivalent Circuit of the Device

In Figure 10, the top and bottom Graphene are modeled by a resistor each. The CFs (grey color) is also modeled by resistors with resistance values, as explained previously. A current source models the gap in parallel with the resistance of the remaining  $Al_2O_3$  dielectric.

The area within the *device radius* is considered as the working area, most of the current flow within this area. The remaining part of the dielectrics(non-CF parts) within the working area are modeled as resistors. Capacitances are neglected in this model. By rough calculations, the capacitance is in the order of  $0.01f\ F$ , hence neglected.

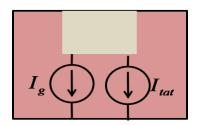

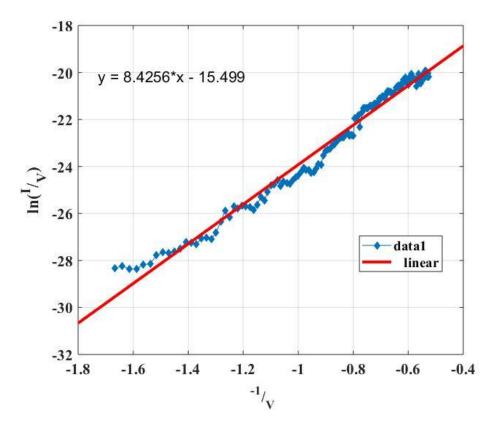

In addition to  $I_g$  through the gap, there is a Trap-Assisted Tunneling (TAT) current. Generally Equation 2 models all type of current mechanisms but in this case, we can model  $I_g$  as all currents except TAT and a TAT current separately for better results. To model the TAT current, an additional current source is added in parallel to Gap current. Illustration of this is shown in Figure 11.

Figure 11: Illustration of TAT current

TAT current is given by

**Equation 3: TAT current**

$$I_{tat} = AVexp\left(-\frac{B}{V}\right)$$

TAT current is significant in HRS (in our case) and is dominant during 0.6 V to 1.9 V and in the remaining range  $I_g$  dominates. Figure 12 shows the plot of  $\ln\left(\frac{I}{V}\right)vs-\frac{1}{V}$ . We can see that the curve is linear. A is an exponent of intercept, and B is the slope of the below plot.

Figure 12: Trap Assisted Tunelling Linear Fit in HRS. Compliance Current = 450nA

#### 3.3 Thermal Model

Resistive switching is very sensitive to temperature. From Equation 1, we can see that change in the gap is dependent on temperature. The rise in the temperature of the device is due to the Joule Heating. The temperature rise will be more in the gap in the  $Al_2O_3$  layer because since joule heating is current \* voltage and most of the voltage applied drops across gap since it is the most resistive region compared to other CFs regions. Cylindrical thermal resistance is used to model the change in temperature. The thermal model and circuit are shown in Figure 13.

**Equation 4: Thermal Equations**

$$R_{th} = \frac{length}{k_{th}Area} = \frac{gap}{k_{th}\pi r_{al2o3}^2}$$

$R_{th}C_p \frac{dT}{dt} = (T - Tamb) - IV_g R_{th}$

Figure 13: a) Thermal Model b) Thermal Circuit

Where  $k_{th}$  is the thermal conductivity of  $Al_2O_3$ , here length is the gap length, and area is the area of the cross-section of CF in  $Al_2O_3$ . Tamb is the ambient temperature of 300 Kelvin.Rth is the calculated thermal resistance.  $I * V_g$  is the power dissipated in the gap region. It is assumed that the temperature is uniform in the gap region.

# 3.4 Simulation Results and Motivation from Single to Multiple Filaments

The model is implemented in Qucs using Verilog-A language.

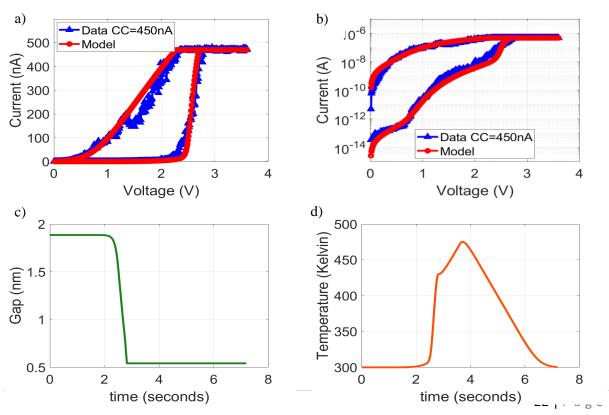

# **Set Process, Compliance Current = 450nA**

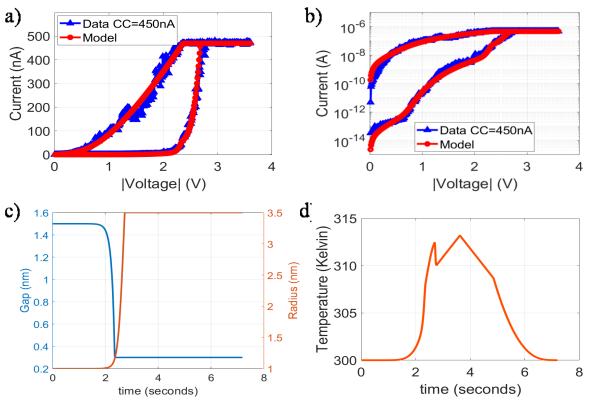

Figure 14: Simulated Result for Set Process CC = 450nA a) IV characteristics b) Log Plot c) Gap Length d) Temperature

Figure 14 shows the simulated results of the set process of the model for Compliance Current (CC) 450nA. The input voltage is a ramp varying at 1V/second. At 2 seconds,thegap starts decreasing, increasing current and joule heating and thus increasing temperature, and this results in positive feedback, which results in a sudden increase in current. The device switches from HRS to LRS at around 2.75 Volts. The temperature reaches a maximum value of 475 Kelvin. The gap length in  $Al_2O_3$  decreases from 1.9 nm to 0.54 nm.

#### **Reset Process and Motivation to Multiple Filaments**

Figure 15:Simulated Result for Reset Process a) IV characteristics b) Log Plot c) Gap Length

Figure 15 shows the simulated results of the reset process. The reset voltage is around 1 V. At 1 second, the gap starts to increase, thus decreasing the current. The gap length increases from 0.54 nm, where it ended during the set process, to 1.5 nm. During the set process, the initial gap length was 1.9 nm. Instead of increasing the gap length to 1.9 nm, 1.5 nm value was used to match the experimental data. Here, the CF does not destroy completely.

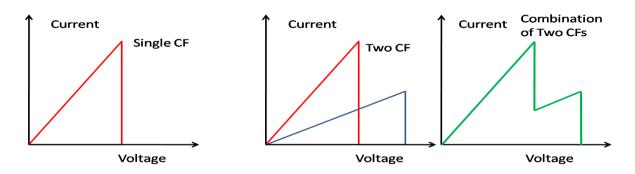

From Reset simulations, Figure 15, it can be observed that from 1 to 1.5 V in LRS, the model does not match the data. For the above simulations, we have used only one conductive filament. Using multiple conductive filaments can solve this problem. The idea is that the

other filaments may destroy at a higher voltage. Other filaments may have different physical properties that the main filament. Illustration of the use of multiple filaments is shown in Figure 16.

Figure 16: Illustration of Two Conductive Filaments. Here the 2<sup>nd</sup> filament (blue) destroys a little later than the 1<sup>st</sup> filament (red)

One precaution we should take is, since the model for the set process matches the data pretty well, we should choose the parameters of new CF such that it does not disturb our previous simulation.

# **Set and Reset Process Simulations, Compliance Current = 450nA, Multiple Filaments**

Two Conductive Filaments are used.

Figure 17:Simulated Result for Set Process with Filaments CC = 450nA a) IV characteristics b) Log Plot c) Gap Length d) Temperature

Figure 18:Simulated Result for Reset Process with 2 Filaments a) IV characteristics b) Log Plot c) Gap Lengths d) Temperatures

It is clear from Figure 18 that the model with 2 CFs matches the data better than that of 1 CF. The initial and final gap lengths are not the same. Here, also the conductive filaments are not broken completely.

#### Number of Filaments to be used

For Compliance Current 450nA 2 CFs are used based on reset data. To find the number of filaments, we can even use set data when we cannot estimate accurately with reset data. The number of abrupt jumps in the data can also give the number of filaments to be used. Illustration for the above explanation is given in Figure 19.

Figure 19: Illustration for Number of Filaments to be used

# **Set and Reset Process, Compliance Current = 900nA, Multiple Filaments**

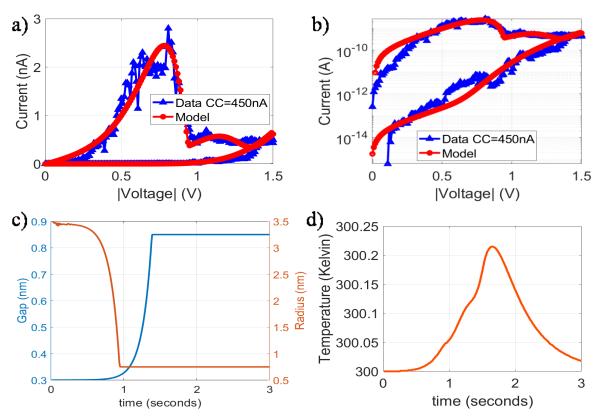

For this compliance current, it was observed from data that there are three jumps, thus using three filaments.

Figure 20: Simulated Result for Set Process with 3 Filaments CC = 900nA a) IV characteristics b) Log Plot c) Gap Length d) Temperature

Figure 21:Simulated Result for Reset Process with 3 Filaments a) IV characteristics b) Log Plot c) Gap Lengths d) Temperatures

# **Set and Reset Process, Compliance Current = 180nA, Multiple Filaments**

Figure 22:Simulated Result for Set Process with 2 Filaments CC = 180nA a) IV characteristics b) Log Plot c) Gap Length d) Temperature

Figure 23: Simulated Result for Reset Process with 2 Filaments CC = 180nA a) IV characteristics b) Log Plot c) Gap Length d) Temperature

# CHAPTER 4 - MODEL-II AND SIMULATION RESULTS

#### 4.1 Conductive Filaments Model

In this model, it is assumed that there will be fully grown cylindrical conductive filaments in  $TiO_2$  layers in both LRS and HRS and, the conductive filament in  $Al_2O_3$  layers plays a crucial role in resistive switching. The illustration of CF is shown in Figure 24. In both HRS and LRS, Figure 7a,b, the CFs (grey color) in  $TiO_2$  layers are fully grown (no gap), and in HRS, the  $Al_2O_3$  layer has a small conductive filament. In LRS, the length of conductive filament in  $Al_2O_3$  is increased, and the radius of conductive filament is also increased. This is a two-step process, as shown in Figure 24.

Figure 24: Illustration of Model 2

Initially, the device is in HRS, and the CF is small. During Step-1 of the Set process, the length of the conductive filament increases, decreasing the gap length till some minimum gap, and in step-2 of the Set process, the radius of the conductive filament increases till some maximum radius and the device is in LRS. In Reset Step-1, the radius of CF decreases, and in Step-2, the gap increases, and the device is in HRS. In this model also, there is a gap in LRS to simulate the non-linearity, as explained previously.

To model, the change in gap length the following equation is used [10], [11]

**Equation 5: Modelling Equation for Gap Change in Model 2**

$$\frac{dg}{dt} = -a * f * exp\left(\frac{-q * E_h}{k_b T}\right)$$

$$E_h = E_{h0} - \alpha ZE$$

Where a is thehopping distance, f is an attempt to escape frequency,  $E_{h0}$  is the activation energy for migration of oxygen ion under zero electric field,  $k_b$  is Boltzmann constant, T is the current temperature of the device,  $\alpha$  is the local electric field enhancement factor, Z is the charge, q is the electron charge, E is the electric field.

To model the change in radius the following equation is used [10]

**Equation 6: Modelling Equation for Radius Change in Model 2**

$$\frac{dr}{dt} = (\Delta r + \frac{\Delta r^2}{2r}) * f * exp\left(\frac{-q * E_a}{k_b T}\right)$$

$$E_a = E_{a0} - \alpha ZE$$

Where a is thehopping distance, f is an attempt to escape frequency,  $E_{a0}$  is the activation energy for the generation of oxygen ion under zero electric field,  $k_b$  is Boltzmann constant, T is the current temperature of the device,  $\alpha$  is the local electric field enhancement factor, Z is the charge, q is the electron charge, E is the electric field.  $\Delta r$  is an effective expanding radius of the filament.

#### 4.2 Current Conduction Model

The conductive filaments can be modeled as resistors, as explained in 3.2.

A compact equation models the current through the gap

**Equation 7: Compact Model for Gap Current with Area dependence**

$$I_g = I_0 * \pi r^2 * \exp\left(\frac{-g}{g_0}\right) \sinh\left(\frac{V_g}{V_0}\right)$$

Where g is the gap length,  $V_g$  is the voltage across the gap, r is theradius of the conductive filament in  $Al_2O_3$ .  $I_0$ ,  $g_0$ ,  $V_0$  are the fitting parameters. Since, in this model, the radius of the filament is not constant, we need to have area dependence in the current term. Since the filaments are cylindrical, the cross-section area will be  $\pi r^2$ . This addition of area dependence can is shown in Equation 7.

Since  $I_g$  is dependent on the area we need to consider twogap currents [10], as shown in Figure 25.

Figure 25: Illustration of 2 gap currents

The reason for two gap currents is that when the radius of CF in  $Al_2O_3$  is a minimum value, the current  $I_{g1}$  will be very small and the current  $I_{g2}$  dominates and as the radius increases the  $I_{g1}$  starts increasing and dominates  $I_{g2}$ .  $I_{g2}$  current is not negligible when the radius is small, thus cannot be neglected. The formulas for  $I_{g1}$  and  $I_{g2}$  are given below

$$\begin{split} I_{g1} &= I_0 * \pi r_{al2o3}^2 * \exp\left(\frac{-g}{g_0}\right) \sinh\left(\frac{V_g}{V_0}\right) \\ I_{g2} &= I_0 * \pi (device\ radius - r_{al2o3})^2 * \exp\left(\frac{-L}{g_0}\right) \sinh\left(\frac{V_{al2o3}}{V_0}\right) \end{split}$$

Where  $r_{al2o3}$  is the radius of CF in Al<sub>2</sub>O<sub>3</sub>, Llength of Al<sub>2</sub>O<sub>3</sub> layer and  $V_{al2o3}$  is the voltage across the Al<sub>2</sub>O<sub>3</sub>layer. The remaining parameters are explained in 3.2.

TAT current will also have area dependence

$$I_{tat} = AVexp\left(-\frac{B}{V}\right) * \pi r_{al2o3}^{2}$$

Illustration for TAT current is given in Figure 11. The constants A and B are explained in 3.2.

#### 4.3 Thermal Model

The thermal model is the same as that in model 1. Refer 3.3.

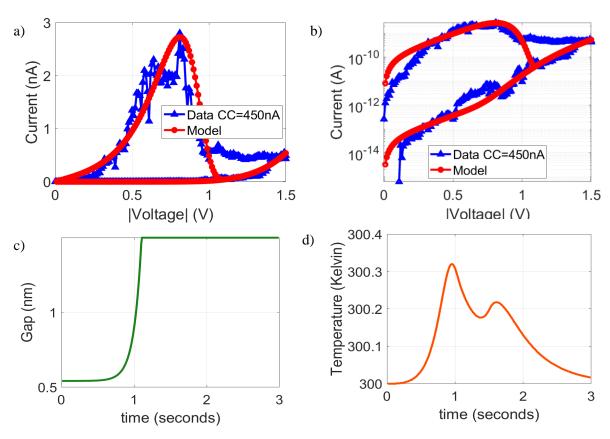

#### 4.4 Simulation Results

# **Set and Reset Process, Compliance Current = 450nA**

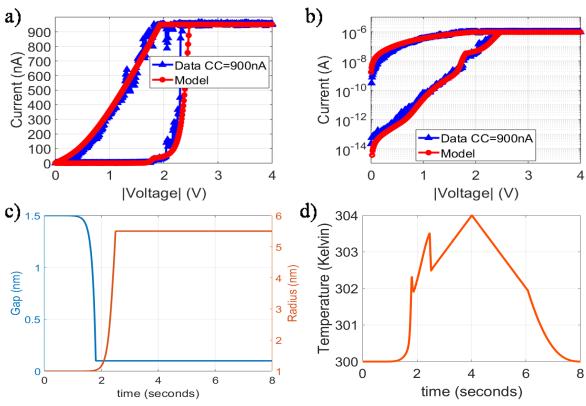

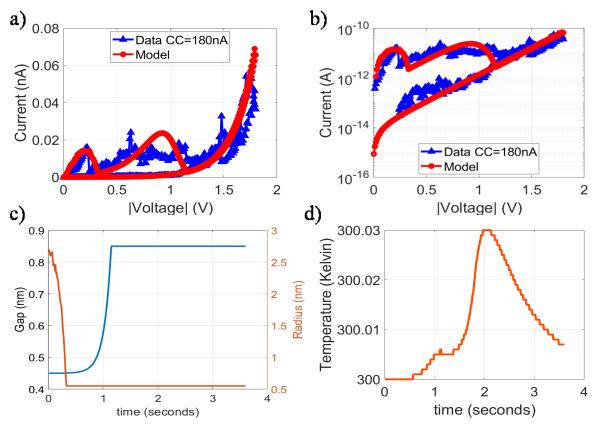

Figure 26:Simulated Result for Set Process CC = 450nA a) IV characteristics b) Log Plot c) Gap Length and Radius d) Temperature

From Figure 26c, we can see that the gap reduces first, which is step 1 in the set process, and then the radius starts to increase, step 2 of the set process. The maximum temperature is only 312.5 Kelvin this because as the radius increases, thermal resistance decreases, Equation 4. In model 1, the radius was constant, whereas, in model 2, it changes, and Rthdecreases with an increase in area, leading to less rise in temperature.

From Figure 27c, we can see that the radius of CF decreases (step 1 of the reset process), and then the gap length starts increasing (step 2 of the reset process). Here also, as in model 1, the conductive filament may not rupture completely. The final gap in the reset process is 0.85 nm, whereas the gap when the set process starts is 1.5 nm. The radius of CF at the start of the set process is 1 nm, and the radius after the reset process is 0.75 nm. In this case,theradius decreases more, and the gap does not increase much.

Figure 27: Simulated Result for Reset Process CC = 450nA a) IV characteristics b) Log Plot c) Gap Length and Radius d) Temperature

# **Set and Reset Process, Compliance Current = 900nA**

Figure 28: Simulated Result for Set Process CC = 900nA a) IV characteristics b) Log Plot c) Gap Length and Radius d) Temperature

Figure 29:Simulated Result for Reset Process CC = 900nA a) IV characteristics b) Log Plot c) Gap Length and Radius d) Temperature

# **Set and Reset Process, Compliance Current = 180nA**

Figure 30: Simulated Result for Set Process CC = 180nA a) IV characteristics b) Log Plot c) Gap Length and Radius d) Temperature

Figure 31: Simulated Result for Reset Process CC = 180nA a) IV characteristics b) Log Plot c) Gap Length and Radius d) Temperature

# CHAPTER 5 – ASYMMETRY IN DEVICE

# 5.1 Asymmetry in Device

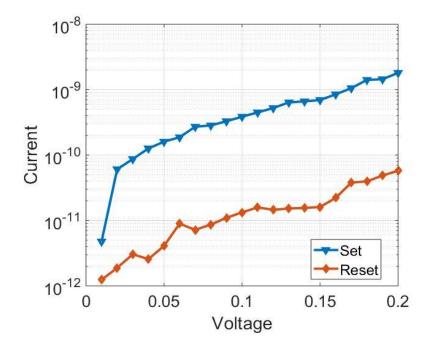

For the GIG device, we are interested in modeling, from the experimental data, it is observed that the device shows rectifying property or asymmetric property. The asymmetry is in the ON state, as described in 2.4. Figure 32: Illustration of Asymmetry in Deviceshows the ON current during positive bias, i.e., during the set process and during negative bias, i.e., during the reset process. We can see that the current in the Set process is higher than that in the Reset process. For 450nA, the ON current in the Set process was roughly 30 times higher than in the Reset process.

Figure 32: Illustration of Asymmetry in Device

# 5.2 Reason for Asymmetry

# **Set Process**

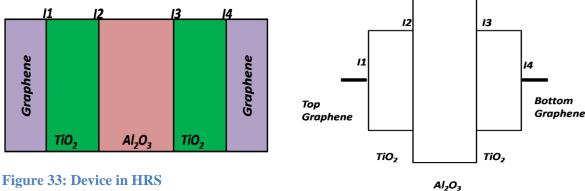

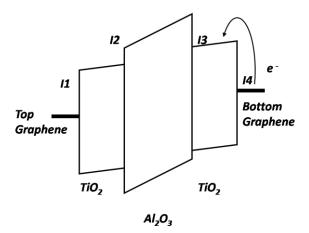

Initially, the device will be in High Resistance State (HRS), i.e., no CF, as shown in Figure 33. The zero-bias band energy diagram is shown in Figure 34.

11, I2, I3, I4 in Figure 33are the interfaces between top Graphene and top TiO<sub>2</sub>; top TiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>; Al<sub>2</sub>O<sub>3</sub> and bottom TiO<sub>2</sub>; and bottom TiO<sub>2</sub> and Graphene respectively.

Figure 34: Band Energy Diagram in Zero-Bias

In HRS state as voltage increases, the current conduction mechanism will be mainly because of Schottky Emission. With positive voltage applied to Top Graphene, the movement of the electrons will be from bottom Graphene to top Graphene, and these electrons will experience a Schottky barrier at the I4 interface as shown in Figure 35. Let the SB height be  $\phi_{b, off, set}$ .

Along with the Schottky current, there will also be Trap-Assisted-Tunneling current (TAT) because of the defects in the dielectrics.

Figure 35: Band Energy Diagram in Positive Bias

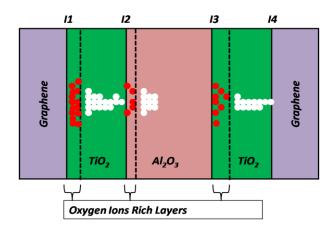

As we keep increasing the voltage applied across the device, the oxygen ions with a negative charge in all three dielectrics, namely Top TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and bottom TiO<sub>2</sub>, will drift towards the positive terminal and leave behind the vacancies thus, forming CFs in the dielectric layers as shown in Figure 36. The I4 interface will become more metallic or conductive due to CF formation. The I1, I2, I3 interfaces will now become rich in oxygen ions. I1 interface would

be more abundant in oxygen ions because of the positive terminal. Thus in LRS, the current is a combination of Ohms Law and Schottky Emission with Schottky barrier height less than that in HRS. Let the SB height be  $\phi_{b, \, on, \, set}$ .

Figure 36: Device in LRS

#### **Reset Process**

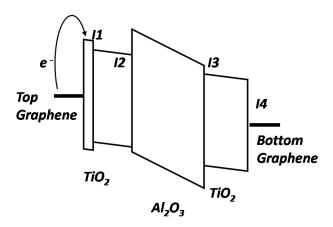

In the reset process, a negative voltage is applied across the top and bottom Graphenes. The current flows from bottom Graphene to top Graphene, i.e., electrons flow from top Graphene to bottom Graphene. These electrons will experience interface I1. Since interface I1 is more abundant in oxygen ions, the I1 interface layer is closer to stoichiometric  $TiO_2$ . Thus, the Schottky barrier is higher for the electrons when they move from top Graphene to bottom Graphene than that of electrons when they move from bottom Graphene to top Graphene as in ON state of the Set process As shown in Figure 37. Let the SB height be  $\phi_{b, \text{ on, reset}}$ .

Figure 37: Energy Band Diagram in Reset ON State

As negative voltage keeps on increasing the oxygen ions in the interfaces, move into the bulk of dielectrics. Then they will recombine with the oxygen vacancies, and the conductive

filaments are destroyed, and also the interface comes to its original state, and the device is switched to HRS. Let the SB height be  $\phi_{b, off, reset}$ .

$\phi_{b, \, off, \, reset}$  may not be the same as  $\phi_{b, \, off, \, set}$  if some part of CF remains intact.

# **5.3** Modelling of Asymmetry

Since the current is approximately 30 times lower in reset than in the Set and this factor is almost constant in the desired voltage range, thus we can model the asymmetric property by decreasing I<sub>0</sub>in Equation 2by 30 times during reset process. This is the most straightforward way to include asymmetricity in the device. All the above-shown results are simulated by including this asymmetricity.

#### **Comparison of Models**

Model 1 with multiple conductive filaments seems to be more practical to GIG device. This conclusion is drawn based on the maximum temperature of the device. The maximum temperature for model-1 with CC = 450nA is around 475 Kelvin whereas for model 2 the maximum temperature is around 313 Kelvin only. Generally, for filamentary devices a significant increase in temperature is observed which is the basis for positive feedback in the device.

# CHAPTER 6 – CONCLUSIONS AND FUTURE WORKS

#### 6.1 Conclusions

The compact models for G-I-G ReRAM are developed. These models are developed based on the evolution of conductive filaments. In Model-1 only the gap of the conductive filament changes whereas the radius of the conductive filament is kept constant. Multiple conductive filaments in Model 1 are used for better modelling of the GIG device.

In Model-2 the switching of the state of the device from HRS to LRS or vice versa is a two step process. In Model-2 both the radius and gap length of the conductive filaments play a important role in the resistive switching.

The asymmetry in the device is explained based on the additional Schottky barriers due to the formation of oxygen rich layers. The above models reproduce the quasi DC characteristics of the GIG device pretty well for different compliance currents. These compact models which have very low power consumption and operating current can be used for future simulations of Neuromorphic circuits.

# **6.2** Future Works to improve the Models

- The simulated reset process of Model 1 with single filament is abrupt. The reset switching curve can be made gradual either by improving thermal model or by changing the parameters in Equation 1. The parameters *b,c* in local electrical field enhancement factormay play a key role in nature of reset curve since electrical field enhancement factor is a strong function gap.

- To include asymmetricity the parameter  $I_0$  was changed manually in reset process. To improve the model,  $I_0$  can be a linear/non-linear function of gap length or temperature.

- Instead of using compact model for current (Equation 2), Schottky's Emission current model can be used. The main parameters will be Schottky Barrier heights namely,  $\phi_b$ , off, set,  $\phi_b$ , on, set,  $\phi_b$ , on, reset, and  $\phi_b$ , off, reset as explained in 5.2. The barrier height can be a linear/non-linear functions of gap length.

#### **REFERENCES**

- [1] H.-S. P. Wong *et al.*, "Metal–Oxide RRAM," *Proc. IEEE*, vol. 100, no. 6, pp. 1951–1970, Jun. 2012, doi: 10.1109/JPROC.2012.2190369.

- [2] H. Y. Lee *et al.*, "Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2 based RRAM," in *2008 IEEE International Electron Devices Meeting*, San Francisco, CA, USA, Dec. 2008, pp. 1–4, doi: 10.1109/IEDM.2008.4796677.

- [3] F. Zahoor, T. Z. Azni Zulkifli, and F. A. Khanday, "Resistive Random Access Memory (RRAM): an Overview of Materials, Switching Mechanism, Performance, Multilevel Cell (mlc) Storage, Modeling, and Applications," *Nanoscale Res. Lett.*, vol. 15, no. 1, p. 90, Dec. 2020, doi: 10.1186/s11671-020-03299-9.

- [4] B. Chen et al., "Ge-Based Asymmetric RRAM Enable \$8{F}^{2}\$ Content Addressable Memory," IEEE Electron Device Lett., vol. 39, no. 9, pp. 1294–1297, Sep. 2018, doi: 10.1109/LED.2018.2856537.

- [5] J.-J. Huang, C.-W. Kuo, W.-C. Chang, and T.-H. Hou, "Transition of stable rectification to resistive-switching in Ti/TiO2/Pt oxide diode," *Appl. Phys. Lett.*, vol. 96, no. 26, p. 262901, Jun. 2010, doi: 10.1063/1.3457866.

- [6] N. Raghavan, "Performance and reliability trade-offs for high-κ RRAM," *Microelectron. Reliab.*, vol. 54, no. 9–10, pp. 2253–2257, Sep. 2014, doi: 10.1016/j.microrel.2014.07.135.

- [7] M. M. Rehman, H. M. M. U. Rehman, J. Z. Gul, W. Y. Kim, K. S. Karimov, and N. Ahmed, "Decade of 2D-materials-based RRAM devices: a review," *Sci. Technol. Adv. Mater.*, vol. 21, no. 1, pp. 147–186, Jan. 2020, doi: 10.1080/14686996.2020.1730236.

- [8] B. Chakrabarti, T. Roy, and E. M. Vogel, "Non-linear Switching with Ultra-low Reset Power in graphene-insulator-graphene Forming-free Resistive Memories," *IEEE Electron. Dev. Lett.*, vol. 35, no. 7, pp. 750–752, 2014.

- [9] X. Guan, S. Yu, and H.-S. P. Wong, "A SPICE Compact Model of Metal Oxide Resistive Switching Memory With Variations," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1405–1407, Oct. 2012, doi: 10.1109/LED.2012.2210856.

- [10] P. Huang *et al.*, "A Physics-Based Compact Model of Metal-Oxide-Based RRAM DC and AC Operations," *IEEE Trans. Electron Devices*, vol. 60, no. 12, pp. 4090–4097, Dec. 2013, doi: 10.1109/TED.2013.2287755.

- [11] S. Ambrogio, S. Balatti, D. C. Gilmer, and D. Ielmini, "Analytical Modeling of Oxide-Based Bipolar Resistive Memories and Complementary Resistive Switches," *IEEE Trans. Electron Devices*, vol. 61, no. 7, pp. 2378–2386, Jul. 2014, doi: 10.1109/TED.2014.2325531.