## TIMING ANALYSIS-HIERARCHY AND POWER ESTIMATION OF CORES IN ASIC AND FPGA

A Project Report

submitted by

#### **BANAVATH VALYA**

in partial fulfilment of the requirements

for the award of the degree of

#### MASTER OF TECHNOLOGY

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS. JUNE 2017

THESIS CERTIFICATE

This is to certify that the thesis titled "Timing Analysis-Hierarchy and Power Esti-

mation of Cores In ASIC and FPGA", submitted by BANAVATH VALYA, to the

Indian Institute of Technology, Madras, for the award of the degree of Master of Tech-

nology(Microelectronics and VLSI design), is a bonafide record of the research work

done by him under our supervision. The contents of this thesis, in full or in parts, have

not been submitted to any other Institute or University for the award of any degree or

diploma.

Prof. Dr.Nitin Chandrachoodan

Project Guide Associate Professor Dept. of Electrical Engineering IIT-Madras, 600 036

Date: 19th June 2017

Place: Chennai

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude towards Prof.Dr.Nitin Chandrachoodan for backing and guiding me throughout the journey of this project.He gave me enough space and freedom to explore my ideas, pursue and tackle so turned out to be interesting problem statements.His immense knowledge in both software and hardware has helped me into getting out-of-the-box perspectives and interesting insights into the project, which only rose the bar of what we aimed at achieving ,one step at a time.

I thank my friends Bibin basheer, Ravi chandra, Nagaraju and Shivani who were with me throughout the project

Lastly and most importantly, I owe my accomplishments to my beloved parents, who always stood by me. They are and always have been my source of inspiration, motivation for hard work and self-belief. I am deeply grateful to them for believing in me and shaping me into what i am today. Seeing them content and proud of my achievements makes this all worthwhile.

**ABSTRACT**

KEYWORDS: ASIC and FPGA.

In-order to create a robust design, all chips must pass the timing checks and meet user

specified timing constraints before fabrication. Statistical timing analysis is a method

of validating the timing performance of the design by checking all possible paths for

timing violations under worst case conditions.

Power has always been a design consideration, though a lower priority has been given

to power than the most of the variables(Speed/Performance,risk,etc). Power translates

to significant system cost. FPGA's can be significantly aid the design in reducing the

challenges associated with power consumption. The power dissipation in ASIC com-

prised of power in the digital core logic, memories, analog macros and other IO in-

terfaces. The power dissipation in the digital logic and memory macros can be due to

switching activity, called active power, and the leakage power which is present even

with zero switching activity in the design.

ii

## TABLE OF CONTENTS

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CNIN | JW LEDGEMEN 13                                    |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|-----|

| Al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BSTR | ACT                                               | i   |

| ABSTRACT  LIST OF TABLES  ABBREVIATIONS  1 INTRODUCTION 1.1 Introduction 1.2 Motivation 1.3 Objectives and Contributions 1.4 Organization of thesis  2 Background  3 Timing Analysis 3.1 Introduction 3.2 Static timing analysis 3.3 Critical path 3.4 Dynamic Vs Static Timing Analysis 3.5 Advantages of static Timing Analysis 3.6 Disadvantages of static Timing Analysis 3.7 Advantages of dynamic Timing Analysis 3.7 Advantages of dynamic Timing Analysis 3.7 Results and Discussions 5.1 Variation of Power in FPGA with Timing Constraint | xi   |                                                   |     |

| Al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BBRE | EVIATIONS                                         | xii |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INT  | RODUCTION                                         | 1   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.1  | Introduction                                      | 1   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.2  | Motivation                                        | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.3  | Objectives and Contributions                      | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.4  | Organization of thesis                            | 3   |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bac  | kground                                           | 4   |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Tim  | ing Analysis                                      | 5   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.1  | Introduction                                      | 5   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.2  | Static timing analysis                            | 5   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.3  | Critical path                                     | 6   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.4  | Dynamic Vs Static Timing Analysis                 | 6   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.5  | Advantages of static Timing Analysis              | 7   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.6  | Disadvantages of static Timing Analysis           | 7   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.7  | Advantages of dynamic Timing Analysis             | 7   |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pow  | er in FPGA and ASIC                               | 1   |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Resi | ults and Discussions                              | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.1  | Variation of Power in FPGA with Timing Constraint | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 5.1.1 Project Core : AES_128                      | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.2  | Discussion                                        | 2   |

|   |     | 5.2.1  | Project Core: Configurable Cordic Core               | 3  |

|---|-----|--------|------------------------------------------------------|----|

|   |     | 5.2.2  | Discussion                                           | 3  |

|   |     | 5.2.3  | Project Core :Cordic polar2rect                      | 4  |

|   |     | 5.2.4  | Project Core :Cordic rect2polar                      | 5  |

|   |     | 5.2.5  | Project Core :Fixed Point Arithmatic Module :Divider | 6  |

|   |     | 5.2.6  | Project Core :Fixed Point Math Library :Divider      | 7  |

|   | 5.3 | Variat | ion of Power in ASIC with Timing Constraint          | 8  |

|   |     | 5.3.1  | Project Core: AES_128                                | 8  |

|   |     | 5.3.2  | Project Core: Configurable Cordic Core               | 9  |

|   |     | 5.3.3  | Project Core : Cordic_polar2rect                     | 10 |

|   |     | 5.3.4  | Project Core :Fixed point math library_divider       | 11 |

|   | 5.4 | Variat | ion of FPGA Size with Timing Constraint              | 13 |

|   |     | 5.4.1  | Project Core: AES_128                                | 13 |

|   |     | 5.4.2  | Project Core: Configurable cordic core               | 15 |

|   |     | 5.4.3  | Project Core : Cordic_polar2rect                     | 17 |

|   |     | 5.4.4  | Project Core : Cordic_polar2rect                     | 19 |

|   | 5.5 | Variat | ion of ASIC Size with Timing Constraint              | 21 |

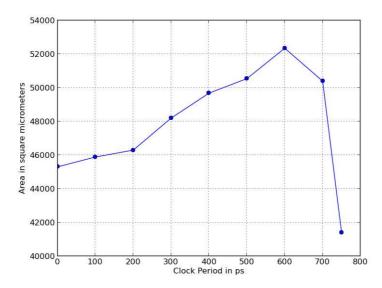

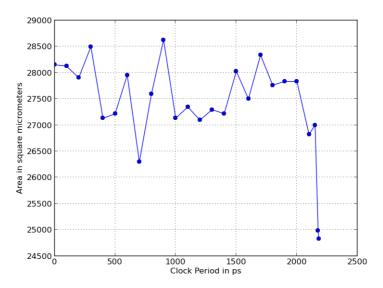

|   |     | 5.5.1  | Project Core: AES_128                                | 21 |

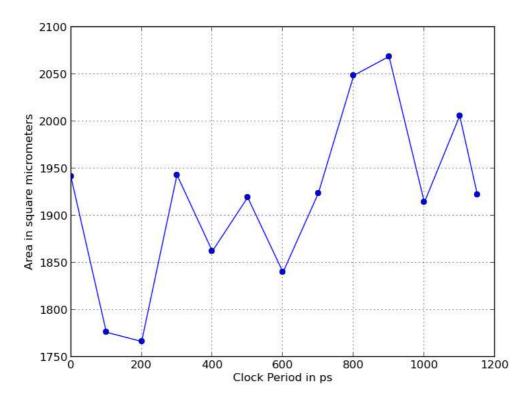

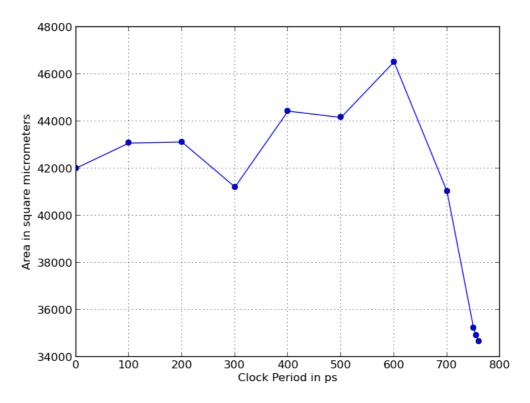

|   |     | 5.5.2  | 8-bit Vedic Multiplier                               | 26 |

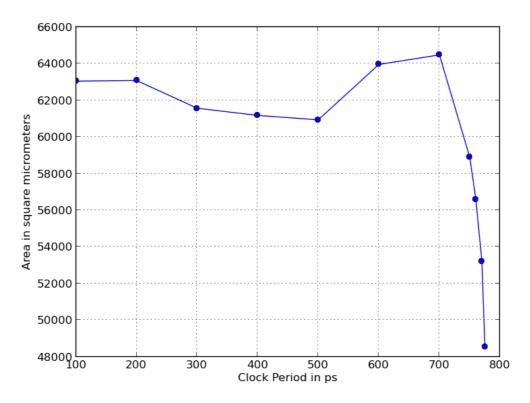

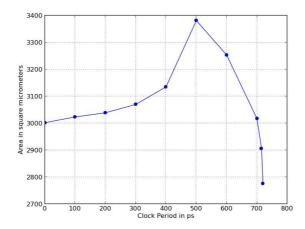

|   |     | 5.5.3  | Configurable Cordic Core                             | 31 |

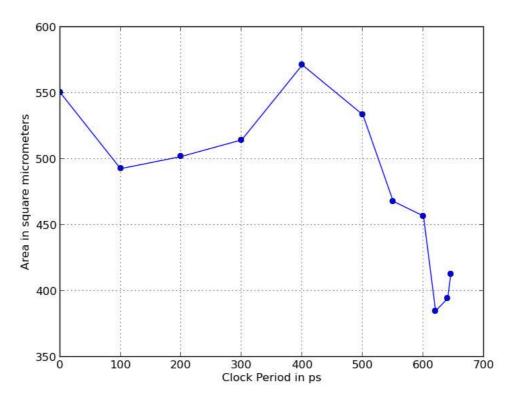

|   |     | 5.5.4  | CORDIC CORE: cordic polar2rect                       | 34 |

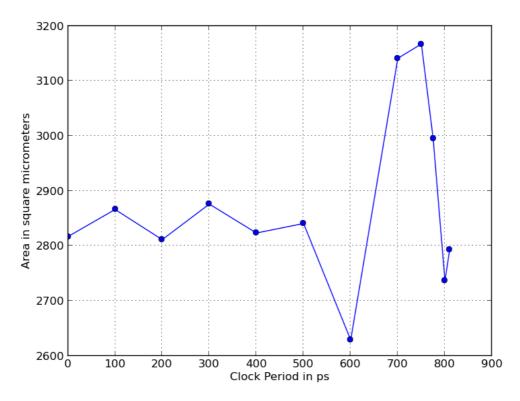

|   |     | 5.5.5  | CORDIC CORE : cordic rect2polar                      | 38 |

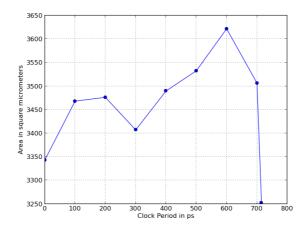

|   |     | 5.5.6  | FIXED_POINT_ARITHMATIC_MODULE: Adder                 | 42 |

|   |     | 5.5.7  | FIXED_POINT_ARITHMATIC_MODULE: Multiplier            | 45 |

|   |     | 5.5.8  | FIXED_POINT_ARITHMATIC_MODULE: Divider               | 48 |

|   |     | 5.5.9  | FIXED_POINT_ARITHMATIC_MODULE:Twoscomp               | 51 |

|   |     | 5.5.10 | FIXED_POINT_MATH_LIBRARY:Adder                       | 55 |

|   |     | 5.5.11 | FIXED_POINT_MATH_LIBRARY:Multiplier                  | 59 |

|   |     | 5.5.12 | FIXED_POINT_MATH_LIBRARY:Divider                     | 62 |

|   |     | 5.5.13 | FIXED_POINT_MATH_LIBRARY:Mults                       | 66 |

| 6 | CO  | NCLUS  | IONS                                                 | 69 |

7 References 70

## LIST OF TABLES

2

| 5.1  | Shows Variation of power with timing constraint for the project core AE  | S_128.     | 2           |

|------|--------------------------------------------------------------------------|------------|-------------|

| 5.2  | Shows Variation of Power with timing constraint from 5ns to 50ns         | 3          |             |

| 5.3  | Shows Variation of Power with timing constraint from 0ns to 50ns         | 4          |             |

| 5.4  | Shows Variation of Power with timing constraint from 0ns to 50ns         | 5          |             |

| 5.5  | Shows Variation of Power with timing constraint from 0ns to 50ns         | 6          |             |

| 5.6  | Shows Variation of Power with timing constraint from 0ns to 50ns         | 7          |             |

| 5.7  | Shows Variation of power with timing constraint for the project core AE  | S_128.     | 8           |

| 5.8  | Shows Variation of power with timing constraint for the project core Co  | nfigurable | cordic co   |

| 5.9  | Shows Variation of power with timing constraint for the project core Co  | nfigurable | cordic_po   |

| 5.10 | Shows Variation of power with timing constraint for the project core Fix | ed point r | nath librar |

| 5.11 | Shows clock period 5ns with Utilization 15.24%                           | 13         |             |

| 5.12 | Shows clock period 10ns with Utilization 15.24%                          | 13         |             |

| 5.13 | Shows clock period 20ns with Utilization 15.24%                          | 13         |             |

| 5.14 | Shows clock period 50ns with Utilization 15.24%                          | 13         |             |

| 5.15 | Shows clock period 100ns with Utilization 15.24%                         | 14         |             |

| 5.16 | Shows clock period 5ns with Utilization 18.36%                           | 15         |             |

| 5.17 | Shows clock period 10ns with Utilization 18.36%                          | 15         |             |

| 5.18 | Shows clock period 20ns with Utilization 18.36%                          | 15         |             |

| 5.19 | Shows clock period 50ns with Utilization 18.36%                          | 15         |             |

| 5.20 | Shows clock period 100ns with Utilization 18.36%                         | 16         |             |

| 5.21 | Shows clock period 5ns with Utilization 10.61%                           | 17         |             |

| 5.22 | Shows clock period 10ns with Utilization 10.61%                          | 17         |             |

| 5.23 | Shows clock period 20ns with Utilization 10.61%                          | 17         |             |

| 5.24 | Shows clock period 50ns with Utilization 10.61%                          | 17         |             |

| 5.25 | Shows clock period 100ns with Utilization 10.61%                         | 18         |             |

| 5.26 | Shows clock period 5ns with Utilization 17.72%                           | 19         |             |

| 5.27 | Shows clock period 10ns with Utilization 17.67%                          | 19         |             |

| 5.28 | Shows clock period 20ns with Utilization 17.67%                          | 19         |             |

| 5.29 | Shows clock period 50ns with Utilization 17.67%           | 19 |

|------|-----------------------------------------------------------|----|

| 5.30 | Shows clock period 100ns with Utilization 17.67%          | 20 |

| 5.31 | Shows clock period 0ps with timing Violation of -1298ps   | 21 |

| 5.32 | Shows clock period 100ps with timing Violation of -1206ps | 21 |

| 5.33 | Shows clock period 200ps with timing Violation of -1092ps | 21 |

| 5.34 | Shows clock period 300ps with timing Violation of -992ps  | 22 |

| 5.35 | Shows clock period 400ps with timing Violation of -898ps  | 22 |

| 5.36 | Shows clock period 500ps with timing Violation of -798ps  | 22 |

| 5.37 | Shows clock period 600ps with timing Violation of -715ps  | 22 |

| 5.38 | Shows clock period 700ps with timing Violation of -600ps  | 23 |

| 5.39 | Shows clock period 800ps with timing Violation of -547ps  | 23 |

| 5.40 | Shows clock period 900ps with timing Violation of -453ps  | 23 |

| 5.41 | Shows clock period 1000ps with timing Violation of -314ps | 23 |

| 5.42 | Shows clock period 1100ps with timing Violation of -197ps | 24 |

| 5.43 | Shows clock period 1200ps with timing Violation of -95ps  | 24 |

| 5.44 | Shows clock period 1250ps with timing Violation of -35ps  | 24 |

| 5.45 | Shows clock period 1275ps with timing Violation of -15ps  | 24 |

| 5.46 | Shows clock period 1280ps with timing slack of 0ps        | 25 |

| 5.47 | Shows clock period 0ps with timing Violation of -1144ps   | 26 |

| 5.48 | Shows clock period 100ps with timing Violation of -1070ps | 26 |

| 5.49 | Shows clock period 200ps with timing Violation of -969ps  | 26 |

| 5.50 | Shows clock period 300ps with timing Violation of -847ps  | 26 |

| 5.51 | Shows clock period 400ps with timing Violation of -774ps  | 27 |

| 5.52 | Shows clock period 500ps with timing Violation of -651ps  | 27 |

| 5.53 | Shows clock period 600ps with timing Violation of -556ps  | 27 |

| 5.54 | Shows clock period 700ps with timing Violation of -466ps  | 27 |

| 5.55 | Shows clock period 800ps with timing Violation of -334ps  | 28 |

| 5.56 | Shows clock period 900ps with timing Violation of -237ps  | 28 |

| 5.57 | Shows clock period 1000ps with timing Violation of -164ps | 28 |

| 5.58 | Shows clock period 1100ps with timing Violation of -41ps  | 29 |

| 5.59 | Shows clock period 1140ps with timing Violation of -13ps  | 29 |

| 5.60 | Shows clock period 1150ps with timing Slack 0ps           | 29 |

| 5.61 | Shows clock period 0ps with timing Violation -751ps     | 31 |

|------|---------------------------------------------------------|----|

| 5.62 | Shows clock period 100ps with timing Violation -647ps   | 31 |

| 5.63 | Shows clock period 200ps with timing Violation -549ps   | 31 |

| 5.64 | Shows clock period 300ps with timing Violation -442ps   | 31 |

| 5.65 | Shows clock period 400ps with timing Violation -359ps   | 32 |

| 5.66 | Shows clock period 500ps with timing Violation -247ps   | 32 |

| 5.67 | Shows clock period 600ps with timing Violation -139ps   | 32 |

| 5.68 | Shows clock period 700ps with timing Violation -53ps    | 32 |

| 5.69 | Shows clock period 750ps with timing Slack 0ps          | 33 |

| 5.70 | Shows clock period 0ps with timing Violation -730ps     | 34 |

| 5.71 | Shows clock period 100ps with timing Violation -627ps   | 34 |

| 5.72 | Shows clock period 200ps with timing Violation -534ps   | 34 |

| 5.73 | Shows clock period 300ps with timing Violation -433ps   | 34 |

| 5.74 | Shows clock period 400ps with timing Violation -319ps   | 35 |

| 5.75 | Shows clock period 500ps with timing Violation -238ps   | 35 |

| 5.76 | Shows clock period 600ps with timing Violation -118ps   | 35 |

| 5.77 | Shows clock period 700ps with timing Violation -20ps    | 35 |

| 5.78 | Shows clock period 750ps with timing Violation -1ps     | 36 |

| 5.79 | Shows clock period 755ps with timing Slack 0ps          | 36 |

| 5.80 | Shows clock period 760ps with timing Slack 0ps          | 36 |

| 5.81 | Shows clock period 0ps with timing Violation -764ps     | 38 |

| 5.82 | Shows clock period 100ps with timing Violation -661ps   | 38 |

| 5.83 | Shows clock period 200ps with timing Violation -562ps   | 38 |

| 5.84 | Shows clock period 300ps with timing Violation -462ps   | 38 |

| 5.85 | Shows clock period 400ps with timing Violation -372ps   | 39 |

| 5.86 | Shows clock period 500ps with timing Violation -285ps   | 39 |

| 5.87 | Shows clock period 600ps with timing Violation -161ps   | 39 |

| 5.88 | Shows clock period 700ps with timing Violation -56ps    | 39 |

| 5.89 | Shows clock period 750ps with timing Violation -17ps    | 40 |

| 5.90 | Shows clock period 760ps with timing Violation of -12ps | 40 |

| 5.91 | Shows clock period 770ps with timing Slack -0ps         | 40 |

| 5.92 | Shows clock period 770ps with timing Slack 0ps          | 40 |

| 5.93  | Shows clock period 0ps with timing Violation -730ps     | 42 |

|-------|---------------------------------------------------------|----|

| 5.94  | Shows clock period 100ps with timing Violation -592ps   | 42 |

| 5.95  | Shows clock period 200ps with timing Violation -496ps   | 42 |

| 5.96  | Shows clock period 300ps with timing Violation -404ps   | 42 |

| 5.97  | Shows clock period 400ps with timing Violation -307ps   | 43 |

| 5.98  | Shows clock period 500ps with timing Violation -209ps   | 43 |

| 5.99  | Shows clock period 600ps with timing Violation -113ps   | 43 |

| 5.100 | Shows clock period 700ps with timing Violation -2ps     | 43 |

| 5.101 | Shows clock period 750ps with timing Slack 0ps          | 44 |

| 5.102 | 2Shows clock period 0ps with timing Violation -2090ps   | 45 |

| 5.103 | 3Shows clock period 500ps with timing Violation -1613ps | 45 |

| 5.104 | Shows clock period 1000ps with timing Violation -1103ps | 45 |

| 5.105 | Shows clock period 1500ps with timing Violation -582ps  | 45 |

| 5.106 | Shows clock period 2000ps with timing Violation -85ps   | 46 |

| 5.107 | Shows clock period 2100ps with timing Violation -26ps   | 46 |

| 5.108 | Shows clock period 2150ps with timing Violation -2ps    | 46 |

| 5.109 | Shows clock period 2175ps with timing Violation -26ps   | 46 |

| 5.110 | Shows clock period 2180ps with timing Slack 0ps         | 47 |

| 5.111 | Shows clock period 0ps with timing Violation -724ps     | 48 |

| 5.112 | 2Shows clock period 100ps with timing Violation -627ps  | 48 |

| 5.113 | Shows clock period 200ps with timing Violation -539ps   | 48 |

| 5.114 | 4Shows clock period 300ps with timing Violation -439ps  | 48 |

| 5.115 | Shows clock period 400ps with timing Violation -338ps   | 49 |

| 5.116 | Shows clock period 500ps with timing Violation -216ps   | 49 |

| 5.117 | Shows clock period 600ps with timing Violation -110ps   | 49 |

| 5.118 | Shows clock period 700ps with timing Violation -18ps    | 49 |

| 5.119 | Shows clock period 715ps with timing violation -19ps    | 50 |

| 5.120 | Shows clock period 720ps with timing Slack 0ps          | 50 |

| 5.121 | Shows clock period 0ps with timing Violation -579ps     | 51 |

| 5.122 | 2Shows clock period 100ps with timing Violation -483ps  | 51 |

| 5.123 | Shows clock period 200ps with timing Violation -382ps   | 51 |

| 5.124 | Shows clock period 300ps with timing Violation -284ps   | 51 |

| 5.125 Shows clock period 400ps with timing Violation -197ps  | 52 |

|--------------------------------------------------------------|----|

| 5.126Shows clock period 500ps with timing Violation -94ps    | 52 |

| 5.127 Shows clock period 550ps with timing Violation -54ps   | 52 |

| 5.128Shows clock period 600ps with timing Violation -9ps     | 52 |

| 5.129 Shows clock period 620ps with timing violation -8ps    | 53 |

| 5.130Shows clock period 640ps with timing Violation -3ps     | 53 |

| 5.131 Shows clock period 645ps with timing Violation 0ps     | 53 |

| 5.132Shows clock period 0ps with timing Violation -805ps     | 55 |

| 5.133 Shows clock period 100ps with timing Violation -696ps  | 55 |

| 5.134Shows clock period 200ps with timing Violation -609ps   | 55 |

| 5.135 Shows clock period 300ps with timing Violation -508ps  | 55 |

| 5.136Shows clock period 400ps with timing Violation -403ps   | 56 |

| 5.137 Shows clock period 500ps with timing Violation -316ps  | 56 |

| 5.138Shows clock period 600ps with timing Violation -229ps   | 56 |

| 5.139 Shows clock period 700ps with timing Violation -98ps   | 56 |

| 5.140Shows clock period 750ps with timing violation -47ps    | 57 |

| 5.141 Shows clock period 775ps with timing Violation -28ps   | 57 |

| 5.142Shows clock period 800ps with timing Violation -1ps     | 57 |

| 5.143 Shows clock period 810ps with timing Slack 0ps         | 58 |

| 5.144Shows clock period 0ps with timing Violation -1486ps    | 59 |

| 5.145 Shows clock period 200ps with timing Violation -1264ps | 59 |

| 5.146Shows clock period 400ps with timing Violation -1072ps  | 59 |

| 5.147 Shows clock period 600ps with timing Violation -858ps  | 59 |

| 5.148Shows clock period 800ps with timing Violation -648ps   | 60 |

| 5.149 Shows clock period 1000ps with timing Violation -453ps | 60 |

| 5.150Shows clock period 1200ps with timing Violation -294ps  | 60 |

| 5.151Shows clock period 1400ps with timing Violation -35ps   | 60 |

| 5.152Shows clock period 1450ps with timing violation -17ps   | 61 |

| 5.153 Shows clock period 1454ps with timing Slack 0ps        | 61 |

| 5.154Shows clock period 0ps with timing Violation -768ps     | 62 |

| 5.155Shows clock period 100ps with timing Violation -669ps   | 62 |

| 5.156Shows clock period 200ps with timing Violation -568ps   | 62 |

| 5.157 Shows clock period 300ps with timing Violation -468ps | 62 |

|-------------------------------------------------------------|----|

| 5.158Shows clock period 400ps with timing Violation -362ps  | 63 |

| 5.159Shows clock period 500ps with timing Violation -280ps  | 63 |

| 5.160Shows clock period 600ps with timing Violation -182ps  | 63 |

| 5.161 Shows clock period 700ps with timing Violation -74ps  | 63 |

| 5.162Shows clock period 750ps with timing violation -26ps   | 64 |

| 5.163 Shows clock period 765ps with timing Violation -3ps   | 64 |

| 5.164Shows clock period 770ps with timing Slack 0ps         | 64 |

| 5.165 Shows clock period 0ps with timing Violation -752ps   | 66 |

| 5.166Shows clock period 100ps with timing Violation -647ps  | 66 |

| 5.167 Shows clock period 200ps with timing Violation -554ps | 66 |

| 5.168Shows clock period 300ps with timing Violation -443ps  | 66 |

| 5.169 Shows clock period 400ps with timing Violation -350ps | 67 |

| 5.170Shows clock period 500ps with timing Violation -257ps  | 67 |

| 5.171 Shows clock period 600ps with timing Violation -165ps | 67 |

| 5.172Shows clock period 700ps with timing Violation -38ps   | 67 |

| 5.173 Shows clock period 745ps with timing violation -0ps   | 68 |

| 5.174Shows clock period 750ps with timing slack 0ps         | 68 |

## **ABBREVIATIONS**

**IITM** Indian Institute of Technology, Madras

**RTFM** Read the Fine Manual

**FPGA** Field Programmable Gate Array

**ASIC** Application Specific Integrated circuits

STA Static timing analysis

**DTA** Dynamic timing analysis

**SSTA** Statistical Static timing analysis

**DRC** Design check rule

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Introduction

As the increase in complexity of digital designs and the requirements in various design stages make static timing analysis critical. Each design stage utilizes static timing analysis to evaluate the system performance, and then optimizes the design accordingly. An accurate and efficient timing analysis package is crucial for the success of whole design process. Timing is important because just designing the chip is not enough, we need to know how fast the chip is going to run, how fast the chip is going to interact with other chips, how fast the input reaches the output.

Timing analysis is used to perform the timing constraints of the design. Timing verification is an important phase in timing analysis as incorrect constraints lead to chip failures. Logic circuits generally consists of large number of paths through which signals cannot propagate in functional mode analysis, these paths are known as unsensitizable paths, or simply false paths. Timing analysis tools can report true critical and false paths . The critical paths reported by the timing tools may or may not be synthesizable. In ASIC timing analysis can be applied in both pre-layout and post lay-out. In pre-layout delay calculation is an estimation of the incorrect delay values. In post-layout timing analysis the delays values are accurate. Morever static timing analysis cannot provide the details of how many critical paths exist in the circuit. A path can also be called as false path if the transitions on the input cannot be propagated to the output along the path. If any one false critical path is right regarded as the a critical path, the results are conservative and the performance of the circuit would be affected. There may be 30 percent of paths in the circuit that are reported as false paths.

Power is always been a design consideration, though a lower priority has been given to power than the most of the variables (Speed/ Performance, risk etc.). Power translates to significant system cost. FPGAs can be significantly aid the design in reducing the challenges associated with power consumption.

The power dissipation in ASIC comprised of power in the digital core logic, memories, analog macos and other IO interfaces.

#### 1.2 Motivation

Motivation behind this tool is to facilitate an open-source unified academic timing engine that performs timing analysis and to enable timing driven flows.

Many commercial tools like Synopsis, Cadence design compiler are well known and widely used industry-wide as well as in academia for timing verification of digital designs at various stages of VLSI design flow.

## 1.3 Objectives and Contributions

Following points highlights the objectives of this thesis:

- 1. To understand how ASIC and FPGA size changes with the timing constraint.

- 2. To estimate how power changes with the timing constraint in ASIC and FPGA.

- 3. Compare results of ASIC and FPGA and understand the similarities.

- 4. To know what is logic depth(Gates in critical path from input to output).

In this thesis, we present how the size (Number of Gates, FF, IO, BUFG) changes with timing constraints, the resource available and how much resource is utilized including percentage of resource utilized is also mentioned in the thesis. Power is calculated in both ASIC and FPGA, In FPGA total on-chip power, Dynamic power(Power utilized for clocks, Logic, Signals, IO) and device static power are estimated for various timing constraint and how the power is changing with variation of timing constraint is reported. Also in FPGA, static timing analysis which includes Worst neative slack, Total negative slack, Number of failing end points, Total number of failing end points, Path delay, Logic delay, Net delay, Clock skew, Slack, High fan-out, cumulative fan-out for critical setup path and critical hold path are reported. Power and delay analysis framework is necessary for FPGA power and delay optimization.

In ASIC Changes in size(Gates) with changes in time period is studied, Variation of leakage power and Total power with changes in timing constraint is reported and timing

slack is calculated for various clock periods and the clock period at which the timing

slack becomes 0 is reported.

1.4 **Organization of thesis**

The rest of the thesis is organized in the following manner:

chapter2: Background

This chapter discusses the related work, definitions involved along the theoretical back-

ground on timing analysis, power and Hierarchy.

chapter3: Timing Analysis

This chapter discusses how timing verification is important phase in timing analysis.

How fast the chip is going to interact with other chips, how fast the chip is going to run,

how fast input reaches the output.

**Chapter4: Power in FPGA and ASIC**

This chapter discusses the basic understanding of power and how the power varies with

timing constraint in ASIC and FPGA.

**Chapter5: Results and Discussions**

The synthesis results of both ASIC and FPGA are reported and discussed how power

and Size Of ASIC and FPGA changes with timing constraint.

**Chapter6: Conclusions**

3

#### **CHAPTER 2**

## **Background**

Miniaturization of transistor size comprises in increasing the complexity of digital designs. So, timing analysis is performed to meet the user specified timing constraints of the design, All chips must pass the timing checks and meet the user specified the timing constraints of the design before fabrication. Static timing analysis is a method of validating the timing performance of the design by checking all possible paths got timing violations under worst-case conditions. The characteristics of static timing analysis only consider the delay of each logic gates and cells in the path and doesn't take functional behaviour of the logic cells into account. All timing paths will not active in real work environment. These paths which are not activated are known as false paths. The traditional static timing analysis results are estimation as many critical paths are not true paths and most of the critical paths are false paths or non-functional paths. In classic design flow, the critical path delay is calculated through static timing analysis. This approach may leads to enormous results as static timing analysis cannot accurately calculate path delay of all critical paths

Elimination of false paths provides area and power advantage. Moreover static timing analysis cannot provide the details of how many critical paths exist in the circuit. A path can also be called as false path if the transition on the input cannot be propagated to the output along the path. If any one false critical path is right regarded as a critical path, the results are conservative and performance of the circuit would be affected. There may up to 30% of paths in the circuit are reported as false paths. So, it is predicted that static timing analysis reported in critical paths may be false. The corresponding delay of the circuit may or may not be accurate and overly pessimistic. The main drawback of static time analysis is inability to detect accurate false path automatically and also the number of false critical paths. The other one is static timing analysis is neglect the simultaneous input transitions.

#### **CHAPTER 3**

## **Timing Analysis**

#### 3.1 Introduction

High-performance integrated circuits have traditionally been characterized by the clock frequency at which they operate. Gauging the ability of a circuit to operate at the specified speed requires ability to measure its delay at numerous steps during the design process. There are mainly two approaches for timing analysis: Static and dynamic timing analysis.

## 3.2 Static timing analysis

Static timing analysis is a method of computing the expected timing a digital circuit without requiring circuit level simulation. By giving each circuit component an "associated delay", it doesn't need to test all possible input vectors. In this way, it treats circuit component delay independently as a solution of a whole system. STA therefore greatly reduces the time to compute the delay at the expense of accuracy. On the contrary, dynamic timing analysis uses the circuit simulation and tries on large number of samples of input vectors. Therefore, it is time consuming.

In ASIC design flow static timing analysis is applied in both pre-layout and postlayout. In the synthsis phase all the timing requirements clock, input load, output load and user defined timing constraint are specified. Timing analysis is applied to match the user specified design constraints. In design for testing the phase design check rule (DRC) is performed to identify all the timing violations, and therefore floor planning phase all the timing all the timing violations are removed. After floor planning parasitics are extracted which contains the delay values.

## 3.3 Critical path

The critical path is defined as the path between an input and output with maximum delay. The critical path can easily be found by using a trace back method.

## 3.4 Dynamic Vs Static Timing Analysis

- Timing analysis is an integral part of ASIC/FPGA design flow. It has to be accomplished and the functionality of the design must be cleared before the design is subjected to Static timing analysis. Anything can be compromised but not timing.

- In addition to the above discussed STA, dynamic timing analysis(DTA) can be used to verify functionality of the design by applying input vectors and checking for correct output vectors.

- In contrast, STA checks static delay requirements of the circuit without any input or output vectors.

- Dynamic timing analysis is a circuit level simulation used for the characterization of timing properties of a complete cell, which most of the time is logic gate. Dynamic timing analysis and STA are not alternatives to each other. The quality of the DTA increases of input test vectors. Increased test vectors increase simulation time.

- DTA can be used for synchronous as well as asynchronous designs. STA can't run on asynchronous designs and therefore DTA is the best way to analyze asynchronous designs. It is the best suited for designs having clocks crossing multiple domains. Finally, DTA is also carried to on post layout netlist to verify that functionality of the design has not changed. Test vectors remain same for both.

## 3.5 Advantages of static Timing Analysis

- Static timing analysis(STA) considers all the timing paths ,whether it may be functional or non-functional paths. STA analysis is very fast and exhaustive compared to statistical static timing analysis(SSTA) and dynamic timing analysis.

- STA is analyzed for best, worst and typical cases, while dynamic simulation it is not possible. Static timing analysis calculates the delay through delay models, STA results are pessimistic in nature and fast. DTA is slow and accurate, as it checks the functionality of the design. DTA is very complex compared to STA.

## 3.6 Disadvantages of static Timing Analysis

- Since STA is pessimistic and considers the false critical path as false critical path is non-functional path. In general STA critical paths are false in nature. If a false path is considered for circuit delay calculation, the output will conservative and results are affected.

- STA will add the delay of the gates and logic cells along the path, it doesn't take functionality of the design onto account. STA cannot be applicable to synchronous circuits.

## 3.7 Advantages of dynamic Timing Analysis

• Very accurate but slow and the quality depends on input vectors. Dynamic timing analysis is non-exhaustive.

#### **CHAPTER 4**

#### **Power in FPGA and ASIC**

Power has always been a design considerations. Traditionally, though, a lower priority has been assigned to power than to most other variables.

Power consumption in ASIC comprised of power in the digital core logic, memories and IO interfaces.

There are traditionally four power components that are important when considering a design using FPGA products. These are 1. pre-programmed static device power consumption. 2. Inrush programming power consumption. 3. Post-programmed static power consumption. 4. Dynamic power consumption. Pre-Programmed static power consumption is the amount of power consumed by the FPGA prior to the device being programmed. For quiescent device power consumption the FPGA is in a non-programmed state, Yet has been powered. It is important that the device not consume significant power during this time.

Post-Programmed static device power consumption is a very significant component of FPGA power consumption. This is due to the large number of transistors on FPGAs. The leakage on these transistors typically is always on and drawing power whether the transistor is used or not. Typically, Post-programmed static power is equal to the or greater than the previously described quiescent static power. There are some recent innovations addressing power grids and removing power to the transistor, etc., which will impact static power.

Dynamic power is a significant component in power analysis and , depending on the type of design being implemented.

#### **CHAPTER 5**

#### **Results and Discussions**

## 5.1 Variation of Power in FPGA with Timing Constraint

#### 5.1.1 Project Core : AES\_128

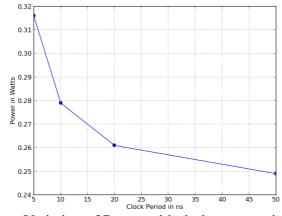

The follwing table shows how Power changes with variation of clock periods.

| ClockPeriod(ns) | Power(inWatts) |

|-----------------|----------------|

| 5               | 0.316          |

| 10              | 0.279          |

| 20              | 0.261          |

| 50              | 0.249          |

Table 5.1: Shows Variation of power with timing constraint for the project core AES\_128.

## 5.2 Discussion

The clock period is varied from 5ns to 50ns, Power is decreased from 0.316Watts to 0.249Watts. This clearly indicates that as the timing constraint is increases, power is decreasing gradually for the project core AES\_128.

Figure 5.1: Shows Variation of Power with timing constraint from 0ns to 50ns.

#### **5.2.1** Project Core : Configurable Cordic Core

The follwing table shows how Power changes with variation of clock periods.

| ClockPeriod(ns) | Power(inWatts) |

|-----------------|----------------|

| 5               | 0.316          |

| 10              | 0.279          |

| 20              | 0.261          |

| 50              | 0.249          |

Table 5.2: Shows Variation of Power with timing constraint from 5ns to 50ns.

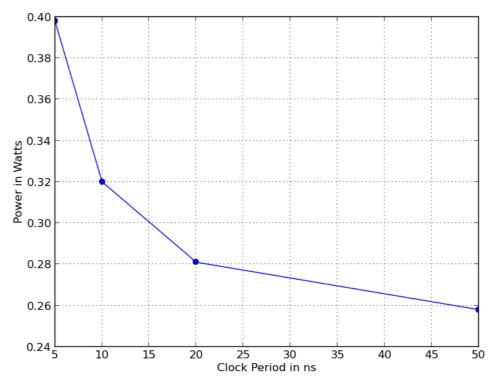

#### 5.2.2 Discussion

From the above table, Power is 0.316Watts at clock period 5ns, 0.279Watts at clock period 10ns, 0.261Watts at clock Period 20ns and 0.249Watts at clock Period 50ns. As the clock period varies from 0ns to 50ns, power is decreased from 0.316Watts to 0.249Watts. From the above analysis it clear that as the clock period is increases power decreases gradually.

Same as project core AES\_128, Power is decreasing as the timing constraint is keep on increasing for the project core: Configurable Cordic Core. From the power analysis of project core AES\_128 and Configurable cordic Core it is clear that as the timing constarint is keep on increasing, Power is decreases in FPGA.

As the timing constraint is varied, Power is also varied that is as the clock poeriod is keep on increasing incase of FPGA, Power is keep on decreasing gradually. From the analysis of the project cores AES\_128 and Configurable cordic core it is clear that as the power is keep on decreasing as the clock period is keep on increasing. All the analysis above also shown graphically from which we can clearly understand how the power is varying with the variation of timing constraint.

Figure 5.2: Shows Variation of power with timing constraint for the project core Configurable Cordic Core.

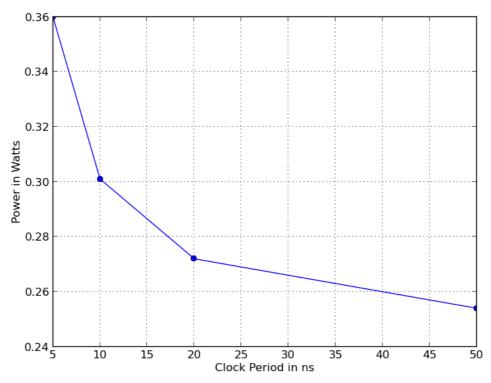

#### 5.2.3 Project Core : Cordic polar2rect

The follwing table shows how Power changes with variation of clock periods. :

| ClockPeriod(ns) | Power(inWatts) |

|-----------------|----------------|

| 5               | 0.36           |

| 10              | 0.301          |

| 20              | 0.272          |

| 50              | 0.250          |

Table 5.3: Shows Variation of Power with timing constraint from 0ns to 50ns.

From the above table, Power is 0.36Watts for the clock period 5ns, 0.301Watts for the clock period 10ns, 0.272Watts for the clock period 20ns and 0.250Watts for the clock period 50ns. As the clock period is keep on increasing from 5ns to 50ns, power is decreased from 0.36Watts to 0.250Watts. From the above analysis it is clear that as the timing constraint is keep on increasing power is decreasing gradually in case of FPGA.

Figure 5.3: Shows Variation of power with timing constraint for the project core Cordic polar2rect.

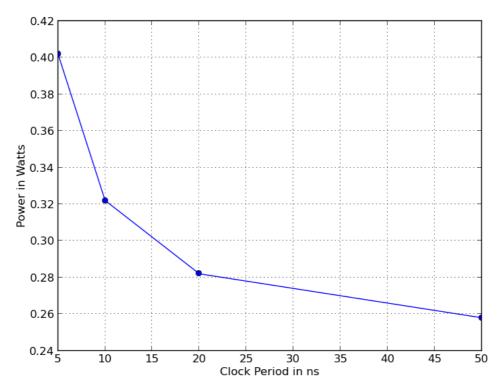

#### 5.2.4 Project Core : Cordic rect2polar

The follwing table shows how Power changes with variation of clock periods.

| ClockPeriod(ns) | Power(inWatts) |

|-----------------|----------------|

| 5               | 0.402          |

| 10              | 0.322          |

| 20              | 0.282          |

| 50              | 0.258          |

Table 5.4: Shows Variation of Power with timing constraint from 0ns to 50ns.

#### **Discussion:**

From the above table, Power is 0.402Watts for the clock period 5ns, 0.322Watts for the clock period 10ns, 0.282Watts for the clock period 20ns and 0.258Watts for the clock period 50ns. As the clock period is keep on increasing from 5ns to 50ns, power is decreased from 0.402Watts to 0.258Watts. From the above analysis it is clear that as the timing constraint is keep on increasing power is decreasing gradually in case of FPGA.

Figure 5.4: Shows Variation of power with timing constraint for the project core Cordic rect2polar.

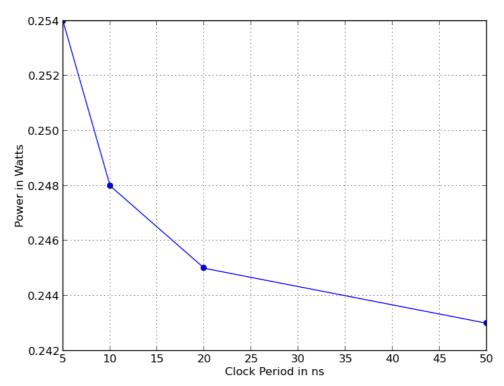

#### 5.2.5 Project Core : Fixed Point Arithmatic Module : Divider

The follwing table shows how Power changes with variation of clock periods.

| ClockPeriod(ns) | Power(inWatts) |

|-----------------|----------------|

| 5               | 0.254          |

| 10              | 0.248          |

| 20              | 0.245          |

| 50              | 0.243          |

Table 5.5: Shows Variation of Power with timing constraint from 0ns to 50ns.

#### **Discussion:**

From the above table, Power is 0.254Watts for the clock period 5ns, 0.248Watts for the clock period 10ns, 0.245Watts for the clock period 20ns and 0.243Watts for the clock period 50ns. As the clock period is keep on increasing from 5ns to 50ns, power is decreased from 0.254Watts to 0.243Watts. From the above analysis it is clear that as the timing constraint is keep on increasing power is decreasing gradually in case of FPGA.

Figure 5.5: Shows Variation of power with timing constraint for the project core Fixed Point arithmatic module: Divider.

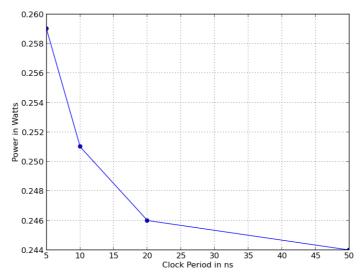

#### 5.2.6 Project Core : Fixed Point Math Library : Divider

The follwing table shows how Power changes with variation of clock periods.

| ClockPeriod(ns) | Power(inWatts) |

|-----------------|----------------|

| 5               | 0.259          |

| 10              | 0.251          |

| 20              | 0.246          |

| 50              | 0.244          |

Table 5.6: Shows Variation of Power with timing constraint from 0ns to 50ns.

#### **Discussion:**

From the above table, Power is 0.254Watts for the clock period 5ns, 0.248Watts for the clock period 10ns, 0.245Watts for the clock period 20ns and 0.243Watts for the clock period 50ns. As the clock period is keep on increasing from 5ns to 50ns, power is decreased from 0.254Watts to 0.243Watts. From the above analysis it is clear that as the timing constraint is keep on increasing power is decreasing gradually in case of FPGA.

Figure 5.6: Shows Variation of power with timing constraint for the project core Fixed Point math library: Divider.

## 5.3 Variation of Power in ASIC with Timing Constraint

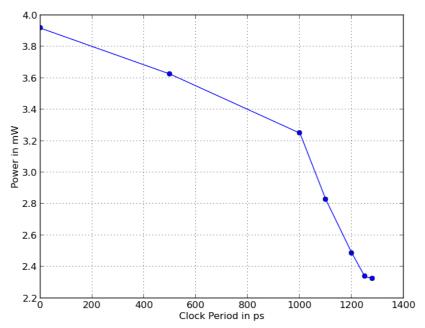

#### 5.3.1 Project Core : AES\_128

| ClockPeriod(ps) | Power(inmW) |

|-----------------|-------------|

| 0               | 3.9177      |

| 500             | 3.6248      |

| 1000            | 3.2492      |

| 1100            | 2.8261      |

| 1200            | 2.4865      |

| 1250            | 2.3369      |

| 1280            | 2.3251      |

Table 5.7: Shows Variation of power with timing constraint for the project core AES\_128.

Figure 5.7: Shows Variation of power with timing constraint for the project core aes\_128.

From the the above figure and table, as the clock period is increased from 0ps to 1280ps, Power is decreased from 3.9177mWatts to 2.3251mWatts. From the above analysis it is clear that as that timing constraint is keep on increasing, power consumption is keep on decreasing incase of ASIC.

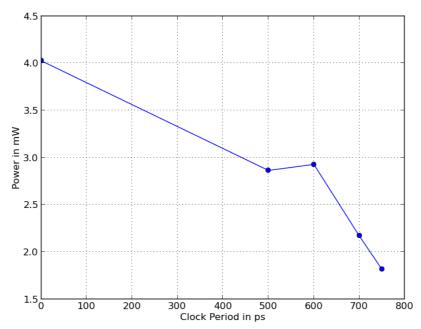

## **5.3.2** Project Core : Configurable Cordic Core

| ClockPeriod(ps) | Power(inmW) |

|-----------------|-------------|

| 0               | 4.026       |

| 500             | 2.864       |

| 600             | 2.928       |

| 700             | 2.169       |

| 750             | 1.184       |

Table 5.8: Shows Variation of power with timing constraint for the project core Configurable cordic core.

Figure 5.8: Shows Variation of power with timing constraint for the project core Configurable cordic core.

From the the above figure and table, as the clock period is increased from 0ps to 750ps, Power is decreased from 4.026mWatts to 1.184mWatts. From the above analysis it is clear that as that timing constraint is keep on increasing, power consumption is keep on decreasing incase of ASIC.

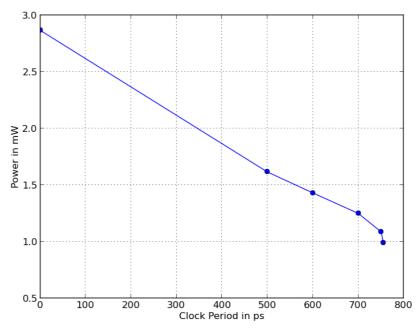

## **5.3.3** Project Core : Cordic\_polar2rect

| ClockPeriod(ps) | Power(inmW) |

|-----------------|-------------|

| 0               | 2.865       |

| 500             | 1.614       |

| 600             | 1.429       |

| 700             | 1.248       |

| 750             | 1.086       |

| 755             | 0.991       |

Table 5.9: Shows Variation of power with timing constraint for the project core Configurable cordic\_polar2rect.

Figure 5.9: Shows Variation of power with timing constraint for the project core cordic\_polar2rect.

From the the above figure and table, as the clock period is increased from 0ps to 755ps, Power is decreased from 2.865mWatts to 0.991mWatts. From the above analysis it is clear that as that timing constraint is keep on increasing, power consumption is keep on decreasing incase of ASIC.

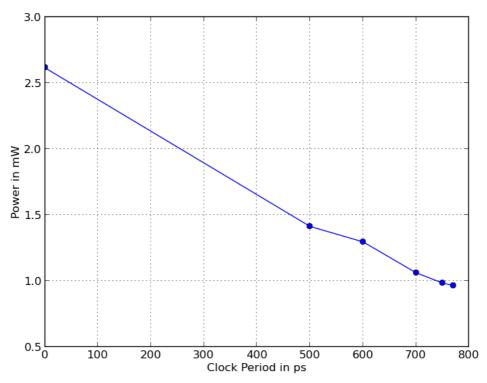

## 5.3.4 Project Core :Fixed point math library\_divider

| ClockPeriod(ps) | Power(inmW) |

|-----------------|-------------|

| 0               | 2.614       |

| 500             | 1.412       |

| 600             | 1.2958      |

| 700             | 1.061       |

| 750             | 0.983       |

| 770             | 0.964       |

Table 5.10: Shows Variation of power with timing constraint for the project core Fixed point math library divider.

Figure 5.10: Shows Variation of power with timing constraint for the project core Fixed point math library\_divider.

From the the above figure and table, as the clock period is increased from 0ps to 770ps, Power is decreased from 2.614mWatts to 0.964mWatts. From the above analysis it is clear that as that timing constraint is keep on increasing, power consumption is keep on decreasing incase of ASIC.

## **5.4** Variation of FPGA Size with Timing Constraint

## 5.4.1 Project Core : AES\_128

#### • Clock Period = 5ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 2041        | 0.67           |

| FF       | 607200    | 910         | 0.15           |

| IO       | 700       | 79          | 11.29          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 3031        | 15.24          |

Table 5.11: Shows clock period 5ns with Utilization 15.24%.

#### • Clock Period = 10ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 2041        | 0.67           |

| FF       | 607200    | 910         | 0.15           |

| IO       | 700       | 79          | 11.29          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 3031        | 15.24          |

Table 5.12: Shows clock period 10ns with Utilization 15.24%.

#### • Clock Period = 20ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 2041        | 0.67           |

| FF       | 607200    | 910         | 0.15           |

| IO       | 700       | 79          | 11.29          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 3031        | 15.24          |

Table 5.13: Shows clock period 20ns with Utilization 15.24%.

#### • Clock Period = 50ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 2041        | 0.67           |

| FF       | 607200    | 910         | 0.15           |

| IO       | 700       | 79          | 11.29          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 3031        | 15.24          |

Table 5.14: Shows clock period 50ns with Utilization 15.24%.

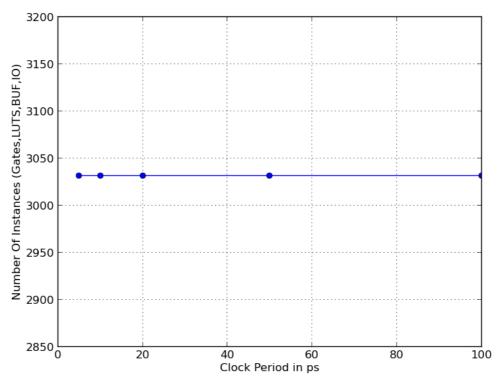

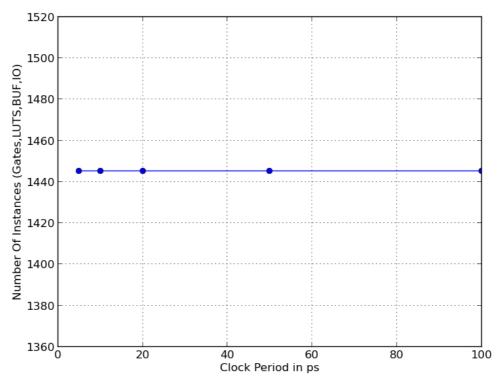

Figure 5.11: Shows Variation of FPGA size with timing constraint for the project core AES\_128.

#### • Clock Period = 100ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 2041        | 0.67           |

| FF       | 607200    | 910         | 0.15           |

| IO       | 700       | 79          | 11.29          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 3031        | 15.24          |

Table 5.15: Shows clock period 100ns with Utilization 15.24%.

#### **Discussion:**

From the above table and figure, As we increase the clock period from 0ns to 100 ns, the number of instances(Gates, LUTs, BUF, IO) are same all clock periods. From the above analysis it is clear that as we keep on increasing the clock periods there is no effect on number of instances. In case of FPGA the timing constraint doesn't effect the number of instances.

## **5.4.2** Project Core : Configurable cordic core

#### • Clock Period = 5ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 735         | 0.24           |

| LUTRAM   | 130800    | 7           | 0.01           |

| FF       | 607200    | 739         | 0.12           |

| IO       | 700       | 104         | 14.86          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1586        | 18.36          |

Table 5.16: Shows clock period 5ns with Utilization 18.36%.

#### • Clock Period = 10ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 735         | 0.24           |

| LUTRAM   | 130800    | 7           | 0.01           |

| FF       | 607200    | 739         | 0.12           |

| IO       | 700       | 104         | 14.86          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1586        | 18.36          |

Table 5.17: Shows clock period 10ns with Utilization 18.36%.

#### • Clock Period = 20ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 735         | 0.24           |

| LUTRAM   | 130800    | 7           | 0.01           |

| FF       | 607200    | 739         | 0.12           |

| IO       | 700       | 104         | 14.86          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1586        | 18.36          |

Table 5.18: Shows clock period 20ns with Utilization 18.36%.

#### • Clock Period = 50ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 735         | 0.24           |

| LUTRAM   | 130800    | 7           | 0.01           |

| FF       | 607200    | 739         | 0.12           |

| IO       | 700       | 104         | 14.86          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1586        | 18.36          |

Table 5.19: Shows clock period 50ns with Utilization 18.36%.

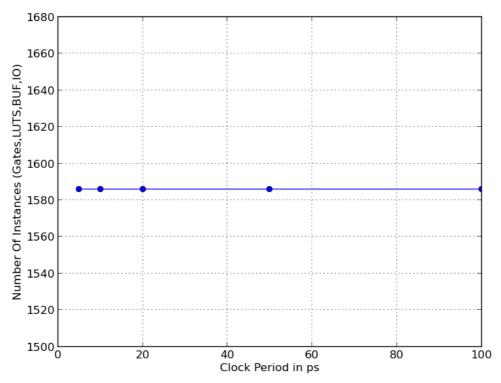

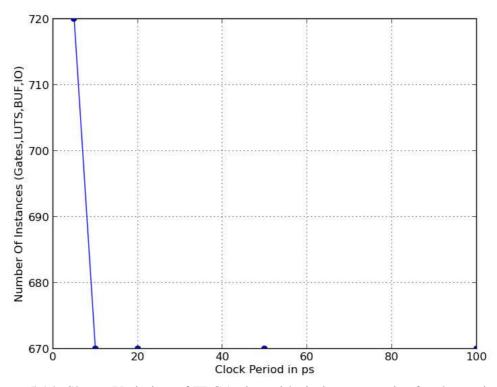

Figure 5.12: Shows Variation of FPGA size with timing constraint for the project core Configurable cordic core.

#### • Clock Period = 100ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 735         | 0.24           |

| LUTRAM   | 130800    | 7           | 0.01           |

| FF       | 607200    | 739         | 0.12           |

| IO       | 700       | 104         | 14.86          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1586        | 18.36          |

Table 5.20: Shows clock period 100ns with Utilization 18.36%.

### **Discussion:**

From the above table and figure, As we increase the clock period from 0ns to 100 ns, the number of instances(Gates, LUTs, BUF, IO) are same all clock periods. From the above analysis it is clear that as we keep on increasing the clock periods there is no effect on number of instances. In case of FPGA the timing constraint doesn't effect the number of instances.

# 5.4.3 Project Core : Cordic\_polar2rect

### • Clock Period = 5ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 705         | 0.23           |

| FF       | 607200    | 689         | 0.11           |

| IO       | 700       | 50          | 7.14           |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1445        | 10.61          |

Table 5.21: Shows clock period 5ns with Utilization 10.61%.

### • Clock Period = 10ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 705         | 0.23           |

| FF       | 607200    | 689         | 0.11           |

| IO       | 700       | 50          | 7.14           |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1445        | 10.61          |

Table 5.22: Shows clock period 10ns with Utilization 10.61%.

### • Clock Period = 20ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 705         | 0.23           |

| FF       | 607200    | 689         | 0.11           |

| IO       | 700       | 50          | 7.14           |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1445        | 10.61          |

Table 5.23: Shows clock period 20ns with Utilization 10.61%.

### • Clock Period = 50ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 705         | 0.23           |

| FF       | 607200    | 689         | 0.11           |

| IO       | 700       | 50          | 7.14           |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1445        | 10.61          |

Table 5.24: Shows clock period 50ns with Utilization 10.61%.

Figure 5.13: Shows Variation of FPGA size with timing constraint for the project core cordic\_polar2rect.

#### • Clock Period = 100ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 705         | 0.23           |

| FF       | 607200    | 689         | 0.11           |

| IO       | 700       | 50          | 7.14           |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 1445        | 10.61          |

Table 5.25: Shows clock period 100ns with Utilization 10.61%.

#### **Discussion:**

From the above table and figure, As we increase the clock period from 0ns to 100 ns, the number of instances(Gates, LUTs, BUF, IO) are same all clock periods. From the above analysis it is clear that as we keep on increasing the clock periods there is no effect on number of instances. In case of FPGA the timing constraint doesn't effect the number of instances.

# **5.4.4** Project Core : Cordic\_polar2rect

# • Clock Period = 5ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 353         | 0.12           |

| FF       | 607200    | 265         | 0.04           |

| IO       | 700       | 101         | 14.43          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 720         | 17.72          |

Table 5.26: Shows clock period 5ns with Utilization 17.72%.

### • Clock Period = 10ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 353         | 0.1            |

| FF       | 607200    | 265         | 0.04           |

| IO       | 700       | 101         | 14.43          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 670         | 17.67          |

Table 5.27: Shows clock period 10ns with Utilization 17.67%.

### • Clock Period = 20ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 353         | 0.1            |

| FF       | 607200    | 265         | 0.04           |

| IO       | 700       | 101         | 14.43          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 670         | 17.67          |

Table 5.28: Shows clock period 20ns with Utilization 17.67%.

### • Clock Period = 50ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 353         | 0.1            |

| FF       | 607200    | 265         | 0.04           |

| IO       | 700       | 101         | 14.43          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 670         | 17.67          |

Table 5.29: Shows clock period 50ns with Utilization 17.67%.

Figure 5.14: Shows Variation of FPGA size with timing constraint for the project core Fixed point math library divider.

#### • Clock Period = 100ns

| Resource | Available | Utilization | Utilization(%) |

|----------|-----------|-------------|----------------|

| LUT      | 303600    | 353         | 0.1            |

| FF       | 607200    | 265         | 0.04           |

| IO       | 700       | 101         | 14.43          |

| BUFG     | 32        | 1           | 3.13           |

| Total    | 911532    | 670         | 17.67          |

Table 5.30: Shows clock period 100ns with Utilization 17.67%.

#### **Discussion:**

From the above table and figure, As we increase the clock period from 0ns to 100 ns, the number of instances(Gates, LUTs, BUF, IO) are same all clock periods. From the above analysis it is clear that as we keep on increasing the clock periods there is no effect on number of instances. In case of FPGA the timing constraint doesn't effect the number of instances.

# **5.5** Variation of ASIC Size with Timing Constraint

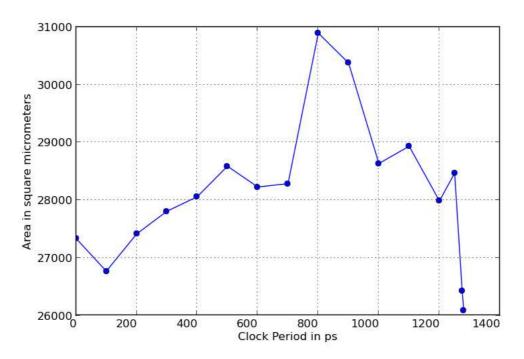

# 5.5.1 Project Core : AES\_128

The follwing tables shows how ASIC size changes with variation of clock periods.

# • Clock Period = 0ps \*Timing Slack = -1298ps (Timing Violation)

| Gates(Type) | Instances | Area      | Area(%) |

|-------------|-----------|-----------|---------|

| Inverter    | 667       | 3123.120  | 11.4    |

| Buffer      | 393       | 1270.920  | 4.6     |

| Logic       | 6168      | 17152.520 | 62.7    |

| Sequential  | 910       | 5791.24   | 21.2    |

| Total       | 9138      | 27337.800 | 100     |

Table 5.31: Shows clock period 0ps with timing Violation of -1298ps.

# • Clock Period = 100ps \*Timing Slack = -1206ps (Timing Violation)

| Gates(Type) | Instances | Area      | Area(%) |

|-------------|-----------|-----------|---------|

| Inverter    | 1504      | 2868.880  | 10.7    |

| Buffer      | 370       | 1208.8    | 4.5     |

| Logic       | 6017      | 16900.24  | 63.1    |

| Sequential  | 910       | 5790.4    | 21.6    |

| Total       | 8801      | 26767.720 | 100     |

Table 5.32: Shows clock period 100ps with timing Violation of -1206ps.

### • Clock Period = 200ps \*Timing Slack = -1092ps (Timing Violation)

| Gates(Type) | Instances | Area      | Area(%) |

|-------------|-----------|-----------|---------|

| Inverter    | 1564      | 2993.480  | 10.9    |

| Buffer      | 380       | 1251.040  | 4.6     |

| Logic       | 6060      | 17362.520 | 63.30   |

| Sequential  | 910       | 5804.960  | 21.20   |

| Total       | 8914      | 27412     | 100     |

Table 5.33: Shows clock period 200ps with timing Violation of -1092ps.

# • Clock Period = 300ps \*Timing Slack = -992ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1595      | 3123.12  | 11.2    |

| Buffer      | 371       | 1202.04  | 4.3     |

| Logic       | 6075      | 17670.8  | 63.60   |

| Sequential  | 910       | 5810     | 20.90   |

| Total       | 8951      | 27805.96 | 100     |

Table 5.34: Shows clock period 300ps with timing Violation of -992ps.

# • Clock Period = 400ps \*Timing Slack = -898ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1634      | 3204.6   | 11.4    |

| Buffer      | 393       | 1284.08  | 4.6     |

| Logic       | 6226      | 17759.56 | 63.30   |

| Sequential  | 910       | 5808.6   | 20.70   |

| Total       | 9163      | 28056.84 | 100     |

Table 5.35: Shows clock period 400ps with timing Violation of -898ps.

# • Clock Period = 500ps \*Timing Slack = -798ps (Timing Violation)

| Gates(Type) | Instances | Area      | Area(%) |

|-------------|-----------|-----------|---------|

| Inverter    | 1624      | 3183.04   | 11.1    |

| Buffer      | 399       | 1360.8    | 4.8     |

| Logic       | 6235      | 18247.6   | 63.80   |

| Sequential  | 910       | 5795.72   | 20.30   |

| Total       | 9168      | 28587.160 | 100     |

Table 5.36: Shows clock period 500ps with timing Violation of -798ps.

## • Clock Period = 600ps \*Timing Slack = -715ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1617      | 3327.8   | 11.80   |

| Buffer      | 378       | 1264.76  | 4.5     |

| Logic       | 6042      | 17806.04 | 63.10   |

| Sequential  | 910       | 5828.2   | 20.60   |

| Total       | 8947      | 28226.8  | 100     |

Table 5.37: Shows clock period 600ps with timing Violation of -715ps.

# • Clock Period = 700ps \*Timing Slack = -600ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1576      | 3111.920 | 11      |

| Buffer      | 361       | 1217.720 | 4.3     |

| Logic       | 6048      | 18129.72 | 64.1    |

| Sequential  | 910       | 5825.4   | 20.60   |

| Total       | 8895      | 28284.76 | 100     |

Table 5.38: Shows clock period 700ps with timing Violation of -600ps.

# • Clock Period = 800ps \*Timing Slack = -547ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1725      | 3473.96  | 11.2    |

| Buffer      | 438       | 1643.32  | 5.3     |

| Logic       | 6617      | 19972.4  | 64.7    |

| Sequential  | 910       | 5803.28  | 18.8    |

| Total       | 9690      | 30892.96 | 100     |

Table 5.39: Shows clock period 800ps with timing Violation of -547ps.

# • Clock Period = 900ps \*Timing Slack = -453ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1873      | 3775.52  | 12.4    |

| Buffer      | 413       | 1392.44  | 4.6     |

| Logic       | 6432      | 19384.12 | 63.80   |

| Sequential  | 910       | 5821.76  | 19.2    |

| Total       | 9628      | 30373.84 | 100     |

Table 5.40: Shows clock period 900ps with timing Violation of -453ps.

## • Clock Period = 1000ps \*Timing Slack = -314ps (Timing Violation)

| Gates(Type) | Instances | Area      | Area(%) |

|-------------|-----------|-----------|---------|

| Inverter    | 1704      | 3131.52   | 10.9    |

| Buffer      | 410       | 1529.08   | 5.3     |

| Logic       | 6129      | 18216.24  | 63.60   |

| Sequential  | 910       | 5756.52   | 20.1    |

| Total       | 9153      | 28633.360 | 100     |

Table 5.41: Shows clock period 1000ps with timing Violation of -314ps.

### • Clock Period = 1100ps \*Timing Slack = -197ps (Timing Violation)

| Gates(Type) | Instances | Area     | Area(%) |

|-------------|-----------|----------|---------|

| Inverter    | 1804      | 3186.12  | 11      |

| Buffer      | 454       | 1578.08  | 5.5     |

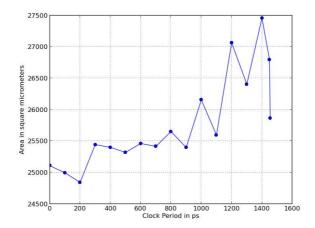

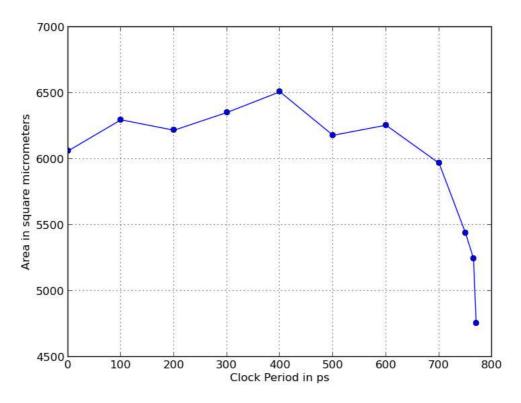

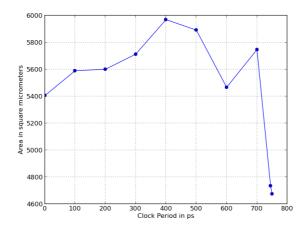

| Logic       | 6007      | 18389.56 | 63.60   |