# CONTROL AND OPERATION OF UNIFIED POWER QUALITY CONDITIONER WITH BATTERY-ULTRACAPACITOR ENERGY STORAGE SYSTEM

A Project Report

submitted by

## NAFIH MUHAMMAD I

in partial fulfilment of the requirements

for the award of the degree of

#### **MASTER OF TECHNOLOGY**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS.

MAY 2014

THESIS CERTIFICATE

This is to certify that the thesis titled **CONTROL AND OPERATION OF UNIFIED**

POWER QUALITY CONDITIONER WITH BATTERY-ULTRACAPACITOR EN-

ERGY STORAGE SYSTEM, submitted by NAFIH MUHAMMAD I, to the Indian

Institute of Technology, Madras, for the award of the degree of Master of Technology,

is a bona fide record of the research work done by him under my supervision. The con-

tents of this thesis, in full or in parts, have not been submitted to any other Institute or

University for the award of any degree or diploma.

Dr. Mahesh Kumar

(Project Guide)

Professor

Dept. of Electrical Engineering

IIT-Madras, 600 036

Place: Chennai

Date: 13th May 2014

## **ACKNOWLEDGEMENTS**

I take this opportunity to express my profound gratitude and deep regards to my project guide Prof. Mahesh Kumar for his excellent guidance, motivation and constant encouragement throughout my project. I consider myself extremely fortunate to have had a chance to work under his supervision. In spite of his hectic schedule he was always approachable and took his time off to discuss problems and give his advice. It has been a very learning and enjoyable experience to work under him.

I am also grateful for the laboratory facilities provided by him in the Power Quality Simulation Laboratory, ESB 342, Department of Electrical Engineering, which facilitated my simulation work.

My appreciation to my fellow research scholars in the Power Simulation Laboratory for spending their invaluable time with me, in discussing about the project and answering my queries. I am particularly grateful to Nagesh, Manojkumar, Narasa Reddy, Suma, Sijo and Chandan for their support during my work.

I would like to extend my thanks to my friends for their companionship and encouragement which made my stay in IIT Madras campus, a memorable one.

This work could not have come to this stage without the support and encouragement from my family. My heartfelt thanks to all of them.

## **ABSTRACT**

KEYWORDS: UPQC; Battery-Ultracapacitor Hybrid; DC/DC Converters; Power Quality;

Power Quality (PQ) can be defined as a set of electrical boundaries that makes an equipment to function in its intended manner without significant loss of performance. UPQC has been widely studied by researchers to mitigate the disturbances propagated from source side and load side. It simultaneously mitigates the current disturbance in load side and voltage disturbance in source side. However it cannot compensate the voltage interruption because it has no energy storage devices connected in the DC link.

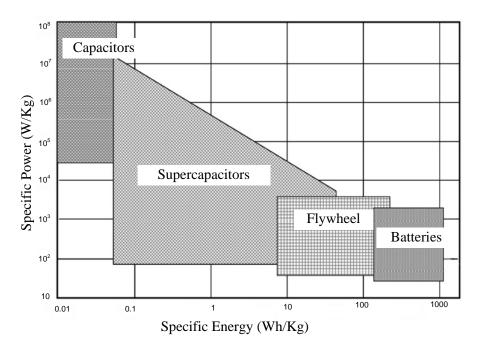

An ultracapacitor also referred to as supercapacitor stores charge in a double layer formed on a large surface area of micro porous materials such as activated carbon. The rate of discharge of ultracapacitor is faster than battery ranging from 0.3s to 30s. The lead acid rechargeable battery has high specific energy and a lower specific power compared to ultracapacitor. A combination of ultracapacitor and battery can take advantage of each kind of device to yield a power source which has both high power density and high energy density. Research on hybrid power sources shows that the combination of battery and ultracapacitor achieves a higher power capability and a longer run time compared to battery or ultracapacitor alone under a pulsed load condition.

The purpose of this thesis is to research the combined operation of UPQC and battery supercapacitor hybrid. This thesis proposes new configuration of UPQC that consists of battery and ultracapacitor connected to DC link through DC/DC converters for compensating the voltage interruption. The operation of proposed system was verified through simulations with Matlab/Simulink.

# TABLE OF CONTENTS

| LIST OF TABLES |               |            |                                       |      |  |  |  |  |  |

|----------------|---------------|------------|---------------------------------------|------|--|--|--|--|--|

| Ll             | IST O         | F FIGU     | URES                                  | viii |  |  |  |  |  |

| A              | ABBREVIATIONS |            |                                       |      |  |  |  |  |  |

| N              | OTAT          | ION        |                                       | X    |  |  |  |  |  |

| 1              | INT           | TRODUCTION |                                       |      |  |  |  |  |  |

|                | 1.1           | Electri    | ric Power Quality and Mitigation      | . 1  |  |  |  |  |  |

|                |               | 1.1.1      | Custom Power Devices                  | . 2  |  |  |  |  |  |

|                | 1.2           | Energy     | gy storage Devices                    | . 4  |  |  |  |  |  |

|                |               | 1.2.1      | Chemical Energy Storage               | . 4  |  |  |  |  |  |

|                |               | 1.2.2      | Electrochemical Energy Storage        | . 4  |  |  |  |  |  |

|                |               | 1.2.3      | Electrical Energy Storage             | . 5  |  |  |  |  |  |

|                |               | 1.2.4      | Thermal Energy Storage                | . 5  |  |  |  |  |  |

|                |               | 1.2.5      | Mechanical Energy Storage             | . 5  |  |  |  |  |  |

|                | 1.3           | Proble     | em Definition                         | . 6  |  |  |  |  |  |

|                | 1.4           | Object     | etives and Scope                      | . 6  |  |  |  |  |  |

|                | 1.5           | Organi     | nisation of Thesis                    | . 7  |  |  |  |  |  |

| 2              | LIT           | ERATU      | URE REVIEW                            | 9    |  |  |  |  |  |

|                | 2.1           | Introd     | luction to Power Quality              | . 9  |  |  |  |  |  |

|                |               | 2.1.1      | Power Quality Problems                | . 10 |  |  |  |  |  |

|                |               | 2.1.2      | Power Quality Terminology             | . 10 |  |  |  |  |  |

|                |               |            | 2.1.2.1 <i>Flicker</i>                | . 10 |  |  |  |  |  |

|                |               |            | 2.1.2.2 Power frequency               | . 11 |  |  |  |  |  |

|                |               |            | 2.1.2.3 <i>Voltage sag</i>            | . 11 |  |  |  |  |  |

|                |               |            | 2.1.2.4 <i>Voltage swell</i>          | . 12 |  |  |  |  |  |

|                |               |            | 2.1.2.5 <i>Momentary interruption</i> | . 12 |  |  |  |  |  |

|   |     |         | 2.1.2.6     | Sustained interruption                                        | 12 |

|---|-----|---------|-------------|---------------------------------------------------------------|----|

|   |     |         | 2.1.2.7     | Temporary interruption                                        | 12 |

|   |     |         | 2.1.2.8     | Voltage unbalance                                             | 13 |

|   |     |         | 2.1.2.9     | Harmonics                                                     | 13 |

|   |     |         | 2.1.2.10    | DC offset                                                     | 14 |

|   |     |         | 2.1.2.11    | Interharmonics                                                | 14 |

|   |     |         | 2.1.2.12    | Transient                                                     | 14 |

|   |     |         | 2.1.2.13    | Notching                                                      | 14 |

|   |     |         | 2.1.2.14    | <i>Noise</i>                                                  | 15 |

|   | 2.2 | Unifie  | d Power Q   | uality Conditioner (UPQC)                                     | 15 |

|   |     | 2.2.1   | Power C     | ircuit Topologies of UPQC                                     | 15 |

|   |     |         | 2.2.1.1     | Classification based on the converter topology                | 18 |

|   |     |         | 2.2.1.2     | Classification based on the supply system                     | 19 |

|   |     |         | 2.2.1.3     | Classification based on the UPQC configuration .              | 22 |

|   |     |         | 2.2.1.4     | Classification based on the voltage sag compensation approach | 24 |

|   |     | 2.2.2   | Control 7   | Techniques For UPQC                                           | 26 |

|   |     |         | 2.2.2.1     | Instantaneous reactive power theory                           | 26 |

|   |     |         | 2.2.2.2     | Synchronous reference frame theory                            | 29 |

|   |     |         | 2.2.2.3     | Instantaneous symmetrical components theory                   | 31 |

|   |     | 2.2.3   | UPQC fo     | or Compensating Voltage Interruption                          | 33 |

|   | 2.3 | Parame  | eters Influ | encing Battery Performance                                    | 35 |

|   |     | 2.3.1   | Capacity    | of Battery                                                    | 35 |

|   |     | 2.3.2   | Battery I   | ife                                                           | 36 |

|   |     | 2.3.3   | Power D     | ensity and Energy Density                                     | 36 |

|   | 2.4 | Battery | y Supercap  | pacitor Hybrid                                                | 37 |

|   | 2.5 | Summ    | ary         |                                                               | 39 |

| 3 | DES | SIGN A  | ND CONT     | TROL OF UPQC                                                  | 41 |

|   | 3.1 | Design  | of DC Li    | nk Capacitor                                                  | 41 |

|   | 3.2 | Design  | and Cont    | rol of Shunt APF                                              | 43 |

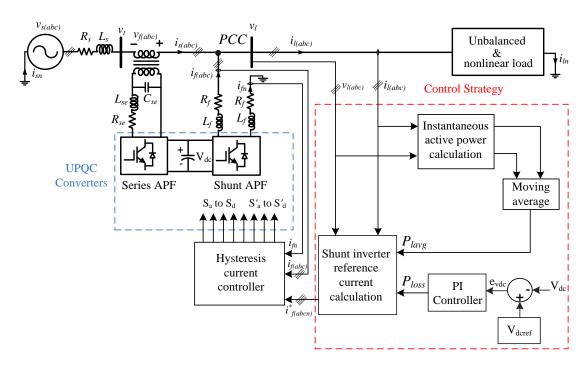

|   |     | 3.2.1   | Reference   | e Current Generation                                          | 43 |

|   |     |         | 3.2.1.1     | Instantaneous symmetrical component theory                    | 43 |

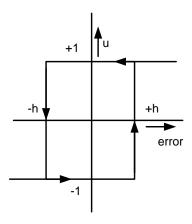

|   |     | 3.2.2                                                               | Hysteresis Based PWM Controller                                       | 48 |

|---|-----|---------------------------------------------------------------------|-----------------------------------------------------------------------|----|

|   |     | 3.2.3                                                               | Shunt Interface Inductor                                              | 49 |

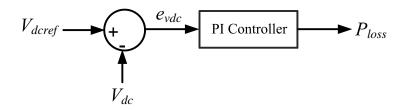

|   |     | 3.2.4                                                               | Control of Shunt Inverter                                             | 50 |

|   | 3.3 | Design                                                              | n and Control of Series APF                                           | 5  |

|   |     | 3.3.1                                                               | Reference Voltage Generation                                          | 5  |

|   |     | 3.3.2                                                               | Sag/Swell Detection                                                   | 5  |

|   |     | 3.3.3                                                               | PWM Gate Signal Generation                                            | 5  |

|   |     | 3.3.4                                                               | LC Low Pass Filter                                                    | 5  |

|   |     | 3.3.5                                                               | Control of Series Inverter                                            | 5  |

|   | 3.4 | Summ                                                                | ary                                                                   | 5  |

| 4 | МО  | DELLI                                                               | NG OF BATTERY AND SUPERCAPACITOR                                      | 5  |

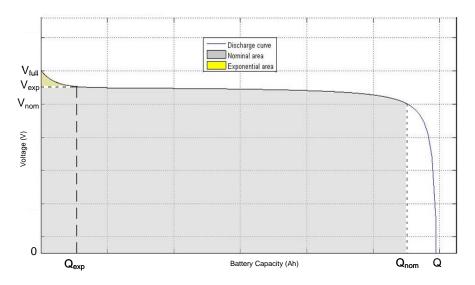

|   | 4.1 | Batter                                                              | y Modelling                                                           | 5  |

|   |     | 4.1.1                                                               | The Charge Model                                                      | 5  |

|   |     | 4.1.2                                                               | The Discharge Model                                                   | 6  |

|   |     | 4.1.3                                                               | Model Assumptions and Limitations                                     | 6  |

|   |     | 4.1.4                                                               | Battery Model Parameters                                              | 6  |

|   | 4.2 | Supero                                                              | capacitor Modelling                                                   | 6  |

|   |     | 4.2.1                                                               | Self Discharge of Supercapacitor                                      | 6  |

|   |     | 4.2.2                                                               | Complete Super Capacitor Model                                        | 6  |

|   | 4.3 | Param                                                               | eter Selection of Bidirectional Converter                             | 7  |

|   | 4.4 | Summ                                                                | ary                                                                   | 7  |

| 5 |     | )POSE<br>)RAGE                                                      | D UPQC WITH BATTERY-ULTRACAPACITOR HYBRID                             | 7  |

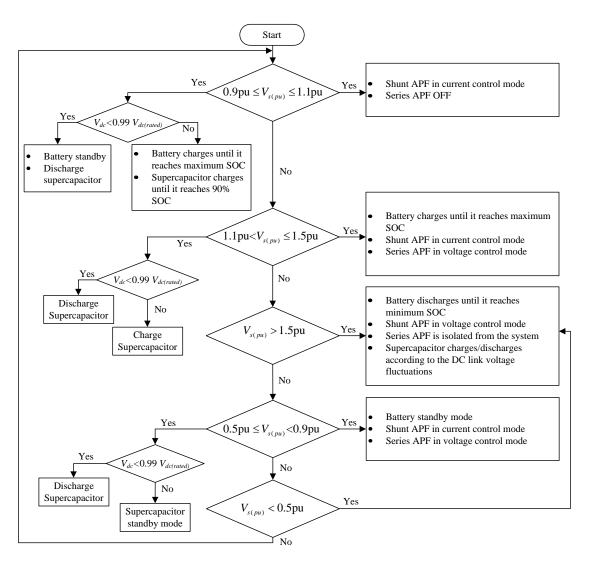

|   | 5.1 | Metho<br>Storag                                                     | edology of UPQC Operation with Battery Ultracapacitor Energy se       | 7  |

|   | 5.2 | 5.2 Grid Connected Mode of UPQC with Battery Ultracapacitor Storage |                                                                       |    |

|   |     | 5.2.1                                                               | Control of Battery and Ultracapacitor During Normal Voltage Condition | 7  |

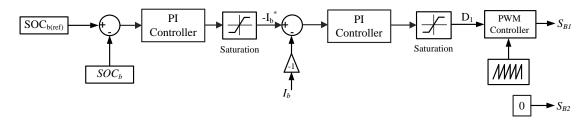

|   |     |                                                                     | 5.2.1.1 Control of battery charging                                   | 7  |

|   |     |                                                                     | 5.2.1.2 Control of supercapacitor DC/DC converter                     | 7  |

|   |     | 5.2.2                                                               | Control of Battery and Ultracapacitor During Voltage Sag .            | 7  |

|   |     | 523                                                                 | Control of Battery and Ultracapacitor During Voltage Swell            | Q  |

|   |                                                                                          | 5.2.4  | Complete Control Strategy in Grid Connected Mode                     | 80  |

|---|------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------|-----|

|   | 5.3 Operation of UPQC with Battery-Ultracapacitor Storage in Voltag terruption Condition |        | • • •                                                                | 80  |

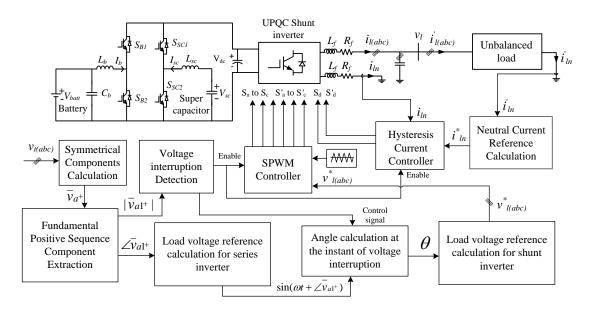

|   |                                                                                          | 5.3.1  | Shunt Inverter Control During Voltage Interruption                   | 82  |

|   |                                                                                          | 5.3.2  | Control of Battery Ultracapacitor Hybrid During Voltage Interruption | 84  |

|   | 5.4                                                                                      | Summ   | ary                                                                  | 86  |

| 6 | SIM                                                                                      | ULATI  | ON RESULTS                                                           | 87  |

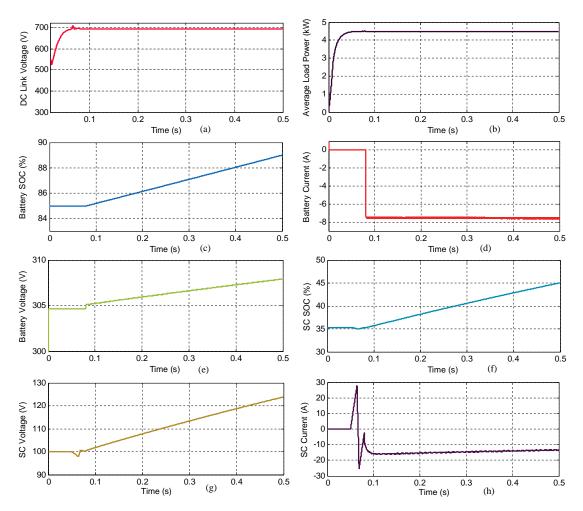

|   | 6.1                                                                                      | Grid C | onnected UPQC and Battery-Ultracapacitor Operation                   | 87  |

|   |                                                                                          | 6.1.1  | Normal Voltage Operation                                             | 87  |

|   |                                                                                          | 6.1.2  | Operation During Voltage Sag                                         | 90  |

|   |                                                                                          | 6.1.3  | Operation During Voltage Swell                                       | 93  |

|   | 6.2                                                                                      | UPQC   | and Battery-Ultracapacitor Operation in Voltage Interruption         | 95  |

|   |                                                                                          | 6.2.1  | Simulation with Constant Load                                        | 95  |

|   |                                                                                          | 6.2.2  | Simulation with Load Change                                          | 97  |

| 7 | CO                                                                                       | NCLUS  | ION AND FUTURE SCOPE                                                 | 101 |

|   | 7.1                                                                                      | Conclu | asion                                                                | 101 |

|   | 7.2                                                                                      | Future | Scope                                                                | 102 |

# LIST OF TABLES

| 2.1 | Battery and Supercapacitor Comparison                    | 38 |

|-----|----------------------------------------------------------|----|

| 4.1 | Parameters Considered for Battery Characteristics        | 64 |

| 4.2 | Parameters Considered for Supercapacitor Characteristics | 69 |

| 4.3 | L and $C$ values of DC/DC converters                     | 72 |

| 6.1 | Parameter values for simulation study                    | 88 |

| 6.2 | $K_p$ and $K_i$ values for simulation study              | 95 |

| 6.3 | Loads for simulation study                               | 97 |

## LIST OF FIGURES

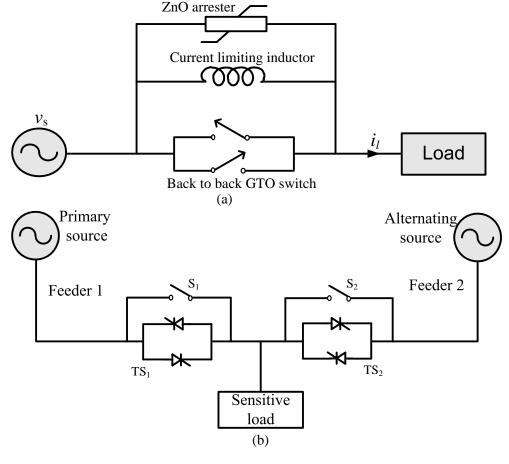

| 1.1  | Schematic diagram of: (a) SSCL (b) SS1S [18]                                                              | 3  |

|------|-----------------------------------------------------------------------------------------------------------|----|

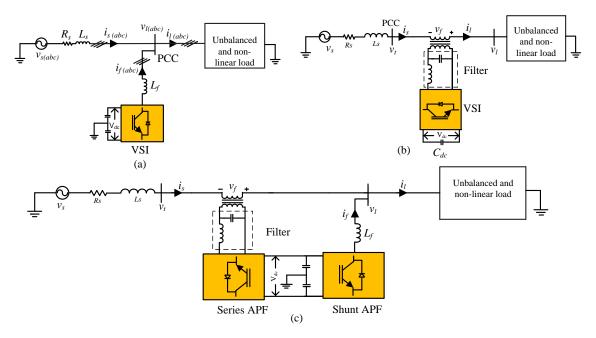

| 1.2  | Schematic diagram of compensating type custom power devices: (a) DSTATCOM (b) DVR (c) UPQC                | 4  |

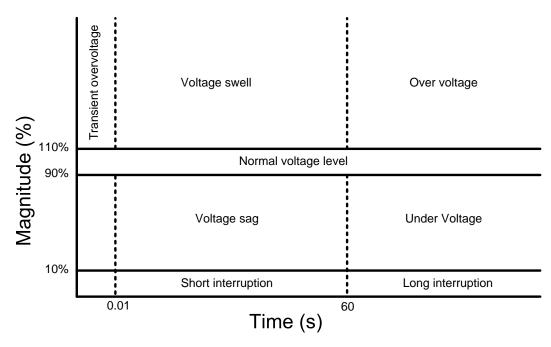

| 2.1  | Distribution of voltage problems                                                                          | 13 |

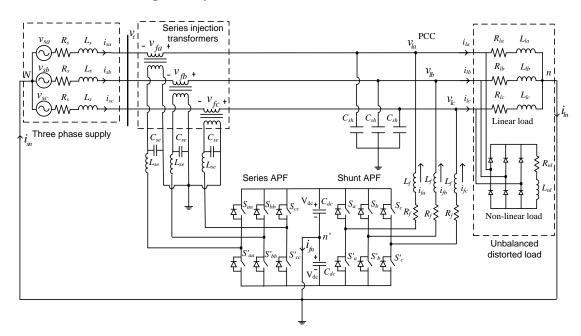

| 2.2  | Power circuit of three phase UPQC                                                                         | 16 |

| 2.3  | Classification of UPQC                                                                                    | 19 |

| 2.4  | CSI based UPQC system configuration                                                                       | 19 |

| 2.5  | VSI based UPQC system configuration                                                                       | 20 |

| 2.6  | $1\phi 2W$ UPQC: (a) Two H-bridge configuration (b) Three leg configuration (c) Half bridge configuration | 20 |

| 2.7  | Power circuit of $3\phi 3W$ UPQC                                                                          | 21 |

| 2.8  | $3\phi 4W$ UPQC based on four leg shunt inverter topology                                                 | 22 |

| 2.9  | $3\phi 4W$ UPQC based on H-bridge shunt inverter topology                                                 | 22 |

| 2.10 | Schematic diagram of left shunt UPQC                                                                      | 23 |

| 2.11 | UPQC configurations: (a) Interline UPQC (b) Multi-converter UPQC.                                         | 23 |

| 2.12 | UPQC-DG system configuration                                                                              | 25 |

| 2.13 | $abc$ to $\alpha\beta$ reference frame                                                                    | 27 |

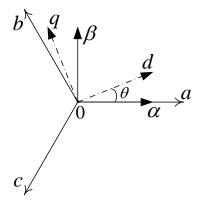

| 2.14 | dq0 reference frame                                                                                       | 30 |

| 2.15 | UPQC system interconnected with energy storage                                                            | 34 |

| 2.16 | Specific power Vs specific energy ranges for different storage elements [1]                               | 37 |

| 3.1  | Power circuit of three phase UPQC                                                                         | 42 |

| 3.2  | PI controller for maintaining constant DC link voltage                                                    | 48 |

| 3.3  | Two-level hysteresis scheme                                                                               | 49 |

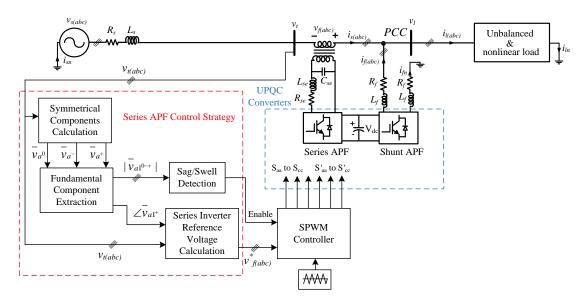

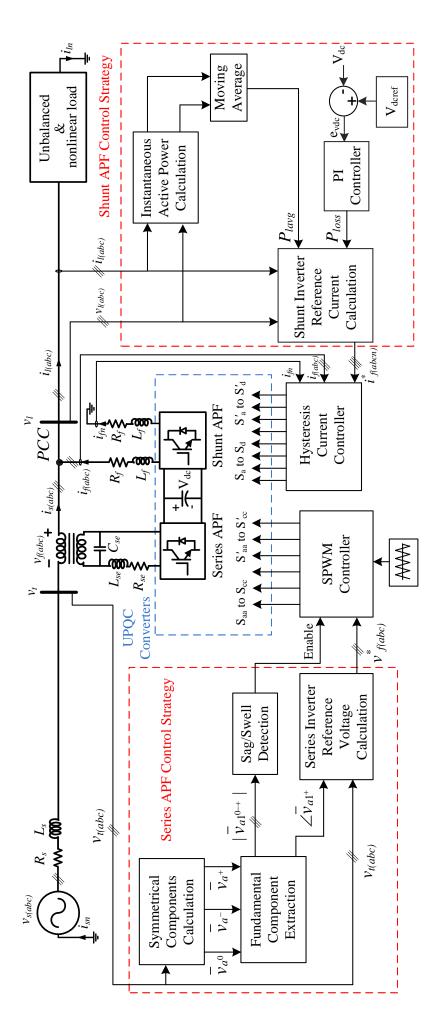

| 3.4  | Control strategy of shunt APF                                                                             | 50 |

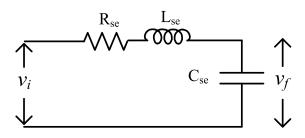

| 3.5  | LC low pass filter                                                                                        | 55 |

| 3.6  | Control strategy of series APF                                                                            | 57 |

| 3.7  | Control strategy of UPQC                                                                                  | 58 |

| 4.1 | Typical discharge curve of lead-acid battery                                                                                                                                                                                                      | 61 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

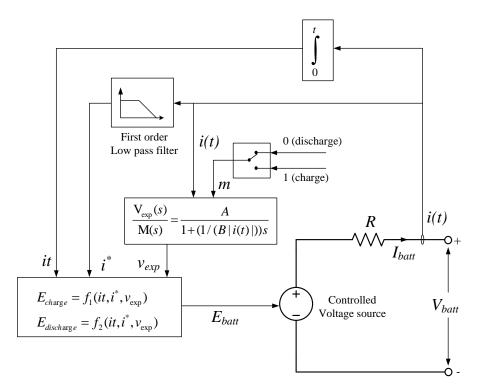

| 4.2 | Battery model [2]                                                                                                                                                                                                                                 | 62 |

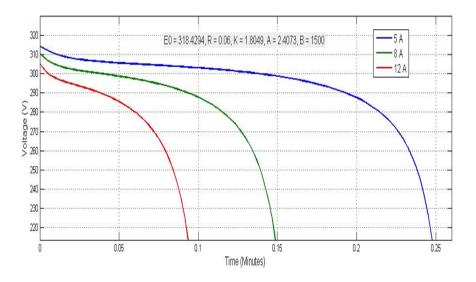

| 4.3 | Discharge curve of lead acid battery [3]                                                                                                                                                                                                          | 64 |

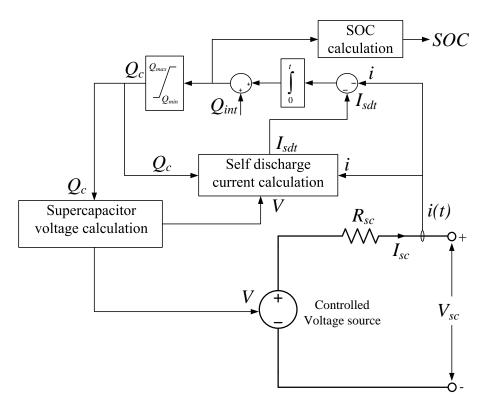

| 4.4 | Supercapacitor model                                                                                                                                                                                                                              | 68 |

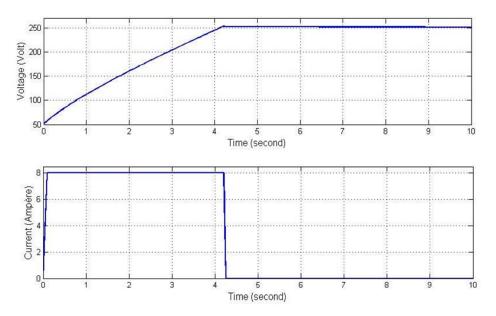

| 4.5 | Supercapacitor voltage and current as a function of time [3]                                                                                                                                                                                      | 70 |

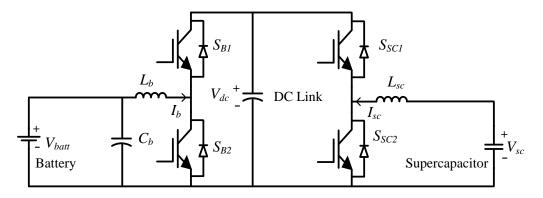

| 4.6 | Bidirectional buck-boost converter for battery-supercapacitor hybrid.                                                                                                                                                                             | 71 |

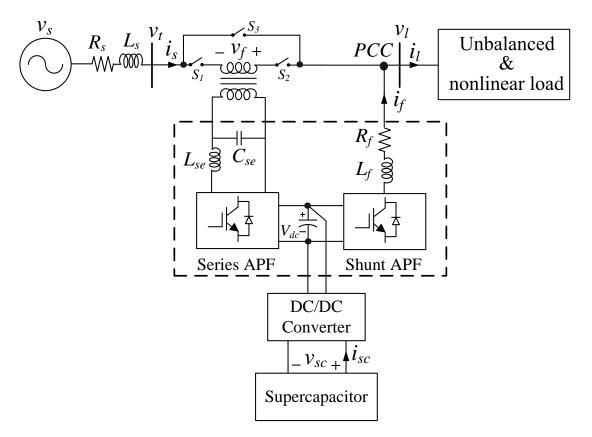

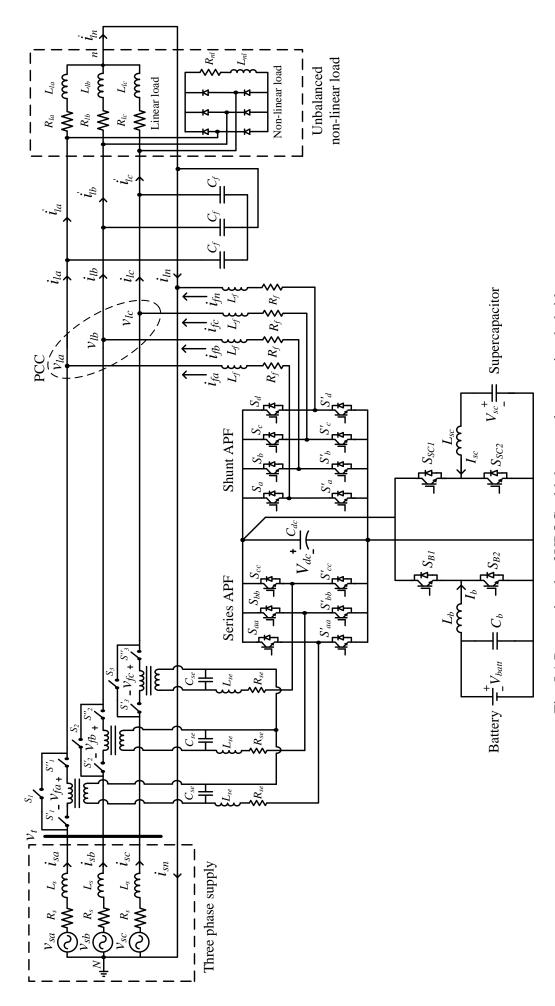

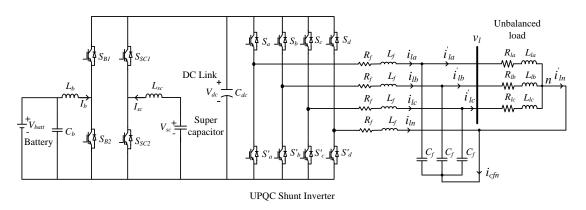

| 5.1 | Power circuit of UPQC with battery ultracapacitor hybrid                                                                                                                                                                                          | 74 |

| 5.2 | Methodology of UPQC operation with battery supercapacitor energy storage                                                                                                                                                                          | 77 |

| 5.3 | Control of battery charging                                                                                                                                                                                                                       | 78 |

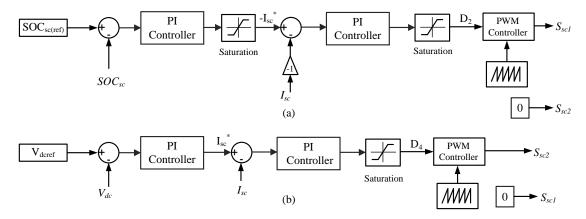

| 5.4 | Control of supercapacitor DC/DC converter for: (a) supercapacitor charging (b) supercapacitor discharging                                                                                                                                         | 79 |

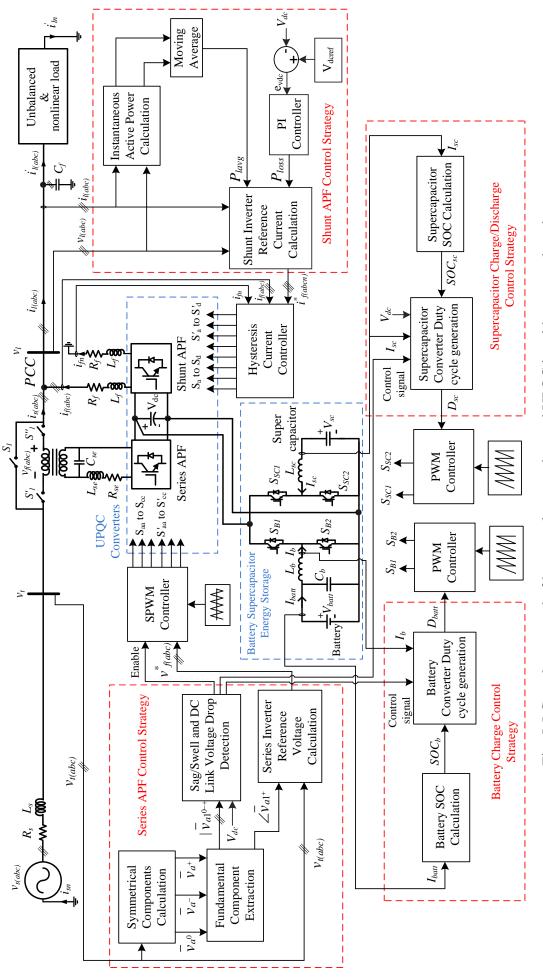

| 5.5 | Complete control of battery, ultracapacitor and UPQC in grid connected mode                                                                                                                                                                       | 81 |

| 5.6 | Power circuit of whole system during voltage interruption                                                                                                                                                                                         | 82 |

| 5.7 | Complete shunt inverter control during voltage interruption                                                                                                                                                                                       | 84 |

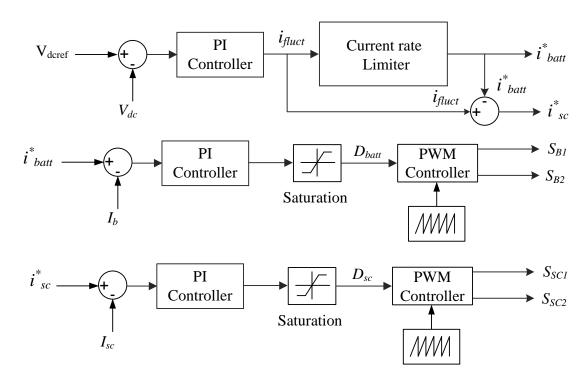

| 5.8 | Control of battery-ultracapacitor DC/DC converters during voltage interruption                                                                                                                                                                    | 85 |

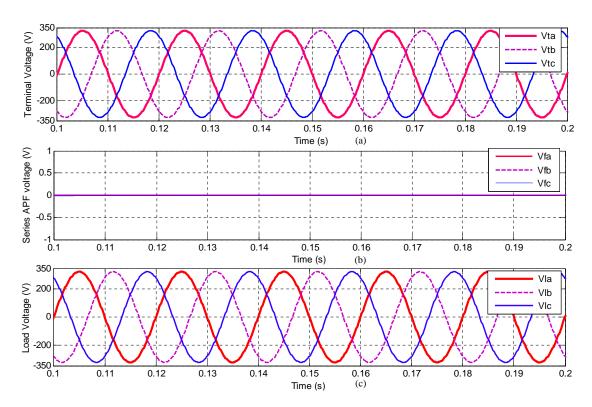

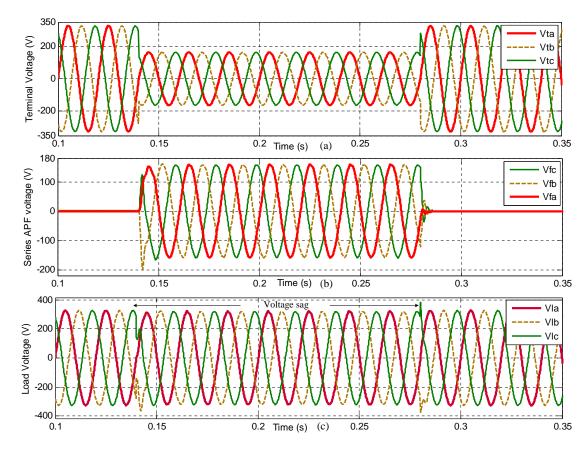

| 6.1 | (a) Source terminal voltage (b) Series inverter injected voltage (c) Load voltage                                                                                                                                                                 | 89 |

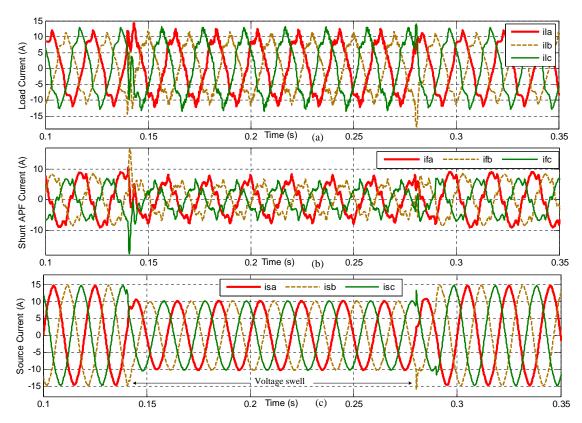

| 6.2 | (a) Source current (b) Shunt inverter injected current (c) Load current.                                                                                                                                                                          | 89 |

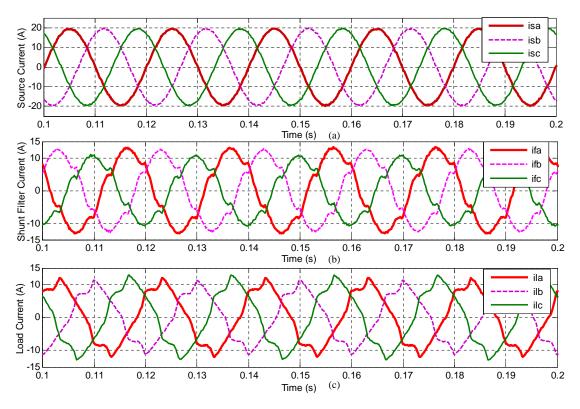

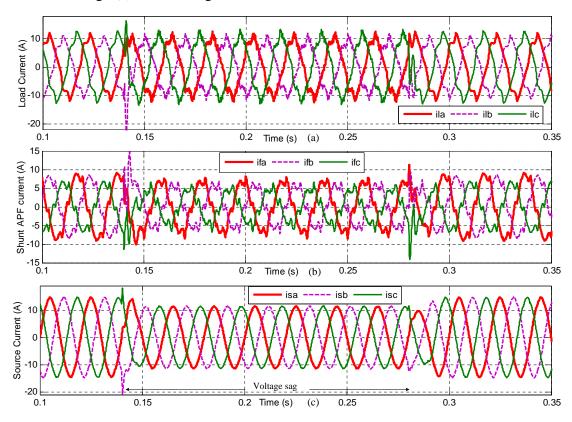

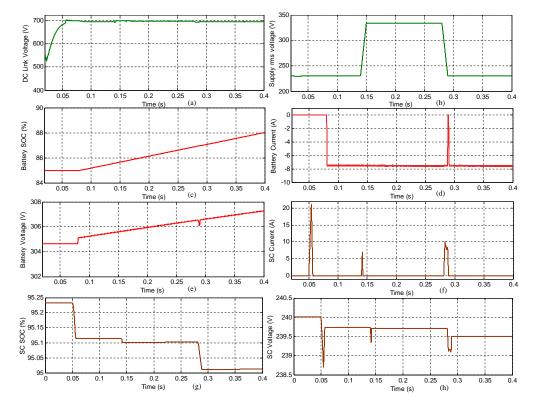

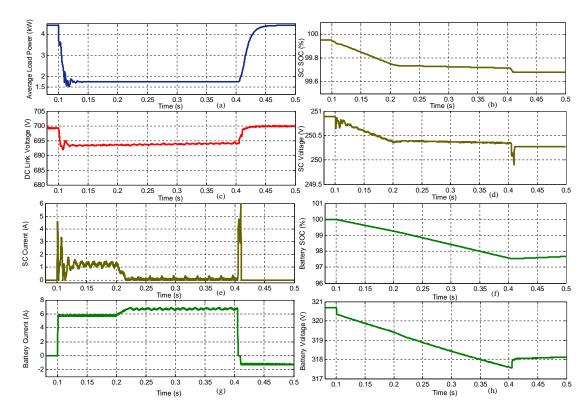

| 6.3 | Normal voltage operation: (a) DC link voltage (b) Average load power (c) Battery SOC (d) Battery current (e) Battery terminal voltage(f) Supercapacitor SOC (g) Supercapacitor terminal voltage (h) Supercapacitor discharge current.             | 90 |

| 6.4 | Voltages during sag: (a) Source terminal voltage (b) Series inverter injected voltage (c) Load voltage                                                                                                                                            | 91 |

| 6.5 | Currents during sag: (a) Load current (b) Shunt inverter current (c) Source current                                                                                                                                                               | 91 |

| 6.6 | Operation during sag: (a) DC link voltage (b) Source voltage magnitude variation (c) Battery current (d) Battery terminal voltage (e) Battery SOC (f) Supercapacitor SOC (g) Supercapacitor terminal voltage (h) Supercapacitor discharge current | 92 |

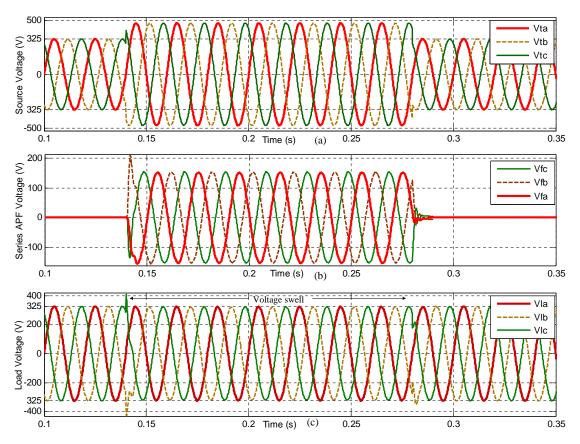

| 6.7 | Voltages during swell: (a) Source terminal voltage (b) Series inverter injected voltage (c) Load voltage                                                                                                                                          | 93 |

| 6.8 | Currents during swell: (a) Load current (b) Shunt inverter current (c)                                                                                                                                                                            | 94 |

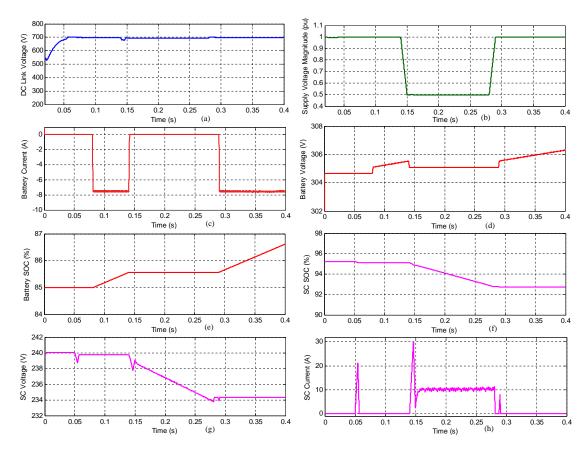

| 6.9  | Operation during swell: (a) DC link voltage (b) Source phase voltage variation (c) Battery SOC (d) Battery current (e) Battery terminal voltage (f) Supercapacitor discharge current (g) Supercapacitor SOC (h) Supercapacitor terminal voltage                        | 94 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

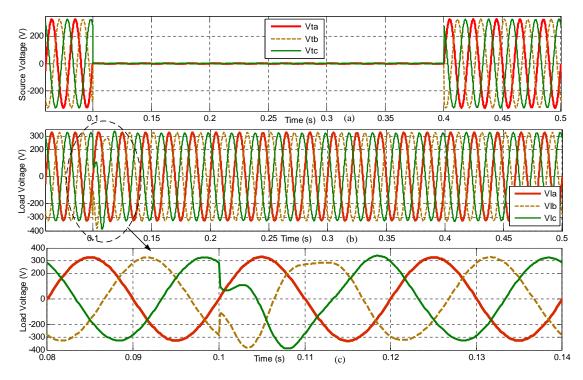

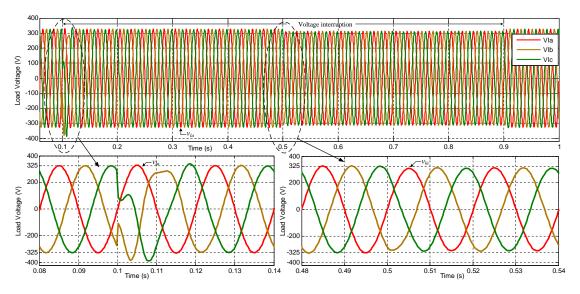

| 6.10 | Voltages during supply interruption: (a) Source terminal voltage (b) Load voltage (c) Load voltage variation from 0.08 s to 0.14 s                                                                                                                                     | 96 |

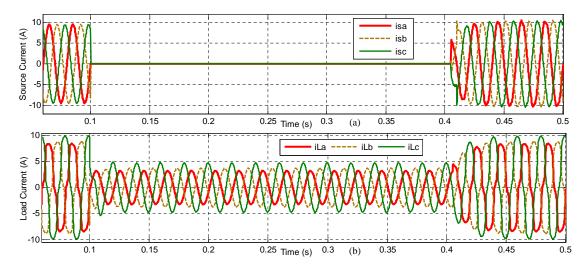

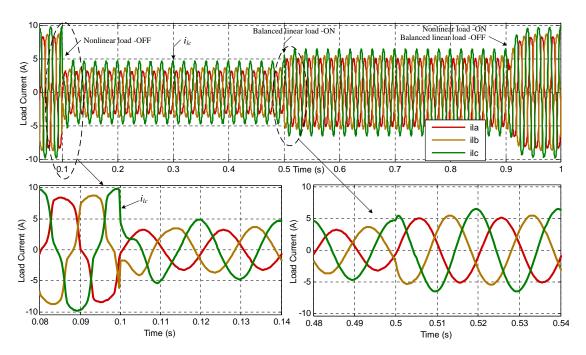

| 6.11 | Currents during supply interruption: (a) Source current (b) Load current                                                                                                                                                                                               | 96 |

| 6.12 | Operation during voltage interruption: (a) Average load power variation (b) Supercapacitor SOC (c) DC link voltage (d) Supercapacitor terminal voltage (e) Supercapacitor discharge current (f) Battery SOC (g) Battery discharge current (h) Battery terminal voltage | 97 |

| 6.13 | Load voltage variation during source voltage interruption                                                                                                                                                                                                              | 98 |

| 6.14 | Load current variation during source voltage interruption                                                                                                                                                                                                              | 98 |

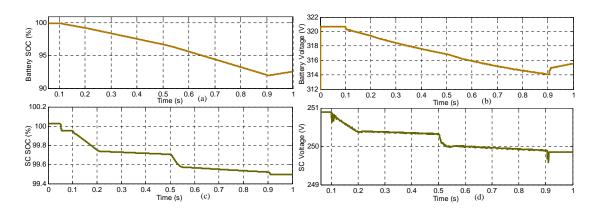

| 6.15 | (a) Battery SOC variation (b) Battery terminal voltage (c) Supercapacitor SOC variation (d) Supercapacitor voltage.                                                                                                                                                    | 99 |

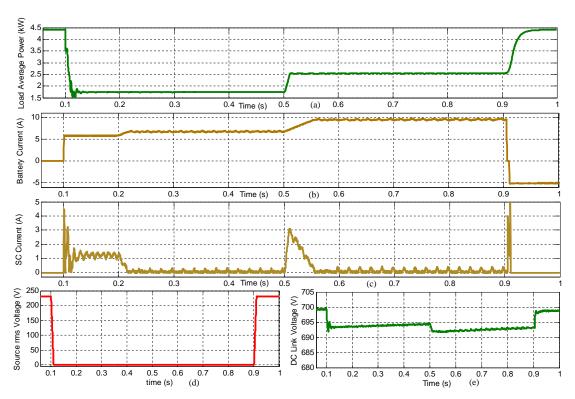

| 6.16 | (a) Average load power variation (b) Battery discharge current (c) Supercapacitor discharge current (d) Source rms voltage variation (e) DC link voltage                                                                                                               | 00 |

## **ABBREVIATIONS**

**UPQC** Unified Power Quality Conditioner

SC Super Capacitor

**IEEE** Institute of Electrical and Electronics Engineers

**IEC** International Electrotechnical Commission

**PQ** Power Quality

**APF** Active Power Filter

PI Proportional and Integral

**DC** Direct Current

**PCC** Point of Common Coupling

VSI Voltage Source Inverter

**PWM** Pulse Width Modulation

**THD** Total Harmonic Distortion

**GTO** Gate Turn Off thyristor

**SSCL** Solid State Current Limiter

**SSCB** Solid State Circuit Breaker

**SSTS** Solid State Transfer Switch

**DSTATCOM** Distribution STATic COMpensator

**DVR** Dynamic Voltage Restorer

**CSI** Current Source Inverter

**IGBT** Insulated Gate Bipolar Transistor

VA Volt Ampere

**DG** Distributed Generation

PLL Phase Locked Loop

**OCC** One Cycle Control

**SOC** State Of Charge

**DER** Distributed Energy Resources

## **NOTATION**

Instantaneous voltages in  $\alpha\beta\theta$  frame, V $v_{\alpha}, v_{\beta}, v_{0}$ Instantaneous voltages in dq0 frame, V  $v_d, v_q, v_0$ Source terminal voltages in phase-a, b and c respectively, V  $v_{ta}, v_{tb}, v_{tc}$ Source voltages in phase-a, b and c respectively, V $v_{sa}, v_{sb}, v_{sc}$ Series inverter voltages in phase-a, b and c respectively, V  $v_{fa}, v_{fb}, v_{fc}$ Three phase load voltages, V  $v_{la}, v_{lb}, v_{lc}$  $i_{sa}, i_{sb}, i_{sc}$ Three phase source current, A Three phase shunt inverter current, A  $i_{fa}, i_{fb}, i_{fc}$ Shunt APF neutral current, A  $i_{fn}$ Filter capacitance connected at load terminal, mF $C_f$ Current drawn by connected load and  $C_f$  in phase-a, b and c respectively, A  $i_{la}, i_{lb}, i_{lc}$ Three phase current drawn by connected load, A  $i_{la}, i_{lb}, i_{lc}$ Instantaneous active power, WInstantaneous reactive power, var q $R_s, L_s$ Feeder resistance and inductance,  $\Omega$ , mH $R_f, L_f$ Shunt inverter filter resistance and inductance,  $\Omega$ , mHLC filter inductance and capacitance of series APF, mH,  $\mu F$  $L_{se}, C_{se}$ DC link voltage, V  $V_{dc}$ DC link capacitance,  $\mu F$  $C_{dc}$ Instantaneous symmetrical components in phase a, V  $v_{a0}, v_{a1}, v_{a2}$ Average load power, W $P_{lavg}$  $V_{ta1}^+$ Fundamental positive sequence component of terminal voltage, V Phase angle of fundamental positive sequence terminal voltage, rad  $-\theta_1$  $SOC_b, SOC_{sc}$ SOC of battery and supercapacitor respectively  $V_{batt}, V_{sc}$ Voltage across battery and supercapacitor respectively, V Discharge current of battery and ultracapacitor respectively, A  $I_b, I_{sc}$  $L_b, C_b$ Battery converter inductance and capacitance respectively, mH,  $\mu F$  $L_{sc}$ Supercapacitor converter inductance, mHQMaximum capacity of battery, Ah  $V_{exp}, Q_{exp}$ Exponential zone voltage and capacity of battery, V, Ah Nominal voltage and capacity of battery, V, Ah $V_{nom}, Q_{nom}$ Fully charged voltage of battery, V $V_{full}$  $Q_c$ supercapacitor charge, C Self discharging current of supercapacitor, mA $I_{sd}$  $\Delta V$ Over-potential, VDDuty cycle Rated rms load voltage, V  $V_l$

Hysteresis band Frequency, rad/s

Angle to synchronize load voltage at interruption and source voltage, rad

$\theta$

h

$\omega$

## **CHAPTER 1**

## INTRODUCTION

In the current scenario of power industry, both consumers and power suppliers are obliged to comply with different Power Quality (PQ) standards proposed by international bodies such as IEC and IEEE. Power Quality is defined as the concept of powering and grounding electronic equipment in a manner that is suitable to the operation of that equipment and compatible with the premise wiring system and other connected equipment in IEEE standard 1159-1995. IEC defined power quality as set of parameters defining the properties of power quality as delivered to the user in normal operating conditions in terms of continuity of supply and characteristics of voltage (frequency, magnitude, waveform and symmetry). Power quality (PQ) depends not only on the supply system but can be strongly affected by the end users selection of equipments and installation practices.

## 1.1 Electric Power Quality and Mitigation

There are two major classes of power quality problems namely problems due to low quality of current drawn by the nonlinear loads and voltage fluctuations that caused by faults in the power system. The most significant and critical power quality problems are voltage sags, voltage swells and current harmonics [4]. These problems cause tripping of sensitive electronic equipment with dangerous consequences in industrial plants where tripping of a critical equipment can cause the stoppage of the whole production with high costs associated. As more sensitive loads such as automation equipments, communication equipments and computers have come into wide use, the power quality becomes a very big issue in the utility company and customer. These equipments are sensitive to the source voltage disturbances, the fault or inadequate operation of these loads brings about huge losses [5],[6].

#### 1.1.1 Custom Power Devices

To provide a flexible and active solution for PQ problems, many efforts have done from time to time. Among these PQ solutions lossless passive filters [7],[8] consists of L-C tuned component have been widely used to suppress harmonics. The advantages of passive filters over active filters are its low initial cost and high efficiency. On the other hand, it have various drawbacks such as fixed compensation, resonance with supply system and instability. To overcome these limitations active power filters (APF) [9],[10] have been widely used. APF has different configurations namely shunt, series and hybrid. Shunt APF is usually used for compensating current related distortions while series APF compensates voltage related distortions. Hybrid APF [11],[12] is used for filtering higher order harmonics. However it has a problem is that its rating is sometimes very close to load (up to 80% of load) in typical applications. PQ level cannot be obtained because of this reason.

To increase the reliability of distribution systems and mitigate the PQ problems, advanced power electronic controller devices have launched over last decades. The advent of power electronic devices has given birth to the custom power devices [13],[14]. Custom power devices uses power electronic controllers for power quality improvements on distribution systems. Their performance has been checked and demonstrated for isolated as well as grid connected distribution systems. Custom power devices are classified into network reconfiguring type and compensating type. The network reconfiguring type changes the configuration of the power system networks for PQ enhancement. Network reconfiguring type includes SSCL (Solid State Current Limiter) [15], SSCB (Solid State Circuit Breaker) [16] and SSTS (Solid State Transfer Switch) [17]. A pictorial representation of SSCL and SSTS are shown in Fig. 1.1(a) and Fig. 1.1(b) respectively [18]. SSCL uses a GTO that inserts an inductor in series with a power system network and limits the fault current, the inductor is removed from the circuit when the fault is cleared. SSCB is a protection device and it isolates the faulted circuit from the system. SSTS is used for rapid transfer of the load from a faulted line to an available alternative line to protect a sensitive load. The schematic diagram of SSTS is shown in . All of these are thyristor or GTO based devices.

The compensating type devices are mainly uses for load balancing, filtering, voltage regulation and power factor correction. The compensating devices include DVR

Fig. 1.1 Schematic diagram of : (a) SSCL (b) SSTS [18]

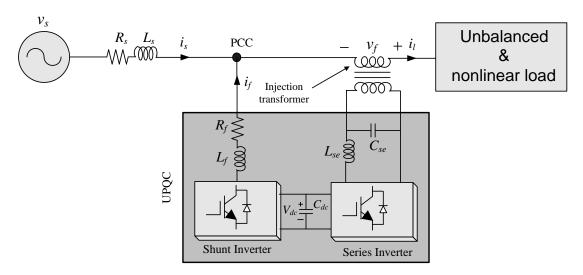

(Dynamic voltage restorer), DSTATCOM (Distribution Static compensator) and Unified power quality conditioner (UPQC). A DSTATCOM [19] configuration consists of a VSI, DC energy storage device (usually a capacitor) and a filter. Fig. 1.2(a) shows the schematic diagram of a DSTATCOM used for PQ problem compensation in a distribution system. In current control mode, DSTATCOM is used for elimination of current harmonics, power factor correction and compensation of reactive power of load. The DVR [20] is commonly used for voltage sag/swell mitigation, unbalanced voltage disturbance mitigation and elimination of voltage harmonics. The DVR uses the same blocks as the DSTATCOM, but in DVR the coupling transformer is connected in series with the ac supply system as shown in Fig. 1.2(b). The main functions of DVR are, compensation of voltage sag/swell, voltage regulation and unbalance voltage compensation. UPQC [21] uses for the mitigation of voltage and current related problems that could affect sensitive electrical loads, it also uses for compensating the load reactive power. It consist of both shunt and series active power filters for simultaneous compensation of current and voltage related PQ problems and load reactive power. The basic structure of UPQC is shown in Fig. 1.2(c).

Fig. 1.2 Schematic diagram of compensating type custom power devices: (a) DSTATCOM (b) DVR (c) UPQC.

## 1.2 Energy storage Devices

The way energy is stored in devices mainly depends on the source of energy. According to this, the following are the main methods of energy storage.

## 1.2.1 Chemical Energy Storage

Chemical energy is a form of potential energy, its storage depends on the source of energy. Hydrogen gas has potentials as a source of energy and it is primarily used as an energy storage medium for subsequent use. Examples are underground hydrogen storage which uses in the underground caverns, empty oil and gas fields to store grid energy for intermittent energy resources such as solar and wind energy.

## 1.2.2 Electrochemical Energy Storage

Electrochemical energy storage uses various devices which convert chemical energy into electrical energy. Examples include fuel cell and battery. Batteries are widely used devices that converts stored chemical energy into electrical energy. Two basic types of batteries are primary batteries or non-rechargeable batteries and secondary batteries or rechargeable batteries. Fuel cell converts chemical energy into electrical energy through

chemical reaction.

## 1.2.3 Electrical Energy Storage

In these kind of storage system, devices stores energy in its electric field. Examples include ultracapacitor, superconducting magnetic energy storage (SMES) and capacitor. Both ultracapacitor and capacitor are used to store electric charge, as its name reveals, ultracapacitor can store more electric charge than capacitor. Capacitor is used as a short time backup power, while ultracapacitor can also be used to power large systems including electric vehicles. SMES are relatively new technology which stores electric energy from the grid in its magnetic field created by the flow of current in a coil.

## 1.2.4 Thermal Energy Storage

It is a method that used to store thermal energy in order to use it to heat or cool buildings when the temperature inside is below or above the internal energy in the stored substance. Examples are storage heater, hot water storage tank and steam accumulator. Hot water storage tank are used to store hot water for washing, bathing, space heating etc. Storage heater is an electric heater that stores energy during the night or evening and releases the heat during day when the price of base load electricity is higher. Storage heaters accumulate heat in ceramic like materials. Steam accumulators uses a steel tank that contains steam under high pressure. It is used to balance supply and demand by accepting steam when the demand is less than supply and to release it when load demand exceeds the supply power.

## 1.2.5 Mechanical Energy Storage

Mechanical energy storage stores energy that is produced by motion including flywheel and hydraulic accumulator. Hydraulic accumulator is a kind of storage reservoir which stores non compressible fluid under pressure. The most widely used hydraulic accumulator is the compressed gas accumulator which store gas under pressure, usually nitrogen. Flywheel energy storage is used to store grid energy and energy generated by wind farms. It also shows potentials in transportation and as an emergency source of

## 1.3 Problem Definition

UPQC is a device that can simultaneously mitigate source side voltage disturbance and load side current disturbance. UPQC can compensate voltage sag/swell, current harmonics and harmonic voltage, and it can control the reactive power supplied by the source. However, it cannot compensate the voltage interruption because it has no energy storage devices connected to its DC link. The commonly used storage device is lead acid batteries, it possess low power density. The battery charge and discharge are slower and hence, it is not suitable for highly fluctuating load demand. The super capacitors are becoming popular for its high power density compared to battery and it can respond very quickly to high fluctuating power. But, the low energy density of super capacitor makes it not suitable to supply the average load demand for longer time.

A combination of ultracapacitor and battery can take advantage of each kind of energy storage devices to yield a power source having high power density and high energy density. This project proposes a new configuration of UPQC that consists of the DC/DC converters and the battery supercapacitor hybrid for compensating the voltage interruption. The DC/DC converter is used to actively control the power flow between battery, ultracapacitor and the UPQC DC link, thereby enhancing the power capability of the system.

## 1.4 Objectives and Scope

The project involves the design of UPQC with battery ultracapacitor hybrid, modelling of controllers associated with different components and control strategy to share power between two energy storage devices and UPQC. Thus compensating grid voltage interruptions along with reduced battery stress and extended energy storage devices life are the major considerations. The objectives of this project are listed below.

• To control the charging and discharging of battery and ultracapacitor during normal voltage (0.9 pu to 1.1 pu), voltage sag and voltage swell conditions.

- To study the operation of UPQC with unbalanced non linear load and battery ultracapacitor hybrid during normal voltage, voltage sag and swell.

- To control Battery ultracapacitor hybrid energy storage system during grid voltage interruption and to relieve stress on the battery during load fluctuations for improving battery life.

## 1.5 Organisation of Thesis

**Chapter 2** presents the literature review. Various power quality problems, UPQC topologies and control strategies, battery ultracapacitor hybrid and advantages of using DC/DC converter for battery ultracapacitor hybrid are discussed in detail.

**Chapter 3** describes design, modelling and control of UPQC. The series APF and shunt APF are controlled in voltage control and current control mode respectively.

In **Chapter 4**, the design and modelling of battery and ultracapacitor are explained in detail. The Matlab/Simulink library model of battery and ultracapacitor are used for the simulation study. This chapter discussed the various parameters considered for modelling of battery and ultracapacitor.

**Chapter 5** proposes a UPQC configuration with battery ultracapacitor hybrid energy storage system. The control of UPQC, battery and ultracapacitor during different voltage disturbances are explained. The operation of UPQC in grid connected mode and voltage interruption condition are explained in detail.

**Chapter 6** discusses simulation results. The performance of UPQC and battery ultracapacitor hybrid energy storage system are verified with the help of simulation results. **Chapter 7** discusses the conclusions and future scope of work.

## **CHAPTER 2**

## LITERATURE REVIEW

Power quality (PQ) has significant influence on high technology equipments related to automation, communication, precise manufacturing technique, online services and advanced control. Majority of the distributed generations (DG) from renewable energy sources are connected to the grid through power electronic devices, which introduce additional harmonics especially switching harmonics in the distribution systems. Research is being carried out to integrate active filtering devices especially the combination of shunt and series devices to mitigate a variety of PQ problems by using a single device.

For a generalized solution, UPQC could be the most effective PQ protecting device for sensitive non linear loads, which draws harmonic current and require quality input supply. Also, harmonics in the load current should be isolated to ensure the quality of the supply current. Battery and ultracapacitor are the two effective energy storage devices that can be used with UPQC, for enabling UPQC to work under voltage interruptions. Ultracapacitor reduces the stress on the battery, thus improving the life of battery. Different power quality terms, UPQC configurations and control methods, the idea of combining two different storage elements, the choice of devices and the previous attempts made towards it are briefly described in this chapter.

## 2.1 Introduction to Power Quality

Most of the power apparatus made over a decade back could operate normally with wide variations of voltage, frequency and current. However, equipment developed in recent years is generally not that tolerant to these variations because of the increased use of power electronic switches and electronic controllers. Hence, power system disturbances, which were tolerated earlier, may now cause disturbances to industrial power system with a huge loss of production and this could be substantial with greater stress

on quality and productivity of products. In a developing country like India, PQ is of prime importance considering the need for energy conservation.

## 2.1.1 Power Quality Problems

The power quality problems can be put under the following main categories.

- Voltage dip or sag

- Voltage swell

- Voltage fluctuations and flicker

- Voltage interruptions

- Harmonics

- Unbalances

- Transients

- Commutation notches

- Electric noise

PQ parameter variations fall into three main categories namely transient disturbances, momentary disturbances and steady state disturbances. Transient disturbances include oscillatory transients, localized faults, unipolar transients and other events typically lasting less than 10 ms. Momentary disturbances, on the other hand are voltage swell/sag lasting more than 3 ms but less than 3 sec. Steady state disturbances are deviations lasting more than 3 sec.

## 2.1.2 Power Quality Terminology

More commonly used power quality terms [22] are defined and explained below.

#### 2.1.2.1 Flicker

Flicker can be expressed as the change in voltage over nominal voltage expressed as a percent. Any load that has significant time variations, especially in the reactive power, can cause voltage fluctuations. The term flicker is derived from the impact of the voltage

fluctuation on lighting intensity. Voltage fluctuation is an electromagnetic phenomenon and flicker is an undesirable effect of that phenomenon.

#### 2.1.2.2 Power frequency

Frequency variation is extremely rare in power grids. Frequency variations occur systems with standby diesel generators. Modern SMPS is frequency tolerant, and are generally not affected by small frequency shifts. Frequency variations are very dangerous in systems with motors, because it changes the angular speed of motor and other parameters like torques and power. The magnitude of the frequency shift and its duration mainly depends on the system load characteristics and the response of the power generation system to load changes.

By standard EN 50160, frequency in the systems with synchronous connection to an interconnected system has to be in range as given below.

```

\pm 1\%~(49.5-50.5~{\rm Hz})~{\rm for}~99.5\%~{\rm of}~{\rm a}~{\rm year} -6\%/+4\%~(47-52~{\rm Hz})~{\rm for}~100\%~{\rm of}~{\rm the}~{\rm time}

```

In the systems with no synchronous connection to an interconnected system frequency has to be in range as given below.

```

\pm 2\% (49 - 51 Hz) for 99.5% of a year \pm 15\% (42.5 - 57.5 Hz) for 100% of the time.

```

#### 2.1.2.3 Voltage sag

Sag is a decrease in rms voltage or current at the power frequency for durations from 0.5 cycles to 1 minute [22]. Voltage sags are usually associated with system faults, starting of heavy motors and switching of large loads. Fault on a parallel feeder circuit results in a drop in the bus voltage which affects all the nearby healthy feeders until the fault is cleared. In PQ problems, the term sag is using to describe a short duration voltage decrease. The IEC definition for this phenomenon is dip. Sag duration is subdivided into three categories, namely, instantaneous, temporary and momentary, which coincide with the three categories of swell and interruption.

## 2.1.2.4 Voltage swell

Swell is an increase in rms voltage or current at the power frequency for durations from 0.5 cycles to 1 min [22]. Typical values are 1.1 - 1.8 pu. Voltage swells are associated with system faults but they are much less common than voltage sags. The main causes of voltage swells are a single line to ground fault, a large load switching OFF and a large capacitor bank switching ON.

## 2.1.2.5 *Momentary interruption*

Momentary interruption is the complete loss of voltage (<0.1 pu) on one or more phase conductors for a time period between 0.5 cycles and 3 sec [22]. Momentary interruptions on power utility systems occur due to automatic circuit reclosings which are used to clear temporary faults on the system, mechanical transfer switches, poor intermittent connections used and faults adjacent to the load which dip the voltage to zero volts.

#### 2.1.2.6 Sustained interruption

When decrease in source voltages occur (<0.1 pu) for more than 1 minute, it is considered as a sustained interruption. A sustained interruption is in the category of a long duration voltage disturbances. Sustained interruptions are specific power system phenomena and have no relation to the term outage. Outage does not refer to a specific phenomena, but rather to the state of a component in a system that has failed to function as expected [22]. A loss of service means that no source voltage is present where as interruption implies that a small but inconsequential (< 0.1 pu) of voltage may remain on the incoming transmission lines.

#### 2.1.2.7 Temporary interruption

The complete loss of voltage (<0.1 pu) on one or more phase conductors for a time period between 3 s to 1 minute is considered as a temporary interruption. Fig. 2.1 shows the different voltage variations, distributed based on the duration of voltage variations.

Fig. 2.1 Distribution of voltage problems.

#### 2.1.2.8 Voltage unbalance

Voltage unbalance (or imbalance) is defined as the ratio of the negative or zero sequence component to the positive sequence component [22]. The negative or zero sequence voltages in a power system generally result from unbalanced loads, faults in one or two lines and capacitor bank irregularities.

#### 2.1.2.9 Harmonics

Harmonics are sinusoidal currents or voltages having frequency components that are integer multiples of the frequency at which the system is designed to operate (termed the fundamental component, in India it is 50 Hz). Harmonics combine with the fundamental current or voltage produces waveform distortion. Harmonics exists due to the nonlinear characteristics of devices and loads used in the power system. Voltage distortion results due to nonlinear voltage drops across the feeder impedances by harmonic currents. Harmonic distortion is a growing concern for many customers and utilities due to increasing application of power electronics equipment.

## 2.1.2.10 DC offset

DC offset is the presence of a DC current or voltage in an ac power system. Direct current in alternating current networks affects the system adversely due to an increase in transformer saturation and additional stress on insulation.

#### 2.1.2.11 Interharmonics

Interharmonics are currents or voltages having frequency components that are not integer multiples of fundamental frequency. The main sources of interharmonic distortion are cyclo-converters, static frequency converters, arcing devices and induction motors. The IEC places background noise phenomenon in the interharmonic category.

#### 2.1.2.12 Transient

Transient is designating a quantity or a phenomenon which varies rapidly between two consecutive steady states for short time interval. A transient can be a unidirectional impulse of either polarity or a damped oscillatory wave with the first peak occurring in either polarity. Transients can be classified into two main categories, impulsive and oscillatory. An impulsive transient is a sudden non power frequency change in the steady state condition of current, voltage or both, that is unidirectional in polarity. The most common cause of impulsive transients is lightning. An oscillatory transient is similar to impulsive transient except that the former has both positive and negative polarities.

#### **2.1.2.13** *Notching*

Notch is mainly a switching disturbance of the normal power system voltage waveform lasting less than 0.5 cycles which is initially of opposite polarity than the waveform and is thus subtracted from the normal waveform in terms of the peak value of the disturbance voltage [22]. Notching can occur due to current commutation from one phase to another, three phase converters that produce continuous DC currents may cause voltage notching. Voltage notching represents a special case that falls between transients and harmonic distortion.

#### 2.1.2.14 *Noise*

Noise is defined as an unwanted electrical signals with broadband spectral content lower than 200 kHz superimposed upon the power system current or voltage in phase conductors, or found on neutral conductors or signal lines. Arcing equipment, power electronic devices, control circuits and switching power supplies can cause noise in the power system. Noise consists of any unwanted distortion of voltage or current that cannot be classified as harmonic distortion or transients.

## 2.2 Unified Power Quality Conditioner (UPQC)

PQ issues are becoming more and more significant in these days because of the large number of power electronic devices and switches that behave as nonlinear loads. Many solutions to PQ problems are available for both the operator and the end user. The shunt APF is usually connected across the loads to compensate for all current related problems such as the reactive power compensation, power factor correction, load unbalance compensation and current harmonic compensation. The series APF is connected in series with the line through series injection transformer. It acts as controlled source of voltage and can compensate all voltage related problems such as voltage sag, voltage harmonics, flicker and voltage swell. UPQC is a custom power device that consists of both series APF and shunt APF. UPQC system can be divided into two sections, namely the control unit and the power circuit. Control unit includes voltage and current disturbance detection, reference signal generation, gate pulse generation and voltage/current measurements. Power circuit consists of two VSI, standby and system protection systems, injection transformers and harmonic filters.

The findings of the comprehensive literature survey summarize the available studies related to power circuit and control unit of UPQC.

## 2.2.1 Power Circuit Topologies of UPQC

UPQC is relatively a new member of the custom power devices family. It is a combination of series and shunt compensator. UPQC can be used for compensating supply

voltage flicker, voltage sag, swell, load reactive power, voltage and current unbalance and harmonics in voltage and current. In other words, UPQC has the capability of correcting the current and voltage related problems at the point of installation on power systems . The UPQC therefore is expected to be one of the most powerful equipment to mitigate all the power quality issues.

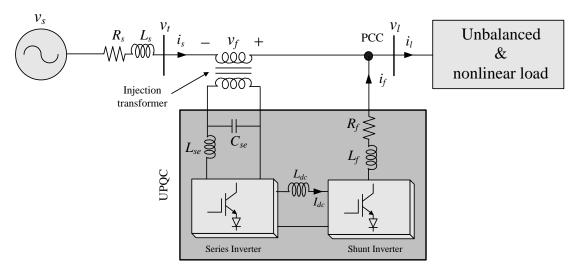

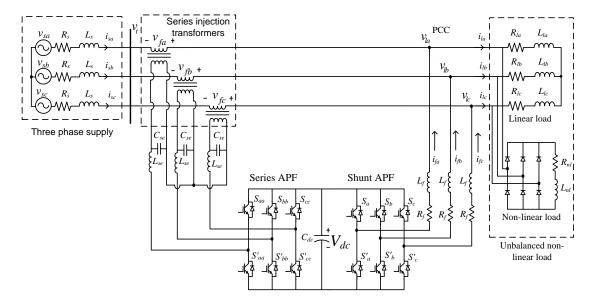

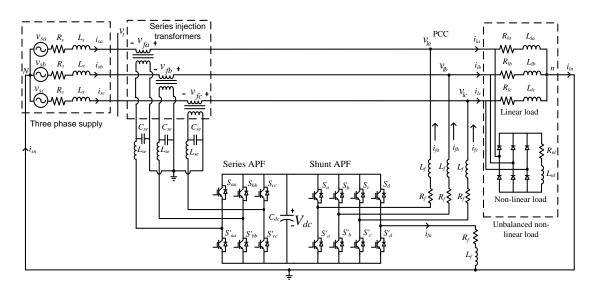

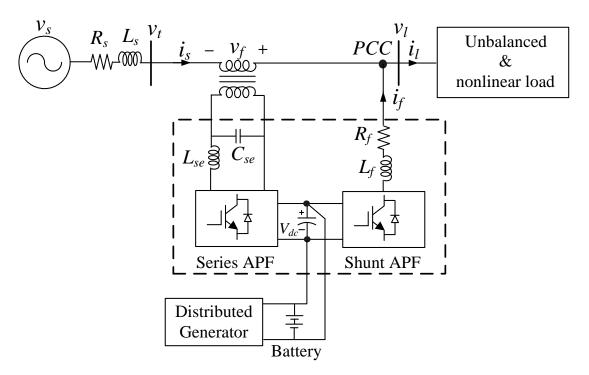

Fig. 2.2 shows the power circuit of the neutral clamped VSI topology based UPQC which uses split capacitor as DC link. In this figure,  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  are the source voltage of phase a, b and c respectively. Similarly,  $v_{ta}$ ,  $v_{tb}$  and  $v_{tc}$  are the terminal voltages (supply voltage after voltage drop in the feeder impedance),  $v_{fa}$ ,  $v_{fb}$  and  $v_{fc}$  are the voltage injected by the series APF.  $v_{la}$ ,  $v_{lb}$  and  $v_{lc}$  are the three phase load voltages. The three phase source currents are represented by  $i_{sa}$ ,  $i_{sb}$  and  $i_{sc}$ , load currents are  $i_{la}$ ,  $i_{lb}$  and  $i_{lc}$ . The shunt APF currents are denoted by  $i_{fa}$ ,  $i_{fb}$  and  $i_{fc}$  and  $i_{ln}$  is the current in the load neutral wire.  $L_s$  and  $R_s$  represent the feeder inductance and resistance respectively.  $C_{sh}$  is the shunt filter capacitor,  $L_f$  and  $R_f$  are shunt APF filter inductance and resistance respectively. The filter inductance and capacitance of the series APF are represented by  $L_{se}$  and  $C_{se}$  respectively. The load includes both linear and nonlinear loads. The DC link capacitance and voltages across them are represented by  $C_{dc1} = C_{dc2} = C_{dc}$  and  $V_{dc1} = V_{dc2} = V_{dc}$  respectively.

Fig. 2.2 Power circuit of three phase UPQC.

The UPQC consists of two voltage source inverters, which are connected back to back with a common DC energy storage capacitor. One of these two VSIs is con-

nected in series with the feeder called series APF and the other is connected in parallel (shunt APF) to the same feeder. The shunt APF tackles the current related problems, whereas, the series APF is the most suitable to mitigate the voltage related problems. Since the modern distribution system demands a better power quality, installation of these APFs has greater scope in distribution systems. However, installing two separate APFs to compensate current and voltage related PQ problems independently may not be a cost effective solution. The back to back inverter system configuration came into attention when Fujita and Akagi [23] proved the practical application of UPQC topology with experimental results. They named this device as unified power quality conditioner (UPQC) and since then the name UPQC has been popularly used by majority of the researchers. The back to back converter topology has been also addressed as series-parallel converter [24], unified active power filter (UAPF) [25], universal active power line conditioner [26], universal power quality conditioning system (UPQS) [27], universal active filter [28], and so forth.

UPQC is similar to a unified power flow controller (UPFC) [29] in construction. A UPFC is employed in power transmission system whereas UPQC is employed in a power distribution system and it perform shunt and series compensation simultaneously. However, a UPFC only needs to provide balance series and/or shunt compensation. Since the transmission network generally operates under a balanced and distortion free environment. On the other hand, a power system distribution network may contain distortion, DC components, and unbalance both in voltages and currents. Therefore, a UPQC should operate under this environment while performing series and/or shunt compensation. The main components of UPQC are as follows.

- A VSI which is connected across the load (at the PCC) and acts as a shunt APF and another VSI in series with the line (through an injection transformer) which acts as a series APF.

- Shunt coupling inductor  $L_f$  is used to interface the shunt inverter to the network. It also helps in smoothing the inverter current. Some configurations uses an isolation transformer to electrically isolate the shunt inverter from the network.

- A common DC link ( $L_{dc}$  or  $C_{dc}$ ) that is formed by using an inductor or a capacitor (usually capacitor is used). In Fig. 2.2, the DC link is realized using a capacitor which interconnects the two inverters and also maintains a constant DC bus voltage across it.

- A LC low pass filter (LPF) is connected to the output of series APF to eliminate switching harmonics from the inverter output voltage. A small resistor can be used in series with inductor to provide sufficient damping to voltage oscillations.

• A Series injection transformer with suitable turns ratio is used to connect the series APF in the network.

In principle UPQC is an integration of series and shunt APF with a common DC bus. The shunt APF of UPQC is controlled in current control mode such that it delivers a current ( $I_f$ ) which follows the current reference given by the UPQC control algorithm. Usually the shunt inverter is used to maintain DC link voltage at the reference value. In order to cancel out the harmonics generated by nonlinear load, the shunt APF reference current can be calculated as,

$$i_f^* = i_l - i_s^*$$

where  $i_f^*$ ,  $i_s^*$  and  $i_l$  represent the shunt inverter reference current, reference source current and load current respectively.

Similarly, the series inverter of UPQC is controlled in voltage control mode such that it injects a voltage in series with the terminal voltage to achieve a sinusoidal, distortion free voltage with desired magnitude (rms) at the load terminal. The operation of series APF can be represented by the following equation.

$$v_f^* = v_l^* - v_t$$

where  $v_f^*$ ,  $v_l^*$  and  $v_t$  represent the series inverter reference voltage, reference load voltage, and actual source terminal voltage respectively.

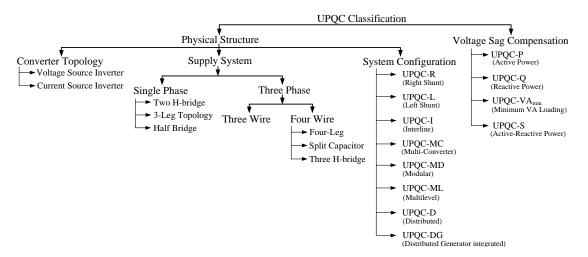

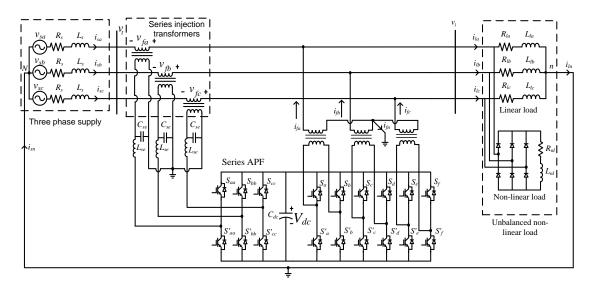

Fig. 2.3 shows a pictorial view for the classification of UPQC [30]. The UPQC classification can be based on the physical structure and voltage sag compensation approach used.

#### 2.2.1.1 Classification based on the converter topology

Generally the shunt inverter is responsible to regulate the DC link at reference value. The UPQC can be developed using a current source inverter (CSI) [31] that shares a common energy storage inductor  $L_{dc}$  to form the DC link. Fig. 2.4 shows single line representation of a CSI based UPQC system configuration.

VSI based configuration is the most common and popular converter topology for

Fig. 2.3 Classification of UPQC.

Fig. 2.4 CSI based UPQC system configuration.

UPQC that shares a common energy storage capacitor  $C_{dc}$ . Single line representation of a VSI based UPQC system configuration is shown in Fig. 2.5. The VSI based topology is dominantly used in almost all the reported work on the UPQC. Some of the advantages offered by voltage source inverter topology over current source inverter includes cheaper, lighter in weight, no need of blocking diodes, flexible overall control and capability of multilevel operation.

## 2.2.1.2 Classification based on the supply system

Both 1- $\phi$  and 3- $\phi$  systems has similar kind of voltage related PQ problems except an additional voltage unbalance compensation needed in the case of a 3- $\phi$  system. The current harmonics and the load reactive current are the major issues in 1- $\phi$  system. In the case of 3- $\phi$  three wire (3 $\phi$ 3W) system, current unbalance are also comes into picture.

Fig. 2.5 VSI based UPQC system configuration.

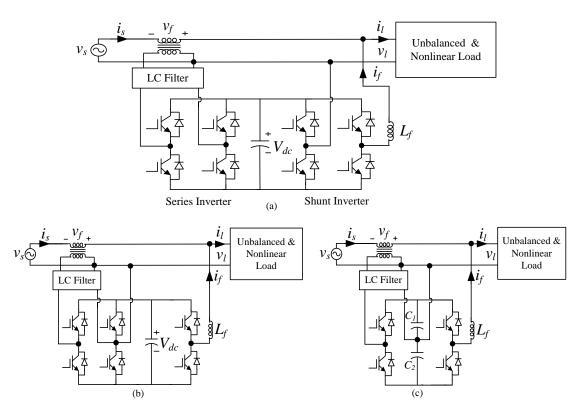

The 3- $\phi$  four wire (3 $\phi$ 4W) system requires an additional neutral current compensation control. Fig.2.6(a) shows the most popular UPQC system configuration to compensate the PQ problems in 1- $\phi$  two wire (1 $\phi$ 2W) supply system consisting of two H-bridge inverters [32]. Nasiri and Emadi introduced two configurations for 1- $\phi$  UPQC [33],

Fig. 2.6  $1\phi$ 2W UPQC: (a) Two H-bridge configuration (b) Three leg configuration (c) Half bridge configuration.

namely, three leg 1- $\phi$  UPQC shown in Fig. 2.6(b) and half bridge 1- $\phi$  UPQC shown in Fig. 2.6(c). These topologies are useful for low cost low power applications.

Several nonlinear loads such as, current regulator, adjustable speed drives fed from  $3\phi 3W$ , arc welding machines, frequency converters, and arc furnaces impose combinations of PQ problems. A  $3\phi 3W$  VSI based UPQC is shown in Fig. 2.7. Apart from the 3- $\phi$  loads many industrial plants often consist of combined loads such as, 1- $\phi$  loads and a variety of 1- $\phi$  loads supplied by  $3\phi 4W$  sources. The neutral conductor demands an additional compensation requirement under unbalanced currents. To mitigate the neutral current problems in  $3\phi 4W$  system, various shunt inverter configurations have been proposed by researchers such as, four leg, two split capacitor and three H-bridge topologies. Fig. 2.2 shows the  $3\phi 4W$  UPQC based on split capacitor topology. Fig. 2.8

Fig. 2.7 Power circuit of  $3\phi 3W$  UPQC.

shows the  $3\phi4W$  UPQC based on four leg shunt inverter and Fig. 2.9 shows H-bridge based  $3\phi4W$  UPQC.

In split capacitor topology, the voltages across both the capacitor should be equal to avoid the flow of circulating current. This requires an additional control algorithm for DC link capacitor voltage regulation. In four leg topology, the load neutral current is compensated by using an additional leg (two semiconductor switches). The four leg topology may offer better control over neutral current compared to other topologies due to the dedicated fourth leg. The three H-bridge topology consists of three units of  $1-\phi$  H-bridge inverters connected to the same DC link of the UPQC. These three H-bridges can use for shunt inverter or series inverter.

Fig. 2.8  $3\phi$ 4W UPQC based on four leg shunt inverter topology.

Fig. 2.9  $3\phi$ 4W UPQC based on H-bridge shunt inverter topology.

## 2.2.1.3 Classification based on the UPQC configuration

Based on the shunt inverter location (right or left) with respect to series inverter, UPQC can be classified as UPQC-R and UPQC-L [34]. Figs. 2.5 shows UPQC-R system configuration, while Fig. 2.10 shows UPQC-L configuration. Among two configurations, the UPQC-R is most commonly used by the researchers.

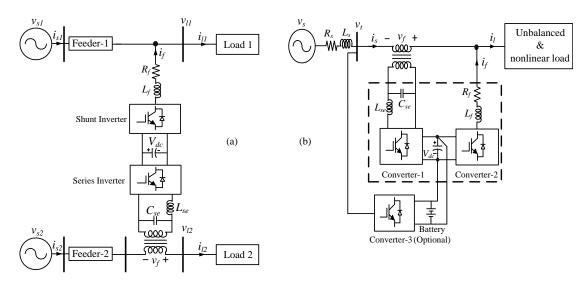

In Interline UPQC (UPQC-I) [35], two converters of the UPQC are connected between two distribution feeders. One of the converter is connected in series with one of the feeders while the other converter in shunt with second feeder as shown in Fig. 2.11(a). With such a configuration, both the feeder voltages can be simultaneously regulated. Furthermore, the UPQC-I can manage and control the flow of real power between

Fig. 2.10 Schematic diagram of left shunt UPQC.

the two feeders. The current related problems (such as unbalance and harmonics) could be effectively compensated only on the shunt inverter connected feeder. Alternatively, the harmonics in the voltages can only be mitigated in the feeder in which the series inverter is connected. Researchers have explored the possibilities for improving the

Fig. 2.11 UPQC configurations: (a) Interline UPQC (b) Multi-converter UPQC.

power system performance by considering a third inverter unit to support the DC link. To further enhance the system performance, the use of an ultracapacitor or storage battery can be used. The third converter can be connected in many ways, for example, in parallel with the same feeder [36] or in series/parallel with the adjacent feeder [37] and is named as multi-converter UPQC (UPQC-MC). In MC-UPQC, the third converter is connected in series with the adjacent feeder. Similar to UPQC-I, the UPQC-MC can be connected between two different feeders. Fig. 2.11(b) shows a multi converter UPQC

configuration in which three inverters are utilized to realize the UPQC system.

In [38] a modular UPQC (UPQC-MD) configuration is realized by using several Hbridge modules similar as connecting several 1- $\phi$  UPQCs in cascade in each phase. As the number of modules increase, the voltage across each module decreases, thus it can be useful in the medium voltage application to achieve higher power levels. A multilevel UPQC (UPQC-ML) [39] uses multilevel converters, a three level topology requires double semiconductor devices as that of a two level UPQC system. A  $3\phi4W$  distribution system is generally realized by utilizing a  $\Delta - Y$  transformer at the distribution level or by providing a neutral conductor along with the three power lines from substation. A new topology for 3P4W UPQC based distribution system is proposed in [40], in that it is possible to extend the UPQC based 3P3W system to a 3P4W system referred as 3P3W to 3P4W distribution UPQC (UPQC-D). The neutral of injection transformer, used in the series APF part of UPQC is considered as a neutral for 3P4W system. Thus, even if the power supplied by the grid is 3P3W, an easy expansion to 3P4W system can be achieved with this configuration. A fourth leg is added to the shunt APF of 3P3W UPQC to compensate the transformer neutral current and it can ensure zero current flow toward the neutral point. Thus, it is possible to maintain transformer neutral point at virtual zero potential.

Wind and solar energies are emerging as alternate sources of electricity. The UPQC can be integrated with one or many distributed generation (DG) systems. The system configurations thus, achieved is referred as UPQC-DG and is shown in Fig. 2.12. The DG power can be regulated and managed through UPQC to supply to the electrical loads connected to the PCC in addition to the current and voltage PQ problem compensation. Additionally, a battery can be connected to the DC link for energy storage, such that the excess DG generated power can be stored and used as backup. In the event of voltage interruption, the UPQC-DG system can act as a backup power source.

### 2.2.1.4 Classification based on the voltage sag compensation approach

The voltage sag on power system is considered as one of the most important and frequent PQ problem. The existing literature suggests four important methods to compensate the voltage sag in UPQC applications.

Fig. 2.12 UPQC-DG system configuration.

UPQCs mitigating voltage sag using active power are called UPQC-P. In principle to compensate the voltage sag, an in phase voltage component is injected in the series with grid voltage by series APF through an injection transformer [41]. The voltage sag can also be mitigated by reactive power injection through series APF of UPQC [42]. In that case, it is called as UPQC-Q (Q stands for reactive power). The concept is to inject a quadrature voltage by the series APF such that the vector sum of terminal voltage and the injected filter voltage equals the required rated load voltage. The shunt inverter of UPQC maintains a upf operation at the PCC. Therefore, by injecting a voltage in quadrature with the terminal voltage, the need of active power to mitigate voltage sag is eliminated. However, the load voltage achieved has phase shift with respect to the source terminal voltage. To compensate an equal percentage of voltage sag, the UPQC-Q requires larger magnitude of injection voltage compared to UPQC-P. In [43] a UPQC control is used to minimize the UPQC volt-ampere (VI) rating during voltage sag compensation. In this method, the voltage is injected to the line at certain optimal angle with respect to the source current. This method of compensating voltage sag using UPQC is abbreviated as UPQC-VA<sub>min</sub>. In UPQC-S [44] (S stands for apparent power), series APF delivers both reactive and active power during voltage sag.

In general, the UPQC-MC, UPQC-I, UPQC-ML, UPQC-MD, UPQC-DG and UPQC-D can be based on CSI or VSI converter topology. Moreover, these topologies can be

configured as UPQC-L or UPQC-R. Expect UPQC-D all other configuration can be realized for  $3\phi3W$ ,  $3\phi4W$  and  $1\phi2W$  systems. Additionally, the UPQC sag/swell compensation controllers can be based on UPQC-Q, UPQC-P, UPQC-VA<sub>min</sub> and UPQC-S approaches.

## 2.2.2 Control Techniques For UPQC

Control strategy decides the desired operation and behavior of UPQC. The UPQC control strategy determines the reference signals (current for shunt and voltage for series APF) and decides the switching methods for inverter switches, such that the desired performance can be achieved. There are several control techniques available in the existing literature, those have successfully applied to UPQC systems. Frequency domain methods such as, based on the fast Fourier transform (FFT) method, are not much popular due to its delay in calculating the FFT and large computation time. UPQC control methods in the time domain are based on instantaneous derivation of compensating references in the form of current or voltage signals. There are many control methods in the time domain, few are briefly discussed here. Three most widely used time domain control techniques for UPQC are the instantaneous active and reactive power theory or  $3-\phi$  pq theory [45], synchronous reference frame method or  $3-\phi$  dq theory [46] and instantaneous symmetrical components theory [47].

#### 2.2.2.1 Instantaneous reactive power theory

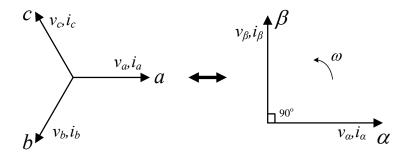

The main aim of instantaneous reactive power theory is to develop a mathematical formulation for the instantaneous reactive power so that the reactive power can be easily calculated and compensated. Shunt APF needs to compensate for load reactive power and load current harmonics. Hence this theory is mostly applied to calculate the reference current of the shunt active filter. It uses the instantaneous values of currents and voltages to formulate the compensating quantities. The abc phase voltages and currents are transformed to the stationary  $\alpha$ - $\beta$  axes using the Clarke transformation as given below and are illustrated in Fig. 2.13. For a balanced source voltage the  $v_0$  component

will be zero.

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix}$$

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix}$$

$$(2.1)$$

The instantaneous power on both reference frames are equal. For a balanced  $3-\phi$  system,

$$v_a i_a + v_b i_a + v_c i_c = v_\alpha i_\alpha + v_\beta i_\beta$$

$$p = v_\alpha i_\alpha + v_\beta i_\beta$$

(2.2)

(where v and i are voltage and current respectively)

Fig. 2.13 *abc* to  $\alpha\beta$  reference frame

The instantaneous reactive power is defined by using cross product of the instantaneous voltage in one axis and the instantaneous current in the other axis.

$$q = \overrightarrow{v_{\alpha}} \times \overrightarrow{i_{\beta}} + \overrightarrow{v_{\beta}} \times \overrightarrow{i_{\alpha}}$$

(2.3)

$$q = v_{\alpha}i_{\beta} + v_{\beta}i_{\alpha} \tag{2.4}$$

Using (2.1) and (2.3), the reactive can be expressed in *abc* coordinates as given below.