# Design Of A 5-Stage Dual Issue Processor

A Project Report

submitted by

## **MANISH KUMAR MAURYA**

in partial fulfilment of the requirements

for the award of the degree of

# BACHELOR OF TECHNOLOGY AND MASTER OF TECHNOLOGY

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS.

MAY 2017

THESIS CERTIFICATE

This is to certify that the thesis titled Design Of A 5-Stage Dual Issue Processor,

submitted by Manish Kumar Maurya, to the Indian Institute of Technology, Madras,

for the award of the degree of Bachelor Of Technology and Master Of Technology,

is a bonafide record of the research work done by him under our supervision. The

contents of this thesis, in full or in parts, have not been submitted to any other Institute

or University for the award of any degree or diploma.

Dr. V. Kamakoti

Research Guide Professor

Dept. of Computer Science and Engineering

IIT-Madras, 600 036

Place: Chennai

Date: May 2017

## **ACKNOWLEDGEMENTS**

Successful completion of this project work would not have been possible without the guidance, support and encouragement of many people. I take this opportunity to express my sincere gratitude and appreciation to them.

First and foremost I offer my earnest gratitude to my guide, **Dr. V. Kamakoti** who has supported me throughout my project work with his patience and knowledge while allowing me freedom and flexibility to follow my own thought process.

My special thanks and deepest gratitude to **Neel Gala** and **Rahul Bodduna** who have been very supportive. They have enriched the project experience with their knowledge of the subject matter, active participation, deep understanding and invaluable suggestions.

## **ABSTRACT**

KEYWORDS: Superscalar; Dual-issue; 5-stage pipeline; Data Dependencies

The number of transistors on a chip is increasing every year (according to Moore's law it doubles in every 2 years) and designers are developing different techniques and architectures to utilize all this hardware to increase the throughput of a processor. This project aims to design a superscalar processor which in simple terms is like replicating the hardware units of a processor to execute more than one instruction in the same time unit which means increasing the throughput. The processor designed in this project is a dual issue and has 5-stages that are Fetch, Decode, Execute, Memory and Writeback. Ideally a superscalar processor should give the improvement in multiples of the units replicated, like a dual issue processor should double the throughput but as this project will show in real scenario this is not possible due to data dependencies between the instructions and many multiple cycle operations which stalls the pipeline, a superscalar processor exploits the Instruction Level Parallelism of the program so it depends on the program how many of its instructions can be executed in parallel. We will see different results for different test cases executed on this processor.

# TABLE OF CONTENTS

| A( | 1.1 Overview of current processor  1.2 Changes in the current processor  1.3 Organization of the thesis  BACKGROUND  2.1 Micro-architecture Basics  2.1.1 How Does a Machine Process Instructions  2.1.2 What is ISA  2.1.3 Single-cycle and Multi-cycle Machines  2.1.4 Pipeline in detail  2.1.5 Pipeline hazards  2.1.6 From scalar to superscalar  2.1.7 Superscalar processor design | i       |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al | BSTR                                                                                                                                                                                                                                                                                                                                                                                      | ACT     |                                         | ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LI | ST O                                                                                                                                                                                                                                                                                                                                                                                      | F FIGU  | URES                                    | vi         vi         and the process Instructions is a process Instructions is a process Instruction is a proces |

| Al | BBRE                                                                                                                                                                                                                                                                                                                                                                                      | EVIATI( | ONS                                     | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1  | INT                                                                                                                                                                                                                                                                                                                                                                                       | RODU(   | CTION                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 1.1                                                                                                                                                                                                                                                                                                                                                                                       | Overv   | iew of current processor                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 1.2                                                                                                                                                                                                                                                                                                                                                                                       | Chang   | ges in the current processor            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 1.3                                                                                                                                                                                                                                                                                                                                                                                       | Organ   | ization of the thesis                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2  | BAC                                                                                                                                                                                                                                                                                                                                                                                       | CKGRO   | DUND                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 2.1                                                                                                                                                                                                                                                                                                                                                                                       | Micro   | -architecture Basics                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.1   | How Does a Machine Process Instructions | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.2   | What is ISA                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.3   | Single-cycle and Multi-cycle Machines   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.4   | Pipeline in detail                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.5   | Pipeline hazards                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.6   | From scalar to superscalar              | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.1.7   | Superscalar processor design            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 2.2                                                                                                                                                                                                                                                                                                                                                                                       | Bluesp  | pec System Verilog                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.2.1   | Building a design in BSV                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.2.2   | Rules                                   | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 2.2.3   | Module hierarchy and Interfaces         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3  | IMI                                                                                                                                                                                                                                                                                                                                                                                       | PLEME   | ENTATION                                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 3.1                                                                                                                                                                                                                                                                                                                                                                                       | Fetch   | Unit Design                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                                                                                                                                                                                                                                                                                                                                                                                           | 3.1.1   | Cache Design for Dual issue             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |     | 3.1.2 Fetch Unit changes       | 21 |

|---|-----|--------------------------------|----|

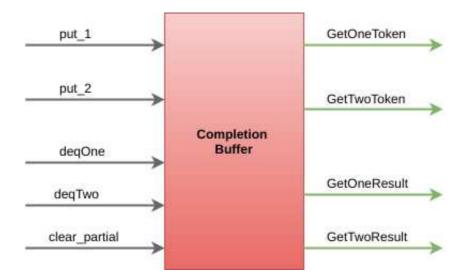

|   | 3.2 | Completion Buffer Design       | 22 |

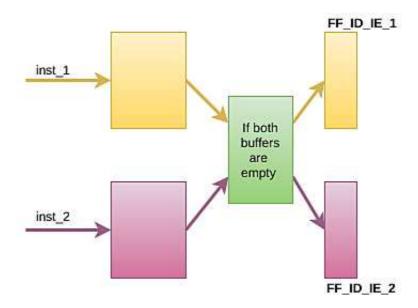

|   | 3.3 | Decode Stage Changes           | 25 |

|   | 3.4 | Register File changes          | 25 |

|   |     | 3.4.1 Working of register file | 27 |

|   | 3.5 | Execution Stage Changes        | 28 |

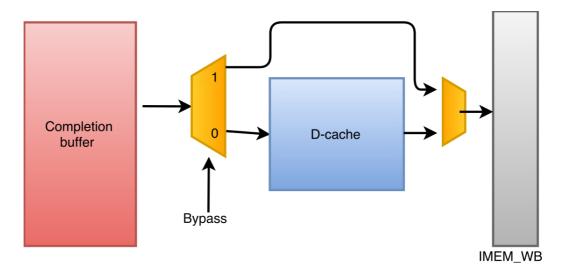

|   | 3.6 | Memory Stage Changes           | 28 |

|   | 3.7 | Write Back Stage               | 29 |

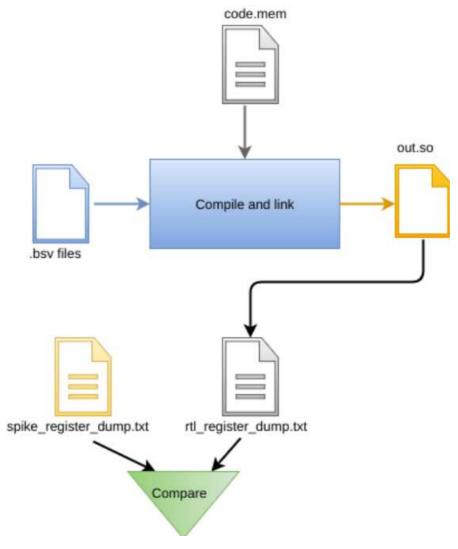

| 4 | VEF | RIFICATION AND RESULTS         | 30 |

|   | 4.1 | Verification Flow              | 30 |

|   | 4.2 | Debugging the code             | 31 |

|   | 4.3 | Results                        | 31 |

| 5 | CO  | NCLUSION AND FUTURE WORK       | 33 |

|   | 5.1 | Conclusion                     | 33 |

|   | 5.2 | Future Work:                   | 33 |

# LIST OF FIGURES

| 2.1  | Single cycle processor datapatii                            | J  |

|------|-------------------------------------------------------------|----|

| 2.2  | Instruction processing in single cycle machine              | 6  |

| 2.3  | Instruction processing in multi cycle machine               | 6  |

| 2.4  | 5-stage pipelined processor                                 | 8  |

| 2.5  | Instruction processing in a pipelined superscalar processor | 11 |

| 2.6  | A dual issue pipelined processor                            | 12 |

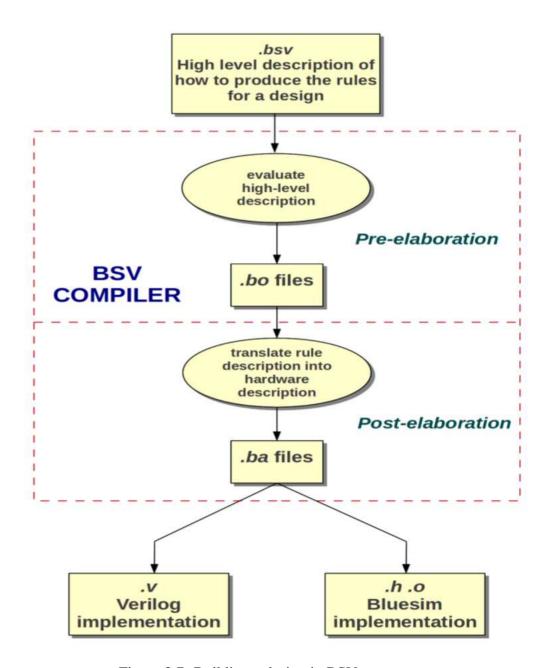

| 2.7  | Building a design in BSV                                    | 15 |

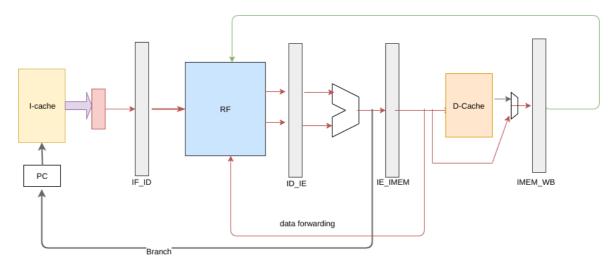

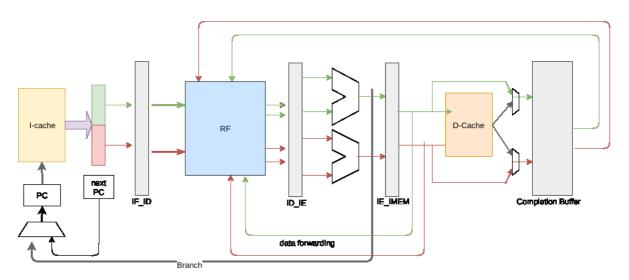

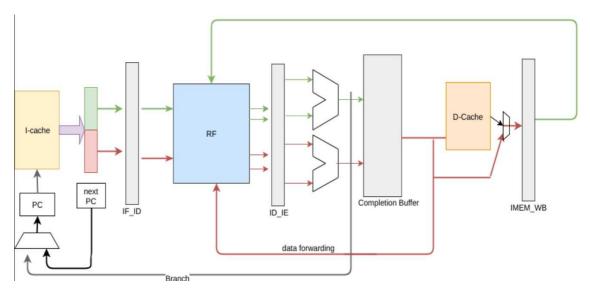

| 3.1  | Designed dual issue processor pipeline                      | 18 |

| 3.2  | Cache interface                                             | 19 |

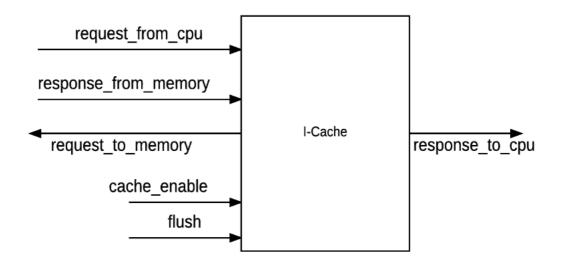

| 3.3  | Single cache line and blocks                                | 20 |

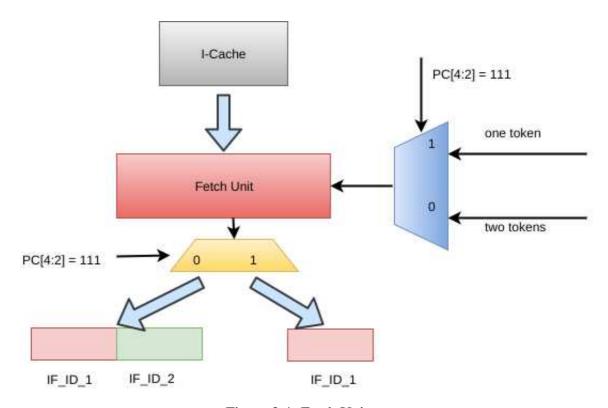

| 3.4  | Fetch Unit                                                  | 21 |

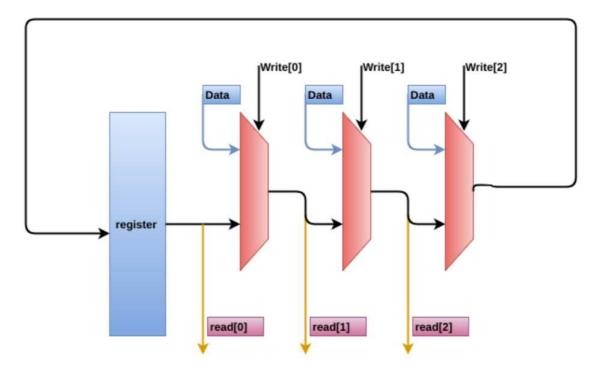

| 3.5  | Circuit implementation of CReg                              | 22 |

| 3.6  | Interface of CompletionBuffer                               | 23 |

| 3.7  | Decode stage design                                         | 25 |

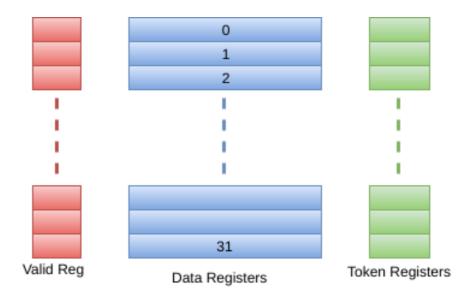

| 3.8  | New register file design                                    | 26 |

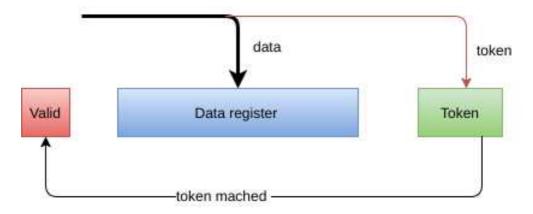

| 3.9  | Data write back in register file                            | 27 |

| 3.10 | Memory stage                                                | 29 |

| 4.1  | Verification flow                                           | 30 |

| 4.2  | Device Utilization                                          | 32 |

| 4.3  | Device Utilization                                          | 32 |

## **ABBREVIATIONS**

**BSV** Bluespec System Verilog

**ISA** Instruction Set Architecture

RISC Reduced Instruction Set Computing

CISC Complex Instruction Set Computing

**HDL** Hardware Description Language

**IPC** Instructions Per Cycle

PC Program Counter

**IF** Instruction Fetch

**ID** Instruction Decode

WB Write Back

WAR Write After Read

**RAW** Read After Write

**WAW** Write After Write

## **CHAPTER 1**

#### INTRODUCTION

Computer has become a essential part of human lives these days. Microprocessor is the central component of any computer. Since its advent, microprocessor throughput has been increasing continuously. It's either because of technology scaling or the advancement of architectural techniques which exploit the workload structure. Transistor density on a chip is approximately doubled every two years due to technology scaling, this is often referred to as Moore's law. With every new generation process node, the transistors get smaller, faster and more power efficient. This results in increase of processor clock speed without increasing power or area, and in the same area now we can pack more transistors that means more hardware which enables more throughput.

# 1.1 Overview of current processor

The Processor design team of Reconfigurable and Intelligent Systems Engineering (RISE) Lab in the Computer Science Department of IIT Madras has been actively involved in building different variants of processors based on RISC-V Instruction Set Architecture(ISA). One of these processors is a 5-stage In-order scalar processor named "C-Class processor". But being a scalar processor the maximum instructions it can execute in a single cycle is 1. This project describes the micro-architecture of a 5-stage in-order dual issue superscalar processor which is designed using C-Class processor as base. A superscalar processor will have higher throughput than a scalar processor but on the cost of more hardware. The entire design of the processor is done using a Hardware Description Language (HDL) called Bluespec SystemVerilog (BSV).

# 1.2 Changes in the current processor

Here are the main changes which I implemented in the current processor these will be explained in detail in coming chapters.

• I-Cache changed to supply two instructions.

• Fetch unit changed to receive two instructions attach token to them and then enqueue

in decode buffers.

• A Completion buffer design and implementation.

• Register file changes to handle inter-dependencies between instructions and to handle

other hazards.

1.3 Organization of the thesis

Chapter 2 contains the theory needed for this project. It starts with the single cy-

cle processor design then deals with Pipelining and how it improves the the processor

throughput with little hardware cost then we go to a supescalar design to further im-

prove the throughput. It also briefly discuss about the ISA, mainly about RISC-V ISA

which is used in this processor. Finally it describes about the HDL called Bluespec Sys-

tem Verilog, its key features.

**Chapter 3** describes the changes implemented in the current processor using Bluespec

System Verilog and also different problems and errors faced during implementation.

**Chapter 4** describes the verification process and results.

**Chapter 5** contains a conclusion and description on the future work.

2

## **CHAPTER 2**

## **BACKGROUND**

## 2.1 Micro-architecture Basics

#### 2.1.1 How Does a Machine Process Instructions

What does processing an instruction means? Processing an instruction means transforming present Architectural State to next Architectural State according to the ISA specification of the instruction.

AS = Architectural (programmer visible) state before an instruction is processed

$\downarrow \downarrow$

Process instruction

$\downarrow$

AS' = Architectural (programmer visible) state after an instruction is processed

ISA specifies abstractly what AS' should be, given an instruction and AS.

#### 2.1.2 What is ISA

The instruction set, also called instruction set architecture (ISA), is part of a computer that pertains to programming, which is basically machine language. The instruction set provides commands to the processor, to tell it what it needs to do. The instruction set consists of addressing modes, instructions, native data types, registers, memory architecture, interrupt, and exception handling, and external I/O. Most of the processors in the present use either Reduced Instruction Set Computer(RISC) ISA or Complex Instruction Set Computer(CISC) ISA, both of these have their merits and demerits.

#### **2.1.2.1** The RISC

A RISC was realized in the late 1970s by IBM. Researchers discovered that most programs did not take advantage of all the various address modes that could be used with the instructions. By reducing the number of address modes and breaking down multi-cycle instructions into multiple single-cycle instructions several advantages were realized:<sup>[2]</sup>

- compilers were easier to write (easier to optimize)

- performance is increased for programs that did simple operations

#### **Evaluation of RISC**

- Emphasis on software

- Register to register

- "LOAD" and "STORE" are independent instructions

- Low cycles per second, large code sizes

#### **2.1.2.2** The CISC

Complex instruction set computing(CISC) is a processor design, where single instructions can execute several low-level operations (such as a load from memory, an arithmetic operation, and a memory store) or are capable of multi-step operations or addressing modes within single instructions.

#### **Evaluation of CISC**

- Emphasis on hardware

- Memory-to-memory

- "LOAD" and "STORE" incorporated in instructions

- Small code sizes, high cycles per second

#### The Overall RISC Advantage

Today, the Intel x86 is arguable the only chip which retains CISC architecture. This is primarily due to advancements in other areas of computer technology. The price of RAM has decreased dramatically. In 1977, 1MB of DRAM cost about \$5,000. By 1994, the same amount of memory cost only \$6 (when adjusted for inflation). Compiler technology has also become more sophisticated, so that the RISC use of RAM and emphasis on software has become ideal.

Our processor is based on RISC-V ISA which is a new instruction set architecture (ISA) that was originally designed to support computer architecture research and education, it's a completely open ISA that is freely available to academia and industry.

## 2.1.3 Single-cycle and Multi-cycle Machines

This section contains theory on single cycle and multicycle machine and why a multicycle machine is better than single cycle, this multicycle machine is the base for our dual issue supersclar processor.

#### 2.1.3.1 Single-cycle machine

A Single-cycle processor does all the instruction processing for a instruction in single cycle i.e. it fetches instruction from memory, executes, and the results are stored all in a single clock cycle. The benefits of single-cycle processors is that they tend to be the most simple in terms of hardware requirements, and they are easy to design. Unfortunately, they tend to have poor data throughput, and require long clock cycles (slow clock rate) in order to perform all the necessary computations in time.

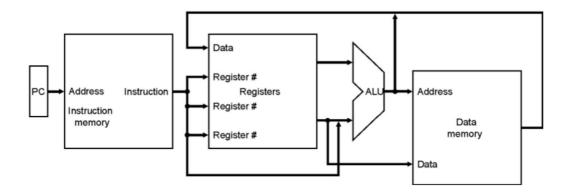

Figure 2.1: Single cycle processor datapath

The length of the cycle must be long enough to accommodate the longest possible propagation delay in the processor. This means that some instructions (typically the arithmetic instructions) will complete quickly, and time will be wasted each cycle. Other

instructions (typically memory read or write instructions) will have a much longer propagation delay.

Figure 2.2: Instruction processing in single cycle machine

## 2.1.3.2 Multi-Cycle pipelined machine

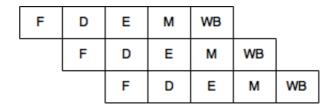

In single cycle machine even when an instruction has completed one stage that stage is still not used till the present instruction completes the processing. In multicycle machine this idle stage can process another instruction so at a time more than one instructions are being processed in the processor but these instructions are in different stages. Here we have 5 stages in our processor these are Fetch(F), Decode(D), Execute(E), Memory operation (M) and Write-back(WB).

Figure 2.3: Instruction processing in multi cycle machine

In figure 2.3 we can see more than one instructions are processing in different stages in a clock cycle.

#### 2.1.3.3 Improvements through pipeling

First we need to understand difference between Latency and Throughput.

**Latency** - After being fetched each instruction takes certain amount of time to complete all the stages and update the register file this is called the latency of that instruction.

**Throughput** - It is the number of instructions executed(completed) per unit of time.

In a pipelined processor the latency to complete an instruction is same or slightly greater than the single cycle machine but the throughput increases because in pipelined processor after 1st instruction we get the output in each cycle.

#### 2.1.3.4 Single cycle vs pipeline example

In an ideal pipeline all the stages take same time to execute and the pipe continues without any interrupts. Making these assumptions here is an example to compare advantage of pipeline over single cycle machine.

A non pipelined machine with 5 stages, each stage takes 50ns to execute, we want to execute 100 instructions.

**Sol.** Instruction latency =  $50 \times 5 = 250 \text{ ns}$

Time to execute 100 instructions = 100 x 250 = 25000 ns

Now lets take a 5 stage pipelined processor with same execution time of each stage and 5ns overhead due to pipeline registers.

**Sol.** Latency = 50x5 + 5 = 255ns

Time to execute 100 instructions = time to execute 1st instruction + 50x rest of the instructions = 255 + 50x99 = 5205ns

Speedup obtained for 100 instructions = 25000/5205 = 4.8

## 2.1.4 Pipeline in detail

In this section I'll explain different stages of pipelined processor and their function.

Figure 2.4: 5-stage pipelined processor

#### **2.1.4.1** Fetch Unit

The instruction fetch unit takes instruction from the I-cache and feeds it into the processor. And it also calculates the next PC.

#### **2.1.4.2 Decode Unit**

The purpose of the instruction decode stage is to understand the semantics of an instruction and this will define how the instruction will be executed by the processor. In this stage processor identifies

- Which registers to read and write

- Type of instruction- ALU, memory, control etc.

#### 2.1.4.3 Execution Unit

In this stage the operands are send to processor's computational unit along with the operation to be performed. In this stage

• arithmetic operations (addition, multiplication, etc.) are performed.

- effective address calculation is done for Load/Store instruction.

- for control-flow instructions change the value of the Program Counter (PC) register.

#### 2.1.4.4 Memory access

In this stage Load and Store operations are performed. Load and store operation are generally multicycle in that case we have to stall the pipe till these operations are completed. If the instruction is not load/store then it will just bypass the memory stage and go to write-back buffer directly.

#### 2.1.4.5 Write-back

This reads the data from imem\_wb buffer and updates the register file. If any instruction is waiting for the updated result of a register then that instruction can only execute when the register is updated from write-back stage.

#### 2.1.5 Pipeline hazards

In the previous section we assumed that our processor is ideal each stage takes equal time and processor never stalled but in reality a processor will have many stalls, a stall is when the processor can not execute the next instruction because of some exceptions or dependence of present instruction on previous instructions.

#### 2.1.5.1 Types of Hazard

- **Data Hazard** Occurs when present instruction depends on the result previous instruction.

- Structural Hazards Occurs when there is resource conflict.

- **Control Hazards** Arises due to branches and other instructions which can change program counter.

We will discuss mainly on the Data Hazards.

#### 2.1.5.2 Data Hazards

These occurs when there are some register dependency between present and past/future instructions. There are three types of data hazard, a hazard can only occur if the register value is being updated and that register is being used by future/past instruction, that's why RAR is not a hazard.

Lets assume two instruction A and B where A should execute before B. Now

• RAW (Read After Write) hazard occurs when B tries to read a register in which A has yet to update the value so B gets the old value which is incorrect so there should be stall till A updates the register.

A: R3 <- R1 op R2

B: R5 <- R3 op R4

• WAR (Write After Read) hazard occurs when B tries to update a register from which A has yet to read. So B should not update the value till A has read the register.

A: R3 < -R1 op R2

B: R1 < -R4 op R5

• WAW (Write After Write) occurs when B updates the same register before A.

A: R3 <- R1 op R2

B: R3 <- R4 op R5

• RAR(Read After Read) is not a hazard and it wont stall the pipe.

RAW is also called True dependency and they are always need to be obeyed.

WAW is called Output dependency and WAR is called Anti dependency, these exits due to limited number of architectural registers. They are dependence on a name, not a value.

#### 2.1.5.3 Dependence handling

Anti and output dependencies are easier to handle: write to the destination in one stage and in program order.

RAW or True dependencies are little difficult, few ways to handle them are:

- Detect and wait until value is available in register file, this will create many bubbles in the pipeline.

- Detect and forward/bypass data to dependent instruction, we forward the data after execution back to the register decode stage and if any other instruction is waiting for the

register value then that instruction can execute now, this way we save bubbles in pipe.

## 2.1.6 From scalar to superscalar

As we know the Moore's law is still being realized by the engineers so the number of transistors in the same are is increasing, that means we have more hardware in the same are area it enables us to design different architectures which will improve the processor throughput. In superscalar pipelined architecture we replicate the hardware of single issue pipeline processor so that we can issue and execute more than one instruction per cycle this increases the throughput and so the performance of processor.

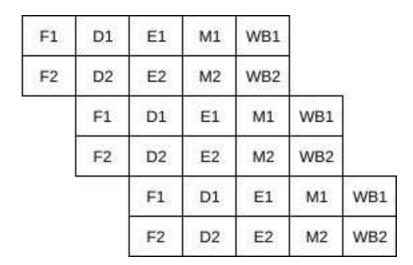

Figure 2.5: Instruction processing in a pipelined superscalar processor

Figure 2.5 shows an ideal superscalar processor in which each stage of the pipeline is duplicated and instruction are independent of each other so pipe is not stalling, but in reality its very hard to replicate all the stages and also there will be many stalls due to the instruction dependencies.

## 2.1.7 Superscalar processor design