# Implementing Cache Coherence through Manager-Client Pairing

A Project Report

submitted by

## **REENA E**

in partial fulfilment of the requirements

for the award of the degree of

#### MASTER OF TECHNOLOGY

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS. June 2016

THESIS CERTIFICATE

This is to certify that the thesis titled Implementing Cache Coherence through Manager-

Client Pairing, submitted by Reena E, to the Indian Institute of Technology, Madras,

for the award of the degree of MASTER OF TECHNOLOGY, is a bona fide record of

the research work done by her under my supervision. The contents of this thesis, in full

or in parts, have not been submitted to any other Institute or University for the award of

any degree or diploma.

Dr. V Kamakoti

Project Guide

Professor

Dept. of Computer Science and Engineering

IIT-Madras, 600 036

Place: Chennai

Date: 21st June 2016

## **ACKNOWLEDGEMENTS**

I would like to express my earnest gratitude to my adviser Prof.V.Kamakoti whose energy, passion and support has been a tremendous source of inspiration throughout my project. I would like to extend my sincere thanks to my co-adviser G.S.Madhusudhan for guiding me throughout the project. I would like to express my special thanks and deepest gratitude to Rahul Bodduna for his valuable suggestions and guidance throughout the project. Finally, I would like to extend my thanks to all my friends because of whom my graduate experience has been one that I would cherish forever.

#### **ABSTRACT**

Multi-core processors dominate the microprocessor industry as the scaling of single core processor performance is rapidly reaching saturation. Designing multi-core processors presents various new challenges. Especially, the design of memory subsystem is a huge challenge because of the complications involved in coherence management. As the cores become more numerous and more diverse, heterogeneous hierarchical coherence protocols are required. Hence, the design, verification and evaluation of advanced memory subsystems become very difficult.

This dissertation uses the Manager-Client pairing method as an attempt to overcome these challenges and enable rapid construction of coherence hierarchy for multi-core processors. Manager-Client pairing provides a standardized coherence communication interface that provides protocol encapsulation. This reduces the complexity in the designing and verification of hierarchical coherence protocols. Each tier can be verified and evaluated in isolation. As a result, bug-free design with protocol heterogeneity can be created without much difficulty. This enables the architects to focus on performance enhancement rather than on debugging and verifying correctness of coherence implementation. The implementation of flat MOESI protocol using Manager-Client pairing and Tilelink protocol is presented in this dissertation. This can be replicated to construct the coherence hierarchy tiers. The memory hierarchy constructed is integrated with the I-class processor of Shakti processor series and the functional correctness of the design is verified.

# TABLE OF CONTENTS

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CKN(  | DWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                            | i  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BSTR  | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                     | ii |

| Ll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IST O | F TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                | v  |

| ABSTRACT       ii         LIST OF TABLES       vi         ABBREVIATIONS       vi         1 Introduction       1         1.1 Cache Coherence       2         1.1.1 MOESI Protocol       3         1.2 Manager Client Pairing       4         1.3 Organization       5         2 Manager-Client Pairing       6         2.1 Problem       6         2.2 Manager-Client Pairing       7         2.3 Basic Functions of MCP       8         2.4 MCP Interface for Coherence Hierarchy Construction       10         2.5 Working of MCP       12         3 Bluespec System Verilog       16         3.1 Limitations of Verilog       16         3.2 Bluespec       16         3.3 Features of Bluespec       17         3.3.1 Modules and Interfaces       17 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BBRE  | ### ACT ### STABLES  FOF TABLES  FOF FIGURES  EVIATIONS  ***Oduction  Cache Coherence  1.1.1 MOESI Protocol  3 Manager Client Pairing  4 Organization  5 ***Organization  ***Manager-Client Pairing  6 Problem  6 Manager-Client Pairing  7 Basic Functions of MCP  8 MCP Interface for Coherence Hierarchy Construction  10 Working of MCP  22 **Spec System Verilog  Limitations of Verilog  16 Bluespec  16 Features of Bluespec  17 |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Intr  | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.1   | Cache Coherence                                                                                                                                                                                                                                                                                                                                                                                                                         | 2  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 1.1.1 MOESI Protocol                                                                                                                                                                                                                                                                                                                                                                                                                    | 3  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.2   | Manager Client Pairing                                                                                                                                                                                                                                                                                                                                                                                                                  | 4  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.3   | Organization                                                                                                                                                                                                                                                                                                                                                                                                                            | 5  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mar   | ager-Client Pairing                                                                                                                                                                                                                                                                                                                                                                                                                     | 6  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.1   | Problem                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.2   | Manager-Client Pairing                                                                                                                                                                                                                                                                                                                                                                                                                  | 7  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.3   | Basic Functions of MCP                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.4   | MCP Interface for Coherence Hierarchy Construction                                                                                                                                                                                                                                                                                                                                                                                      | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.5   | Working of MCP                                                                                                                                                                                                                                                                                                                                                                                                                          | 12 |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Blue  | espec System Verilog                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.1   | Limitations of Verilog                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.2   | Bluespec                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.3   | Features of Bluespec                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 3.3.1 Modules and Interfaces                                                                                                                                                                                                                                                                                                                                                                                                            | 17 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 3.3.2 Data Types                                                                                                                                                                                                                                                                                                                                                                                                                        | 18 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 3.3.3 Rules                                                                                                                                                                                                                                                                                                                                                                                                                             | 19 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 3.3.4 Methods                                                                                                                                                                                                                                                                                                                                                                                                                           | 19 |

|   | 3.4 | TLM Library                | 20 |

|---|-----|----------------------------|----|

|   | 3.5 | Tile Link                  | 22 |

| 4 | Imp | lementation of MCP         | 23 |

|   | 4.1 | Tile Link Architecture     | 24 |

|   | 4.2 | Working of MCP             | 25 |

|   |     | 4.2.1 Processor            | 25 |

|   |     | 4.2.2 Client               | 26 |

|   |     | 4.2.3 Manager              | 29 |

|   |     | 4.2.4 Working of Hierarchy | 30 |

| 5 | Con | clusion and Future Work    | 34 |

# LIST OF TABLES

| 2.1 | Comprehensive list of the base functions required for communication between processors, clients, managers and memory in MOESI protocol | ç  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Components of RequestDescriptor                                                                                                        | 21 |

| 3.2 | Components of RequestData                                                                                                              | 21 |

| 3.3 | Components of TLMResponse                                                                                                              | 22 |

| 4.1 | Channels of Tilelink                                                                                                                   | 24 |

| 4.2 | Description of fields of Tilelink Protocol                                                                                             | 25 |

# LIST OF FIGURES

| 1.1 | State transition beginning with data in E state                       |    |  |

|-----|-----------------------------------------------------------------------|----|--|

| 1.2 | State transition beginning with data in S state                       | 4  |  |

| 1.3 | Construction of coherence hierarchy using MCP                         | 4  |  |

| 2.1 | Coherence Hierarchy                                                   | 7  |  |

| 2.2 | Inclusion of Protocol layer in the memory hierarchy                   | 11 |  |

| 2.3 | Interface between Manager and Client                                  | 12 |  |

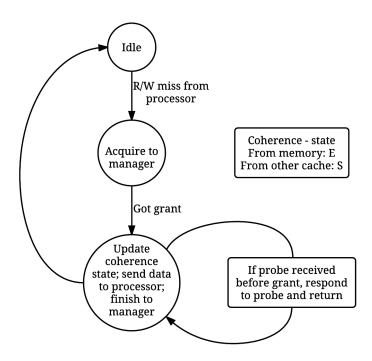

| 2.4 | MCP State Machine for Data Acquisition                                | 13 |  |

| 2.5 | Propagation of data acquisition within a coherence realm              | 14 |  |

| 2.6 | Propagation of data acquisition through different coherence realms .  | 15 |  |

| 3.1 | Representation of methods, interfaces and rules in a module hierarchy | 18 |  |

| 3.2 | Representation of TLMSendIFC and TLMRecvIFC                           | 21 |  |

| 4.1 | MCP hierarchy                                                         | 23 |  |

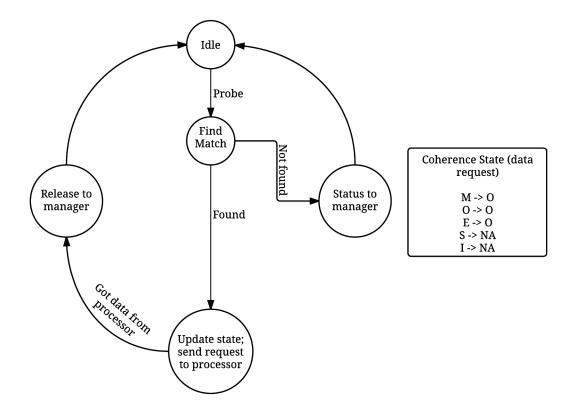

| 4.2 | Acquire-Grant-Finish in Client                                        | 26 |  |

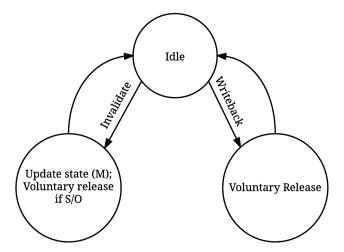

| 4.3 | Voluntary Release by Client                                           | 27 |  |

| 4.4 | Probe-Release in Client                                               | 28 |  |

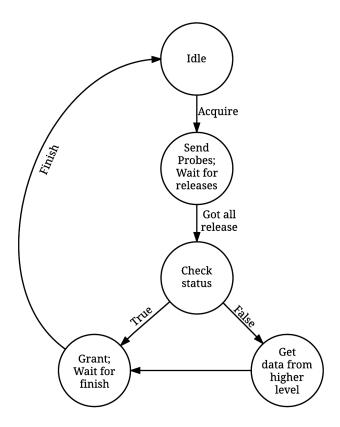

| 4.5 | Acquire-Grant-Finish in Manager                                       | 29 |  |

| 4.6 | Handling Voluntary Release in Manager                                 | 30 |  |

| 4.7 | Handling Read-Miss                                                    | 32 |  |

| 4.8 | Handling Write-Miss                                                   | 33 |  |

| 4.9 | Handling Write-Back                                                   | 33 |  |

|     |                                                                       |    |  |

# **ABBREVIATIONS**

MCP Manager-Client Pairing

**BSV** Bluespec System Verilog

HDL Hardware Description Language

**ASIC** Application Specific Integrated Circuit

**FPGA** Field Programmable Gate Array

**SOC** System on Chip

**RTL** Register Transfer Level

**IP** Internet Protocol

**CPU** Central Processing Unit

## **CHAPTER 1**

## Introduction

In the recent years, there has been a shift in focus towards multi-core processors due to the limitations of performance-scaling in single-core design. Parallelism in terms of multi-threading in multi-core processors improve performance by faster execution, better system utilization and lower power consumption. Cache hierarchy is often used with multi-core processor design in several applications for optimal performance. The use of shared memory presents numerous challenges. With multiple caches sharing single memory, data traffic becomes huge and it may present a performance bottleneck. Hierarchical clustered cache design is one possible solution to this problem. Grouping cores and their caches in clusters reduces network congestion by localizing traffic among several hierarchy levels, potentially enabling much higher scalability.

In a shared memory system, cache coherence is required for consistent view of memory across all the cores. As the cores become more diverse, there is a need for sophisticated coherence management. In hierarchical clustered cache design, each cluster may operate with a different coherence protocol depending on its application. With multiple levels of cache, this leads to a hierarchy of coherence protocols. New states have to be introduced to manage multiple coherence protocols in single design. The complexity of the design increases exponentially with increase in number of coherence protocol states, which makes the testing and verification of the design very difficult. This limits the scalability of the shared memory design.

The challenges in designing, testing and verifying advanced hierarchical cache coherence protocols can be overcome by the use of standardized coherence communication interface that provides protocol encapsulation. This dissertation presents the implementation of this standardized interface by adapting the Manager-Client pairing technique.

## 1.1 Cache Coherence

In a shared memory environment, the private processor caches may contain copies of data which may be dirty with respect to main memory. Cache coherence handles the management and distribution of data in such cases. Without coherence, the consistency model of architecture could be violated. That is when a private processor cache commits a store which is not being observed in the local cache of other processors, it breaks the consistency among the copies of data stored in the private processor caches. This affects the fundamental way in which the processors communicate with each other in a shared memory environment. The loads and stores performed by every processor should be observed by every other processor for functional correctness and cache coherence ensures that this behavior is maintained.

Cache coherence in hardware is accomplished through the addition of state bits to the data in cache, which indicates the coherence state of the data. The coherence state associated with the data depends on the coherence protocol used. The basic coherence states are invalid, shared and modified. Invalid state indicates whether the copy of data in cache is valid or not. Shared state of data implies that one or more of other caches also contain the copy of the same data. When a private processor cache commits a store, that copy of data is stored in modified state. These provide the basic mechanisms required to maintain coherency in the caches. A processor can read from its local cache only if the data is valid. Also, when a local copy of data is written by the processor, all other shared copies are invalidated. And the copy written is put in modified state. The two major classes are coherence protocols are broadcast based protocols and directory based protocols. In the directory based coherence management, the coherence state of all the data in the local caches is maintained in a directory. Whenever a processor has to perform read or write, the request is sent to the directory and the operation is performed if the required permissions are granted by the directory. In a broadcast based protocol, read or write miss is broadcasted through a shared bus and every local cache is snooped to check if the requested data is present in them. Also, when a processor performs a store on a shared copy of data in its local cache, invalidation request is sent to other caches to invalidate the other copies of that data. The invalidation of the shared copies in the event of a write operation by the processor is done in invalidation based

protocols. There is another variant of coherence protocol which handles write-hit in a different manner. Instead of invalidating the shared copies, the written value is broadcasted to all the caches that share this data and they are updated with the new value. This protocol is referred to as the update-based protocol.

The choice of a coherence protocol primarily depends on the application. Different protocols can be best suited for different hardware implementations. In this dissertation, broadcast based MOESI coherence protocol is used.

#### 1.1.1 MOESI Protocol

As already mentioned, we will be using broadcast based MOESI protocol, which will handle write-hit by invalidation. Initially, when the data is fetched from the memory, it is stored in Exclusive(E) state, as it will be the only copy of that data among the caches. When this data is read by some other cache, it is no longer an exclusive copy. So, the state is changed to Owner(O) and the cache which read this data will store it in Shared(S) state. When the data in Shared(S) state is read by other caches, its state does not change.

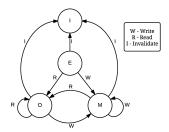

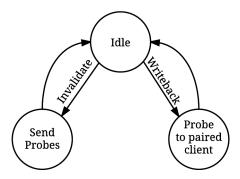

Figure 1.1: State transition beginning with data in E state

Reading of data in Owner(O) state, by other caches does not change the state of the local copy. However, writing of data in Owner(O) state or Shared(S) state, by the processor, changes its state to Modified(M) and the invalidate request is sent to other shared copies. Writing of data in Modified(M) state, will cause it to remain in modified state. When data in Exclusive(E) state is written, its state is updated as Modified(M), but invalidate request is not sent out as there are no shared copies to invalidate. The data in any coherence state, when invalidated, is put in Invalid(I) state. This transition of coherence states is shown in Figures 1.1 and 1.2.

Figure 1.2: State transition beginning with data in S state

## 1.2 Manager Client Pairing

Manager-Client pairing(MCP) is a method used to resolve the issues of heterogeneous integration of hierarchical coherence protocols. It provides a standardized interface definition, to rapidly construct and integrate coherence hierarchies. This reduces the complexity of the hierarchical coherence design by taking the native functioning of a given component protocol and mapping these to corresponding MCP methods. Therefore, the details of the component protocol's implementation gets abstracted away from the composition of the hierarchy, hidden behind an interface layer.

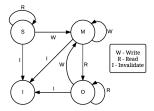

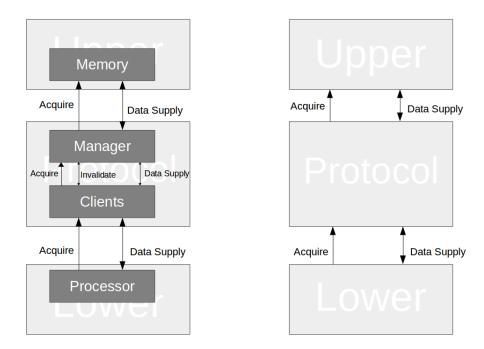

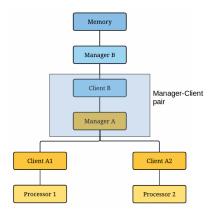

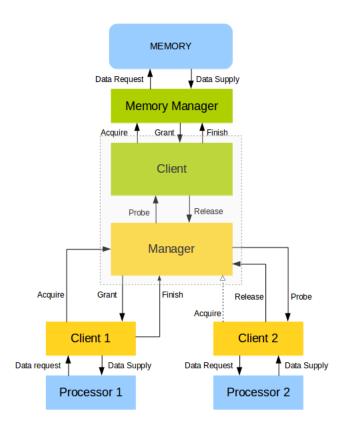

A coherence realm in the memory hierarchy consists of a single upper interface at

Figure 1.3: Construction of coherence hierarchy using MCP

the Manager and multiple lower interfaces at the Clients as shown in Figure 1.3. The interfaces are designed such that the upper interface of one coherence realm can plug into the lower interfaces of any other coherence realm without any additional modification, and creating Manager-Client pairs at the junction points. This allows us to construct hierarchies with ease. The responsibility of coherence management is localized in the hierarchical tiers. The verification and validation can be done in isolation in all of these component parts of the coherence hierarchy. The processor and the main

memory can be mapped seamlessly to the dangling interfaces of the MCP, completing the memory hierarchy.

# 1.3 Organization

The remainder of the dissertation is arranged as follows:

Chapter 2 presents the Manager-Client pairing framework.

**Chapter 3** presents a brief overview of Bluespec and its features. Bluespec is the HDL used to design the memory hierarchy.

Chapter 4 provides the implementation details of MCP.

**Chapter 5** presents the conclusion and possible future work.

## **CHAPTER 2**

# **Manager-Client Pairing**

As we move towards multi-core processors, there is an increasing need for sophisticated coherence management. When cache hierarchies are used in the design, we also need to introduce coherence management hierarchies to achieve data consistency. The hierarchical coherence protocol based design increases the complexity in terms of the ease of designing, testing and verification. Also, this complexity increases exponentially with the addition of more coherence states in the protocol. This in turn, strains the interaction between the hierarchy tiers.

Manager-Client Pairing (MCP) is a method to design hierarchical coherence protocols by formally defining and limiting interactions between different levels of the hierarchy. This enables composition in the coherence hierarchy design, which makes the designing of several complex designs much faster by restricting the complexity of design to a small set of protocol component parts.

#### 2.1 Problem

During the recent years, there has been a shift in focus towards multi-core processors because of the advantage it has over single-threaded designs in terms of power and performance. The addition of cache hierarchies in multi-core processors makes the process of fetching data from the memory faster compared to having single level of cache. However, cache hierarchy presents a problem of scalability, mainly due to the burden of coherent data management.

Data coherence management is a major challenge in hardware design with multiple cores. It presents a performance bottleneck as there are limits in terms of scalability presented by both directory based and broadcast based coherence protocols, thus requiring hierarchical coherence protocol design to overcome this. To achieve this, a

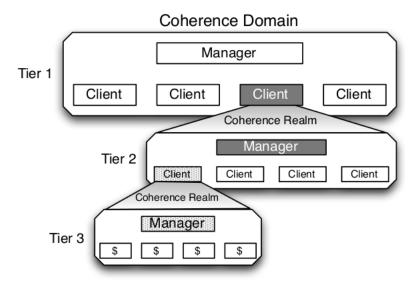

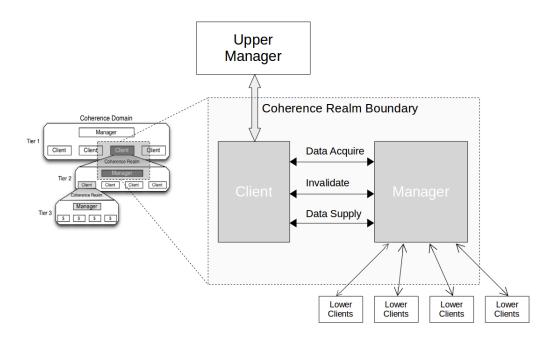

flexible framework is required, which supports variable width and depth of hierarchy. Figure 2.1 shows a model of coherence hierarchy.

The current approach to build such a framework is to design a glue layer to tie low-level

Figure 2.1: Coherence Hierarchy

coherence protocols together. This often results in changes to the low-level protocols. A complex sub-state replication is required which encodes all hierarchy information into protocol state. Therefore, more states need to be managed which leads to a complex state machine. Also, making changes to the hierarchy is difficult as a new solution has to be developed for each change. As a result, there is an abundance of large, complex, inflexible and highly specialized coherence protocols.

# 2.2 Manager-Client Pairing

Manager-Client pairing(MCP) is a powerful new approach to design coherence hierarchies. MCP employs a client-manager model, which gives a simple coherence protocol interface for clear communication between the entities that use data(clients) on one side and the mechanisms that maintain the coherence of the users(managers) on the other side of the interface. This encapsulates each tier of the coherence hierarchy so that each component can be dealt with in isolation. Application of MCP solves the state-space explosion problem and reduces the complexity in designing hierarchical coherence architecture. As the interface is standardized with independent tiers, a multi-core pro-

cessor design can be partitioned in to arbitrarily deep hierarchies to apply MCP, which ensures rapid design of coherence hierarchies.

It precisely defines the functions to be carried out by the Client and Manager to maintain coherence and reduces the fundamental requirements of a coherence protocol into a modular and generic set of base functions. Based on these base functions, coherence protocol communication is standardized by the generic Manager-Client interface. Thus, by converting stand-alone coherence protocols into coherence-tier building blocks, MCP aids in the rapid development of multi-tier coherence hierarchies.

Cache coherence protocols are responsible for maintaining a consistent view of memory across all the caches of a coherence domain, in a shared memory environment. The responsibilities of the coherence protocol include upgradation or degradation of coherence state of data and deciding how updates to data are propagated through the system. These functions can be divided between two kinds of agents:managers that manage propagation of updates to data and clients which hold the coherence state of data and performs data acquisition when necessary.

These roles are first formally defined for non-hierarchical MOESI protocol and then re-examined to derive interfaces that enable composition of complex coherence hierarchies.

## 2.3 Basic Functions of MCP

The coherence protocol used here is MOESI protocol. It has five states: Modified(M), Owner(O), Exclusive(E), Shared(S) and Invalid(I). The client which has the data in the Exclusive state or the Modified state has the only copy of that data. Although the client with data in Owner state does not have a unique copy of the data, it is the only client among the sharers, which can respond to a request. Also, at any point of time, only one of these states(M,O,E) can be present among the clients of the same level. Therefore, data propagation can be easily handled by the manager as it can directly grant data from the only client in M/O/E state to the client which requested that data block.

Let us consider the handling of write operation in MOESI protocol. After write, the copy of the data block which is written, becomes dirty with respect to the sharers. In order to track this information, the Modified(M) state is used by the client. In the event of a write hit in the processor, the client changes the state of that data to Modified(M) and sends an invalidate request if the previous state of the data written was Owner(O) or Shared(S) state. During write-back, if the data block is in M/E state, it is directly written in the main memory. If in Owner(O) state, in addition to sending the data to main memory, all the other shared copies are invalidated. If the data is in Shared(S) or Invalid(I) state, the write-back operation is not performed. Table 2.1 summarizes and enumerates a comprehensive list of the base functions required for communication between processors, clients, managers and memory in MOESI protocol. These will be used as an aid in the developing a generic protocol interface.

The basic requirements that have to be satisfied by the agents involved in coherence

Table 2.1: Comprehensive list of the base functions required for communication between processors, clients, managers and memory in MOESI protocol

| Origin<br>Agent | Action<br>Type      | Action     | Description                                                                                                | Destination<br>Agent | Response Action                   |

|-----------------|---------------------|------------|------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------|

|                 | Data<br>Acquisition | GetData    | R/W miss: Get data to complete CPU request                                                                 | Client               | GetData                           |

| Processor       | Invalidation        | FwdInval   | Write hit: Invalidate<br>shared copies                                                                     | Client               | FwdInval                          |

|                 | Data Supply         | DoWrite    | Block replacement;<br>writeback                                                                            | Client               | DoWrite                           |

|                 |                     | GrantData  | Supply Data                                                                                                | Client               | GrantData                         |

|                 | Data                | GetData    | Request from processor                                                                                     | Manager              | GetData                           |

|                 | Acquisition         | GetData    | Request from manager;<br>change state to O                                                                 | Processor            | GrantData                         |

|                 |                     | DoInval    | Invalidate copy in local cache if hit in O/S state                                                         | Processor            | CompleteInvalidate                |

| Client          | Invalidation        | FwdInval   | Change state to M;<br>forward request to<br>manager if O/S state                                           | Manager              | DoInval                           |

| Chem            | Data Supply         | DoWrite    | Only when in M/O/E.<br>Invalidate shared copies<br>when O                                                  | Manager              | DoWrite; DoInval                  |

|                 |                     | GrantData  | Got data from processor                                                                                    | Manager              | GrantData                         |

|                 |                     | GrantData  | Got data from manager;<br>State – E if from mem, S<br>otherwise; send data to<br>processor                 | Processor            | Complete R/W;<br>when write, send |

|                 | Data<br>Acquisition | GetData    | Gets data from client if it is in M/O/E state                                                              | Client               | GetData                           |

|                 | -                   | GetData    | If no hit in any client                                                                                    | Memory               | GrantData                         |

|                 | Invalidation        | DoInval    | Invalidate shared copies                                                                                   | Client               | DoInval                           |

| Manager         | Data Supply         | GrantData  | Data supply from M/O/E<br>clients or from main<br>memory; indicate if data<br>obtained from main<br>memory | Client               | GrantData                         |

|                 |                     | DoWrite    | Forward request to higher level                                                                            | Memory               | GrantWrite                        |

| Memory          | Data Supply         | GrantData  | Supply Data                                                                                                | Manager              | GrantData                         |

| IVICIIIOI y     |                     | GrantWrite | Finish write                                                                                               | N/A                  | N/A                               |

management are as follows. Clients should be able to respond whether or not they have the requested data block. If the cache associated with a client encounters a read or write miss, the client should be able to place a request to the manager. Managers should accept data requests from clients, and provide data from the appropriate location. The client should also be able to send out invalidate request when necessary and the manager should forward it to all the other clients in the same level. In case of write back, the clients and managers should forward the data till the main memory.

As the management of coherency is completely handled by the client, the manager need not be aware of any internal change of coherence states. The manager only has to keep track of whether the data is obtained from the clients of the same level or from higher level. This information is used by the clients to appropriately update the coherence states.

# 2.4 MCP Interface for Coherence Hierarchy Construction

Now, we need to construct coherence hierarchy. From the basic functions performed by the agents of coherence realm, as inferred from Table 2.1, considerable similarities in the interactions between processor and client and the interactions between manager and memory can be observed. In both cases, the data is provided by the data supplier when requested. The mechanism of data transfer is same as that in main memory when the data is requested from the lower levels of the memory hierarchy. This information allows us to create interfaces that allow recursion, which can be used to develop hierarchies.

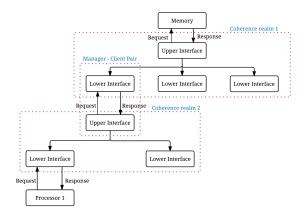

By examining the Figure 2.2, we observe that the replacement of the implementation details of the coherence protocol with a black box yields a self-similar upper and lower interface. Not only does this insight enable recursion through a simple interface definition, but also allows encapsulation of the coherence protocols used in the hierarchy, reducing design complexity.

From this we can see that there are at least two necessary components to the MCP

Figure 2.2: Inclusion of Protocol layer in the memory hierarchy

interface: R/W request for data from lower to higher level(write during write-back from processor), and Data supply from higher to lower as well as from lower to higher levels. Manager is paired with a client in the next higher-up client(or to the memory in the highest level). By requesting the paired client when necessary, the manager can perform data transfer without having to worry about the coherence protocol in the higher level. The mechanism of data transfer can be the same as that in main memory, irrespective of the level of memory hierarchy being communicated with. Similarly, the clients of the lower level handle the coherence management silently, and the manager need not be aware of any change in the coherence state within the clients. This is much like how a processor is unaware of the coherence in the caches implemented; it simply requests for data from higher level and receives it.

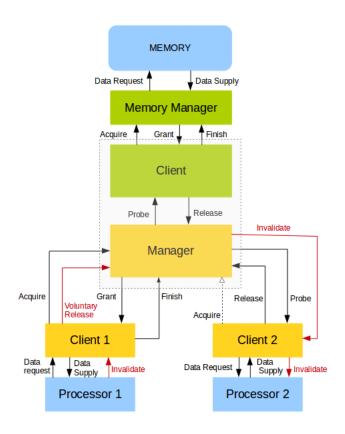

The other important detail that must be addressed is the propagation of invalidation signal. When a write-hit happens in a processor, the other shared copies of the data have to be invalidated. As the client handles all the coherence management, the processor notifies the client whenever there is a write-hit. The client forwards that request to the manager, if necessary after updating the current coherence state of the data block being written. The manager then has to forward this request to every other client in that

level, so that all the shared copies could be invalidated. Similarly when a client receives invalidate request from the manager, it should invalidate its local copy if it has that data. This provides us the third and final component of the MCP interface: Invalidation. Figure 2.3 outlines a brief description of the working of MCP interface.

Figure 2.3: Interface between Manager and Client

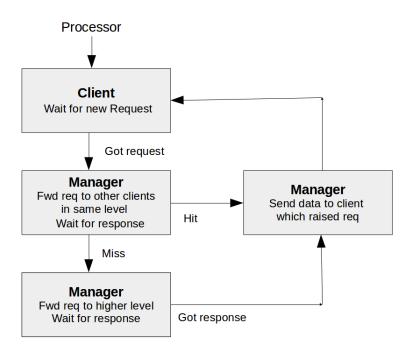

# 2.5 Working of MCP

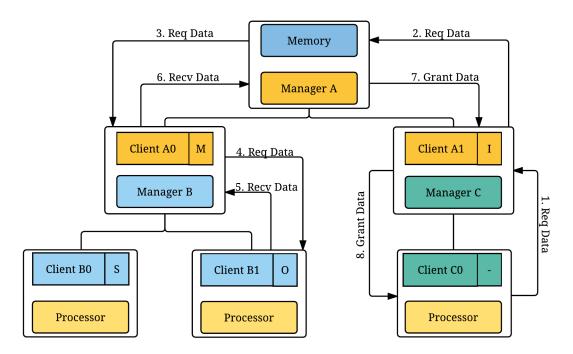

With a common interface defined, we can begin using coherence protocol agents as building blocks in the construction of hierarchical coherence protocols. By expanding the scope of client agents to also monitor coherence realms in addition to processor caches, the coherence effort can be distributed over several protocols by layering the protocols in a tiered fashion. When manager of one coherence realm cannot satisfy the request of one of the clients of lower level, it recursively sends request to the manager of the higher level, through its paired client. In this way, hierarchies of coherence protocols are established. Figure 2.4 explains the algorithm. To aid in understanding and to highlight some important details of MCP, two examples are presented. In both examples we have a top-tier coherence realm A, that implements MEI protocol to manage two lower coherence realms, B and C, both implementing MOESI. Manager A resides

Figure 2.4: MCP State Machine for Data Acquisition

at memory and therefore has no need for a gateway client, being the highest manager agent in the system. Similarly, clients B0, B1 and C0 do not have a matching manager agent because there are no lower tiers to be tracked. They are gateways for processors' private caches, not further coherence realms.

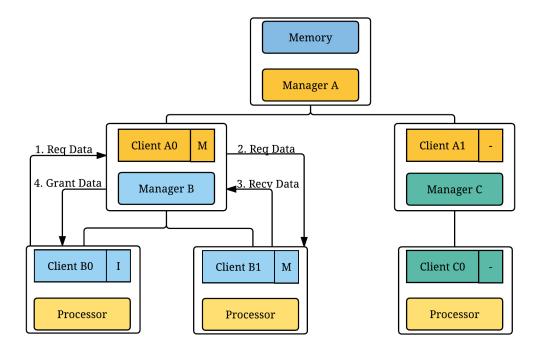

In Figure 2.5, an example of a realm-hit from a read request is shown. The processor below client B0 initiates the sequence with a request to acquire data. The client forwards the request to the manager. The manager checks with its paired client to find out if the data requested is available in any of the other clients of the B level. As the clientA0 represents all the agents of the lower level, it can provide the information that the requested data is available in clientB1. Now the manager obtains data from clientB1, after which the state of it changed to O and it is given to the clientB0 to satisfy the request. As the clientA0 follows MEI protocol, it stores the states of data in both the clients in B level in M state.

From this example we see a clear demonstration of the encapsulation of the coherence realm provided by MCP. The request in the example was serviced only within the scope of coherence realm B because the gateway client A0 had sufficient information to allow the request to proceed in a coherent manner. Furthermore, despite a change in

the state of the coherence realm's manager B from M to O, the change does not need to be reflected in client A0 since it is a silent downgrade. Because there is no need to notify manager A of this activity, there is the benefit of reduced traffic while preserving encapsulation. Additionally, if either client B0 or B1 were to modify the state of this data to M later, it can happen without the knowledge of the agents in the higher level.

Requests can however cross coherence realm boundaries, referred to as a realm-miss,

Figure 2.5: Propagation of data acquisition within a coherence realm

when no client agent in that realm has the requested data block, as shown in Figure 2.6. Here the MCP algorithm propagates the request all the way to the top tier where it encounters manager A and memory instead of a client agent. Since there is no higher tier to consult, the top manager always services the request to make forward progress; there is no gateway client at the top level.

In this example, the request is from the ClientC0. Upon requesting the ClientA1, ManagerC gets the information that no client agent in realm C has the requested data block. So, the request is now forwarded to the higher-level, to ManagerA. Now, ManagerA requests ClientA0, and waits for response as there is a hit in realm B. The request propagates to the client which contains the data, through the ManagerB. The data reaches ManagerA through ClientA0 and from ManagerA, the data propagates through ClientA1 and ManagerC to reach ClientC0, which requested the data. Client A1 stores

Figure 2.6: Propagation of data acquisition through different coherence realms

the data in the M state as it is not an exclusive copy. ClientC0 stores it in S state as it is a shared copy. The state of data does not change in realm B as the request was serviced by client in O state. Therefore, state of data in ClientA0 also does not change.

Although more complex, this second example further serves to demonstrate the decoupling of the protocol coherence realms from one another. When a gateway client encounters a miss, the entire coherence realm effectively collapses into a single node from the perspective of the manager in the next tier. The next-tier manager does not need to be aware of any details of how the coherence realm guarded by the gateway client operates just as long as it knows how to interact with the gateway client (which obviously it will being the manager). Similarly, when coherence realm C was being updated, this was done opaquely from the perspective of manager A. This coherence realm encapsulation is what enables efficient composition of coherence protocol hierarchies without the need for ad-hoc sub-state replication. Despite the MEI protocol of manager A managing two realms using different protocols (with additional, independent S and O states), the protocol of realm A was never aware of this since it had no need to store information outside its own protocol scope. Furthermore, each component protocol may be validated in isolation.

## **CHAPTER 3**

# **Bluespec System Verilog**

Bluespec System Verilog is a Hardware Description Language (HDL), which is used for specification, synthesis, modeling and verification of ASIC and FPGA design. With a radically different approach to high-level synthesis, bluespec offers significantly higher productivity. It allows designers to express intended hardware through high-level constructs, where all behavior is described as a set of guarded atomic actions.

# 3.1 Limitations of Verilog

Verilog focusses more on simulation than logic synthesis. The source text of verilog often explicitly contains aspects of circuit that could be readily determined by the compiler, such as size of registers, width of busses etc. This makes the design less portable. Handling concurrency in hardware is relatively difficult in verilog as the designer should manage all the aspects of handshaking between combinational circuits. Shared use of register and other memory resources should also be elaborated. The behavioral specification of design in verilog often consumes multiple clock cycles. Attempts to resolve this problem results in a highly unreadable code with possible bugs. In practice, this problem is solved by separating the combinational and sequential parts of the circuit. Due to these shortcomings, the synthesis and verification of hardware in verilog is slowed down. This is a huge problem during the design of SOC.

# 3.2 Bluespec

Bluespec is based on atomic transactions, which increases the level of concurrency abstraction above SystemC and RTL without compromising the control over hardware design. It enables automatic synthesis of complex control logic, which is the source of many bugs. This results in highly adaptable, reusable and reconfigurable designs.

Control-adaptive parameterization in bluespec provides flexibility, where a significantly different micro-architecture can be generated by changing the parameters in the design with the associated control structures generated automatically. Bluespec allows user-defined data types and static type checking. It provides several features of the modern high level languages and all of them can be synthesized.

In recent times, several attempts have been made to move the hardware design language towards a more software like specification of the circuit behavior. Languages like C, C++ are used to express designs as sequential programs. However, the semantic gap between the software model and the hardware results in suboptimal designs with unpredictable speed and area. Bluespec System Verilog tackles this problem by building upon the traditional hardware semantics. It exploits advanced concepts from software only for static elaboration and static verification. It uses the standard hardware structure model of verilog such as modules, module instances, hierarchy etc. For communication between modules it uses the System verilog model of interfaces and interface instances. These added with the advanced features of the high level languages, makes designing and verification in bluespec much faster.

# 3.3 Features of Bluespec

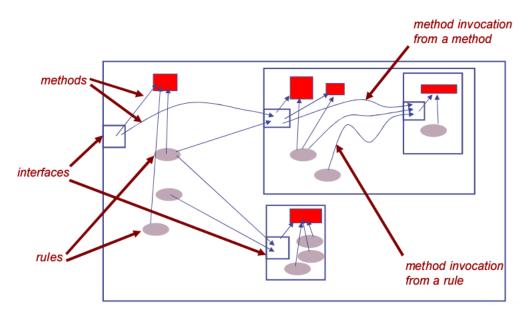

#### 3.3.1 Modules and Interfaces

Module is the basic element of the hardware design hierarchy in bluespec. A module can be instantiated multiple times, and also different parameters can be passed during every instantiation. Unlike verilog, bluespec does not have input, output and in-out pins as interface to modules. Methods are used to drive signals and busses in and out of modules. These methods are grouped together into interfaces. Modules contain rules, which use methods in other modules. Figure 3.1 shows how these methods, interfaces and rules fit into a hierarchy of modules.

In BSV, the interface declaration is done separately, outside the module definition. This allows declaration of common interfaces which can be used in multiple modules, without having to declare them repeatedly. All the modules which share the same inter-

Figure 3.1: Representation of methods, interfaces and rules in a module hierarchy

faces also share same methods and therefore share same number and type of inputs and outputs.

#### 3.3.2 Data Types

In verilog, all the representation is done in bits. Also, ultimately in hardware all computation is done in bits. However, representation in terms of integers, floating point numbers, fixed point numbers etc, makes the process of coding much easier. Different representations may be more appropriate depending on the application environment. By separating out the type abstraction from its bit representation, we can easily change representations without modifying or breaking the rest of the program.

In BSV, every variable has a type and only the values of compatible types can be assigned to a variable. The BSV compiler provides a strong, static type-checking environment. Type checking is done before the program elaboration and it ensures that the object types are compatible and the conversion functions are valid for the context. Bluespec also allows the usage of user-defined types. BSV has a typeclass which can be considered as a set of types. It implements overloading across related data types. Overloading is the ability to use a common name for a collection of types, with the specific type for the variable being chosen by the compiler based on the types on which it is actually used. Functions and operators are shared by all the data types within a

typeclass.

Some common scalar types used in Bits typeclass are Bit#(n), Bool, UInt#(n) and Int#(n). The values stored in registers, FIFOs and other memory elements and also the values passed by wires, must be in the Bits typeclass. Other common data types include Integer, which belongs to the Arith typeclass and String, which belongs to the Literal typeclass etc.

#### **3.3.3** Rules

Rules manage the movement of data from one state to another, within the module. It consists of two parts: rule conditions and rule body. Rule conditions are boolean expressions which decide whether the rule can be fired. Rule body is a set of actions for state transitions. Rules in BSV are atomic. The actions within the rule completely describes the state transition. The process of determining the functional correctness of a design is greatly simplified by one-rule-at-a-time semantics. That is, because of the atomic property of rules, each rule can be looked at in isolation, without considering the actions of the other rules to determine functional correctness. Multiple rules can be executed concurrently in the hardware implementation.

The actions in a rule are executed simultaneously. This can be thought of as similar to the execution of non-blocking statements in always blocks of verilog. Also, as the rule has atomic property, the entire body of rule is executed and there is no partial execution of a rule. When there are several rules within a module, the execution of rules is ordered by the compiler. No two rules can execute simultaneously. The ordering of the rules by the compiler is called scheduling.

#### 3.3.4 Methods

A method is a procedure which takes arguments and returns a value. It could also return a value without taking any arguments. It becomes a bundle of wires when translated into RTL. The method definition is written within the definition of the interface and it can be different in different modules sharing a common interface. A method also contains

implicit conditions which are handshaking signals and logic automatically generated by the compiler.

Methods are of three types: Value Methods, Action Methods and Action Value Methods. Value methods return a value. They do not alter any state within the module. Action methods cause actions to occur. They create state changes within the module. Action value methods are a combination of value methods and action methods. They cause state changes and also return values.

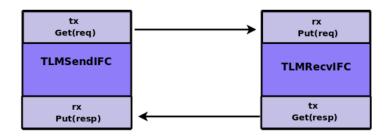

## 3.4 TLM Library

The TLM package includes definitions of interfaces, data structures, and module constructors which allow users to create and modify bus-based designs in a manner that is independent of any one specific bus protocol. Designs created using the TLM package are thus more portable as it allows the core design to be easily applied to multiple bus protocols.

The TLM interfaces define how TLM blocks interconnect and communicate. The TLM package includes two basic interfaces: The TLMSendIFC interface and the TLMRecv-IFC interface. These interfaces use basic Get and Put sub-interfaces as the requests and responses. The TLMSendIFC interface generates (Get) requests and receives (Put) responses. The TLMRecvIFC interface receives (Put) requests and generates (Get) responses. Additional TLM interfaces are built up from these basic blocks. The TLM-SendIFC interface transmits the requests and receives the responses. The TLMRecvIFC interface receives the requests and transmits the responses. This is represented in Figure 3.2.

The two basic data structures defined in the TLM package are TLMRequest and TLM-Response. By using these types in a design, the underlying bus protocol can be changed without having to modify the interactions with the TLM objects. A TLM request contains either control information and data, or data alone. A TLMRequest is tagged as either a RequestDescriptor or RequestData. A RequestDescriptor contains control information and data while a RequestData contains only data. Table 3.1 describes the

Figure 3.2: Representation of TLMSendIFC and TLMRecvIFC

components of RequestDescriptor and the valid values for each of its members. Table 3.2 presents the components of RequestData and the valid values for its members. Table 3.3 describes the components of a TLMResponse and the valid values for its members.

In the above BSV code definitions the compiler macros 'TLM\_TYPES are used

Table 3.1: Components of RequestDescriptor

| RequestDescriptor |                           |                                             |  |  |

|-------------------|---------------------------|---------------------------------------------|--|--|

| Member Name       | DataType                  | Valid Values                                |  |  |

| command           | TLMCommand                | READ, WRITE, UNKNOWN                        |  |  |

| mode              | TLMMode                   | REGULAR, DEBUG, CONTROL                     |  |  |

| addr              | TLMAddr#('TLM_TYPES)      | Bit#(addr_size)                             |  |  |

| data              | TLMData#('TLM_TYPES)      | Bit#(data_size)                             |  |  |

| burst_length      | TLMUint#('TLM_TYPES)      | UInt#(uint_size)                            |  |  |

| byte_enable       | TLMByteEn#('TLM_TYPES)    | Bit#(TDiv#(data_size, 8))                   |  |  |

| burst_mode        | TLMBurstMode              | INCR, CNST, WRAP, UNKNOWN                   |  |  |

| burst_size        | TLMBurstSize#('TLM_TYPES) | <pre>Bit#(TLog#(TDiv#(data_size, 8)))</pre> |  |  |

| prty              | TLMUInt#('TLM_TYPES)      | UInt#(uint_size)                            |  |  |

| lock              | Bool                      |                                             |  |  |

| thread_id         | TLMId#('TLM_TYPES)        | Bit#(id_size)                               |  |  |

| transaction_id    | TLMId#('TLM_TYPES)        | Bit#(id_size)                               |  |  |

| export_id         | TLMId#('TLM_TYPES)        | Bit#(id_size)                               |  |  |

| custom            | TLMCustom#('TLM_TYPES)    | cstm_type                                   |  |  |

Table 3.2: Components of RequestData

| RequestData    |                        |                 |  |  |

|----------------|------------------------|-----------------|--|--|

| Member Name    | Valid Values           |                 |  |  |

| data           | TLMData#('TLM_TYPES)   | Bit#(data_size) |  |  |

| transaction_id | TLMId#('TLM_TYPES)     | Bit#(id_size)   |  |  |

| custom         | TLMCustom#('TLM_TYPES) | cstm_type       |  |  |

in the typedef statements. A 'define statement is a preprocessor construct used to place prepackaged text values into a file. In this case, the macros contain parameters to be used in the data definitions. Placing the parameters in a separate file allows them to be easily modified for different protocol requirements.

Table 3.3: Components of TLMResponse

| TLMResponse    |                        |                             |  |

|----------------|------------------------|-----------------------------|--|

| Member Name    | DataType               | Valid Values                |  |

| command        | TLMCommand             | READ, WRITE, UNKNOWN        |  |

| data           | TLMData#('TLM_TYPES)   | Bit#(data_size)             |  |

| status         | TLMStatus              | SUCCESS, ERROR, NO_RESPONSE |  |

| prty           | TLMUInt#('TLM_TYPES)   | UInt#(uint_size)            |  |

| thread_id      | TLMId#('TLM_TYPES)     | Bit#(id_size)               |  |

| transaction_id | TLMId#('TLM_TYPES)     | Bit#(id_size)               |  |

| export_id      | TLMId#('TLM_TYPES)     | Bit#(id_size)               |  |

| custom         | TLMCustom#('TLM_TYPES) | cstm_type                   |  |

## 3.5 Tile Link