# 3-PHASE 3-WIRE AND 3-PHASE 4-WIRE GRID TIED ACTIVE FRONT END VOLTAGE SOURCE RECTIFIER CONTROL

A Project Report

submitted by

#### MOHAMED ANSHAD PARI

in partial fulfilment of the requirements

for the award of the degree of

Master of Technology (Power Systems and Power Electronics) and Bachelor of Technology

in

**Electrical Engineering**

THESIS CERTIFICATE

This is to certify that the thesis titled 3-PHASE 3-WIRE AND 3-PHASE

4-WIRE GRID TIED ACTIVE FRONT END VOLTAGE SOURCE

RECTIFIER CONTROL, submitted by MOHAMED ANSHAD PARI, to

the Indian Institute of Technology, Madras, for the award of the degree of Dual-

Degree (Bachelor of Technology & Master of Technology), is a bona fide

record of the project work done by him under my supervision. The contents of

this thesis, in full or in parts, have not been submitted to any other Institute or

University for the award of any degree or diploma.

Dr. Kamalesh Hatua

(Project Guide) Asst.Professor

Dept. of Electrical Engineering

IIT-Madras, 600 036

Place: Chennai

Date: 6th May 2015

#### ACKNOWLEDGEMENTS

It gives me great pleasure to express my sincere and heartfelt gratitude to Dr. Kamalesh Hatua for his excellent guidance, motivation and constant support throughout my project. I consider myself extremely fortunate to have had a chance to work under his supervision. I am grateful to him for instilling a passion in the domain of Power Electronics and Drives through his scholarly lectures on Machine Modelling and Power Electronic Control of Electric Machines. Working with him has enhanced my potential on a technical as well as on a personal level and has made the final year of my learning in IITM truly memorable amongst all the five years I had spent here.

I also thank Dr. Shanti Swarup for his valuable support as a mentor during my entire tenure as a student.

I thank Mr. Kothandaraman and Ms. Jayasudha for their help and advice in arranging the hardware setup.

I am truly wordless to express my gratitude to my fellow research scholar Jose Titus for being a pillar of support during my work. Discussions with him helped me to grasp the digital platform which made me a step ahead in my work and trouble shooting sessions with him who has an eagle eye, were worth an experience.

I deeply esteem my fellow students in the Laboratory, especially Parthasarathy and Vamshi Krishna for spending their invaluable time with me, in discussing about the project. I would also extend my thanks to Hridya, Deepthi, Pratap, Aloka, Shekhar, Saravanan, Rajendra, Guru and Poongothai for their support during my work.

This work could not have come to this stage without the support and encouragement from my family. My heartfelt thanks to all of them.

#### ABSTRACT

KEYWORDS: Active Front End Converter; Voltage Source Rectifier; Vector Control

The aim of the project is modeling and controlling of a 3-phase 3-wire and 3-phase 4-wire voltage source rectifier. These types of converters are generally classified as Active Front End Converter (FEC), since these are connected to front/utility side of the supply. The implemented converter can also be used as a replacement for a diode bridge rectifier for an induction motor drive. Active front end converter ensures bidirectional power flow between AC grid and DC bus. The front end converter maintains a fixed DC bus at all operating conditions. It draws sinusoidal current from the grid and have VAR compensation capability. In this project, vector control of FEC has been implemented in a synchronous reference frame, which is aligned with the a-phase grid voltage. Vector control ensures independent control of both active power and reactive power flow between AC grid and active front end rectifier.

Simulation studies are done for a 10 kVA 3-phase 3-wire and 3-phase 4-wire FEC using MATLAB/SIMULINK to verify the design of the power circuit and control algorithms. The control hardware is developed based on the TMS320F28335 DSP from Texas Instruments, which is indigenously developed in the laboratory. The system design and control software for 3-phase 3-wire and 3-phase 4-wire FEC are experimentally validated on a 10 kVA laboratory prototype. A simple algorithm in order to eliminate the lower order harmonics from the line current of FEC has been implemented.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                           |               |        |                                                                          |              |

|------------------------------------------------------------------------------------------|---------------|--------|--------------------------------------------------------------------------|--------------|

| LIST OF FIGURES                                                                          |               |        |                                                                          |              |

| $\mathbf{A}$                                                                             | ABBREVIATIONS |        |                                                                          |              |

| N                                                                                        | OTA           | TION   |                                                                          | $\mathbf{v}$ |

| 1                                                                                        | INT           | ROD    | UCTION                                                                   | 1            |

|                                                                                          | 1.1           | Back g | ground of the project                                                    | 1            |

|                                                                                          |               | 1.1.1  | Vector Control for FEC                                                   | 2            |

|                                                                                          | 1.2           | Power  | Structure of the System                                                  | 3            |

|                                                                                          | 1.3           | Goals  | of the Project Work                                                      | 4            |

|                                                                                          |               | 1.3.1  | Vector control of 3-phase 3-wire FEC and 3-phase 4-wire FEC              | 4            |

|                                                                                          | 1.4           | Organ  | isation of Thesis                                                        | 5            |

| 2 Modeling, Analysis and Control of 3-phase 3-wire and 3-p<br>4-wire Front End Converter |               |        | 6                                                                        |              |

|                                                                                          | 2.1           | Introd | luction                                                                  | 6            |

|                                                                                          | 2.2           | Vector | Control of FEC                                                           | 6            |

|                                                                                          | 2.3           | Ideal  | Operation of Front End Converter                                         | 9            |

|                                                                                          | 2.4           | Model  | ing of 3-phase 3-wire Front End Converter                                | 10           |

|                                                                                          | 2.5           | Contro | ol Strategy for FEC                                                      | 12           |

|                                                                                          |               | 2.5.1  | Phase Locked Loop (PLL)                                                  | 14           |

|                                                                                          |               | 2.5.2  | PI Controllers                                                           | 16           |

|                                                                                          |               | 2.5.3  | Feed-forward Terms and Inverter Gain                                     | 20           |

|                                                                                          |               | 2.5.4  | PWM generation                                                           | 21           |

|                                                                                          | 2.6           |        | nation of lower order harmonics from the line current of a se 3-wire FEC | 22           |

|                                                                                          |               | 2.6.1  | Harmonic elimination technique                                           | 23           |

|   | 2.7  | Three  | -phase Four-wire FEC                                                                        | 25      |

|---|------|--------|---------------------------------------------------------------------------------------------|---------|

|   |      | 2.7.1  | Modeling and control of 3-phase 4-wire FEC                                                  | 26      |

|   |      | 2.7.2  | Switching frequency distortions in line and neutral current                                 | 29      |

|   | 2.8  | Concl  | usion                                                                                       | 33      |

| 3 |      |        | ARE ORGANISATION AND CONTROL IMPLEMEN<br>OF FEC                                             | -<br>34 |

|   | 3.1  | Introd | luction                                                                                     | 34      |

|   | 3.2  | Brief  | Overview of the TMS320F28335                                                                | 34      |

|   | 3.3  | Curre  | nt and Voltage Sensing                                                                      | 35      |

|   | 3.4  | Three  | Phase Inverter Module                                                                       | 35      |

|   |      | 3.4.1  | Protection and Delay Card                                                                   | 36      |

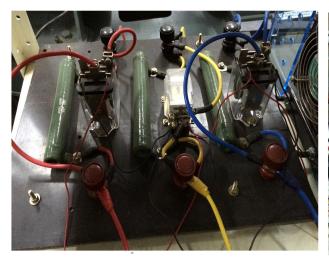

|   | 3.5  | Three  | Phase Line Side Filter and Common Mode filter                                               | 36      |

|   | 3.6  | Soft S | tart-up for FEC                                                                             | 37      |

|   | 3.7  | Hardy  | vare Setup                                                                                  | 39      |

|   | 3.8  | The F  | Per Unit System                                                                             | 41      |

|   | 3.9  | Design | n of Controllers                                                                            | 42      |

|   | 3.10 | Concl  | usion                                                                                       | 43      |

| 4 | RES  | SULTS  | S AND INFERENCES                                                                            | 44      |

|   | 4.1  | Introd | luction                                                                                     | 44      |

|   | 4.2  | Simul  | ation Results                                                                               | 44      |

|   |      | 4.2.1  | PLL Results                                                                                 | 44      |

|   |      | 4.2.2  | 3-phase 3-wire FEC results                                                                  | 48      |

|   |      | 4.2.3  | Elimination of lower order harmonic component from the line current of a 3-phase 3-wire FEC | 56      |

|   |      | 4.2.4  | 3-phase 4-wire FEC results                                                                  | 62      |

|   | 4.3  | Hardy  | vare Results                                                                                | 65      |

|   |      | 4.3.1  | PLL Results                                                                                 | 65      |

|   |      | 4.3.2  | 3-phase 3-wire FEC results                                                                  | 68      |

|   |      | 4.3.3  | 3-phase 4-wire FEC results                                                                  | 74      |

|   | 4.4  | Concl  | usion                                                                                       | 79      |

| 5 | CO   | NCLU   | ISION                                                                                       | 80      |

| - |      |        |                                                                                             | 23      |

| 5.1           | Summary of the Present Work | 80 |

|---------------|-----------------------------|----|

| 5.2           | Future Scope of Work        | 80 |

| REFERENCES 81 |                             |    |

# LIST OF TABLES

| 3.1 | Ratings of a single phase inductor | 37 |

|-----|------------------------------------|----|

| 3.2 | Ratings of common mode inductor    | 37 |

| 3.3 | PU base quantities                 | 42 |

| 3.4 | PI controller notations            | 42 |

| 3.5 | Controller parameters              | 43 |

# LIST OF FIGURES

| 1.1  | Power structure of the system                                                                                                           | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | 3-phase 3-wire FEC                                                                                                                      | 7  |

| 2.2  | $\alpha$ - $\beta$ and d-q frames phasor representation                                                                                 | 8  |

| 2.3  | Equivalent circuit and phasor diagrams of the FEC                                                                                       | 9  |

| 2.4  | 3-phase 3-wire FEC circuit diagram                                                                                                      | 10 |

| 2.5  | Vector Controller Loops                                                                                                                 | 13 |

| 2.6  | Control structure of FEC in $d$ - $q$ reference frame                                                                                   | 14 |

| 2.7  | PLL Block Diagram                                                                                                                       | 15 |

| 2.8  | Block diagram for $I_{sd}$ controller                                                                                                   | 18 |

| 2.9  | Block diagram for $I_{sq}$ controller                                                                                                   | 18 |

| 2.10 | Block diagram for $V_{dc}$ controller                                                                                                   | 20 |

| 2.11 | Controller Structure                                                                                                                    | 21 |

| 2.12 | Generation of SVPWM modulating signals from the SPWM modulating signals                                                                 | 22 |

| 2.13 | Control structure for $nth$ Harmonic elimination                                                                                        | 24 |

| 2.14 | Harmonic Extraction Algorithm                                                                                                           | 25 |

| 2.15 | 3-phase 4-wire FEC                                                                                                                      | 26 |

| 2.16 | xth phase half bridge FEC                                                                                                               | 26 |

| 2.17 | Controller block diagram for 3- $\phi$ 4-wire FEC                                                                                       | 28 |

| 2.18 | (a)<br>Zero-axis circuit of 3-phase 4-wire FEC(b)<br>Equivalent zero-axis circuit of 3- $\phi$ 4-wire                                   | 29 |

| 2.19 | (a) Neutral current controller for a 3-phase 4-wire FEC                                                                                 | 29 |

| 2.20 | (a)Line and neutral current distortions with SPWM(b)Differential mode ripple equivalent circuit(c)Common mode ripple equivalent circuit | 30 |

| 2.21 | 3-phase 4-wire FEC with additional inductance $(L_{cn})$ in the neutral wire                                                            | 32 |

| 3.1  | Inverter and control hardware                                                                                                           | 40 |

| 3.2  | The DSP board which is developed in the lab                                                                                                     | 40 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3  | Pre-charge Circuit (left) and PD card(right)                                                                                                    | 41 |

| 3.4  | Line side inductors (left) and Common mode inductor<br>(right) $\ .$ .                                                                          | 41 |

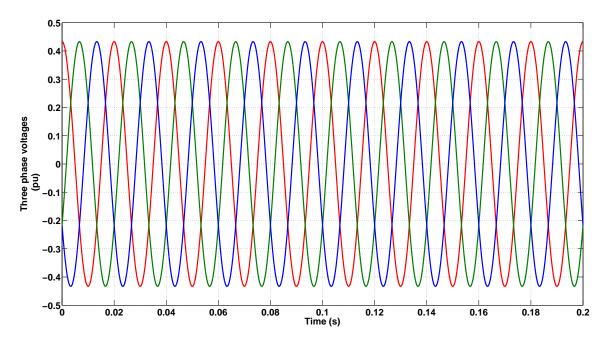

| 4.1  | Simulation result: $a, b$ and $c$ -phase voltages $\ldots \ldots \ldots$                                                                        | 44 |

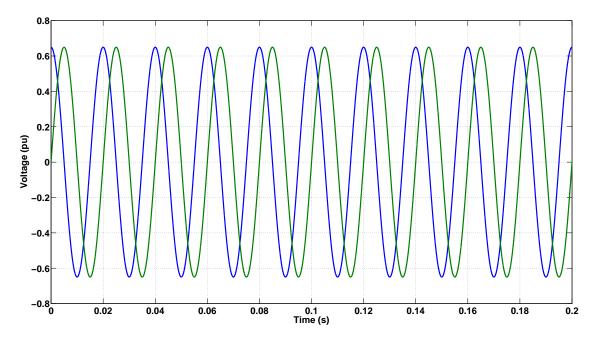

| 4.2  | Simulation result: $V_{s\alpha}$ and $V_{s\beta}$                                                                                               | 45 |

| 4.3  | Simulation result: $V_{s\alpha}$ and $V_{s\beta}$ after passing through first low pass filter                                                   | 46 |

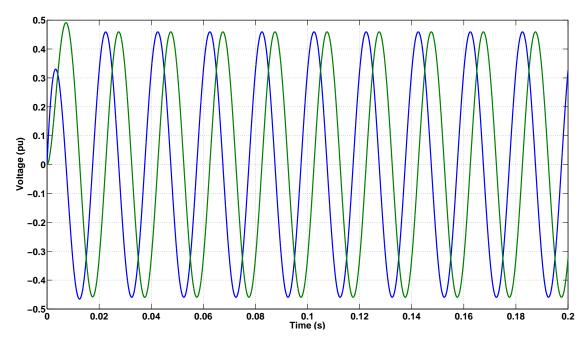

| 4.4  | Simulation result: $V_{s\alpha}$ and $V_{s\beta}$ after passing through second low pass filter                                                  | 46 |

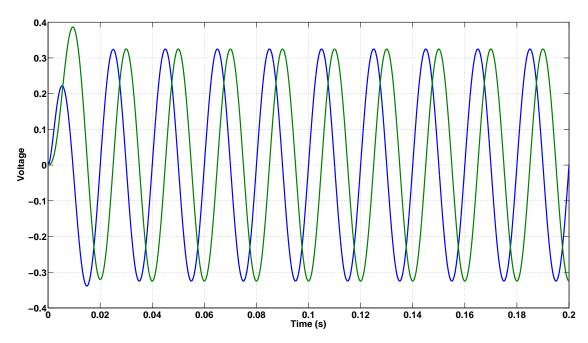

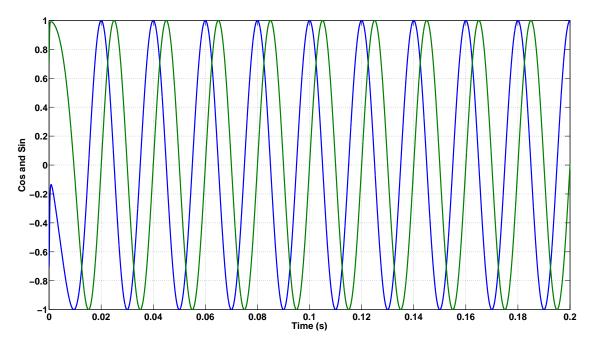

| 4.5  | Simulation result: $Cos\theta$ and $Sin\theta$                                                                                                  | 47 |

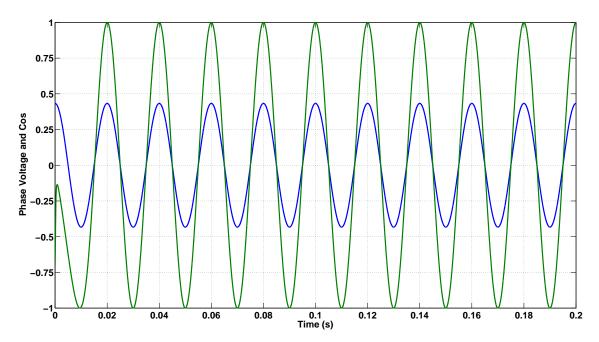

| 4.6  | Simulation result: $Cos\theta$ and $V_{sr}$                                                                                                     | 47 |

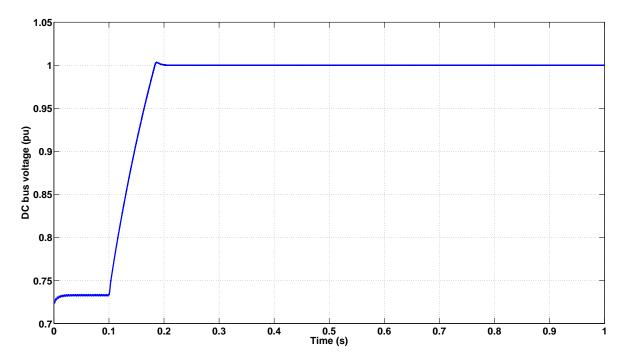

| 4.7  | Simulation result: DC bus charging from the initial pre-charged value to the reference voltage                                                  | 48 |

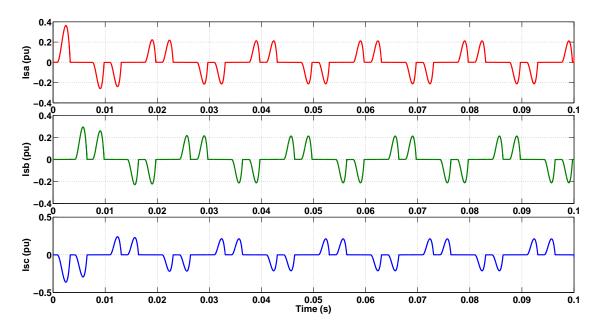

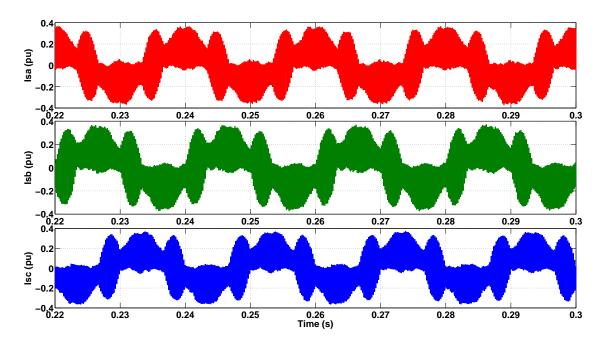

| 4.8  | Simulation result: Three phase line currents $I_{sa}$ , $I_{sb}$ and $I_{sc}$ through diode bridge rectifier                                    | 49 |

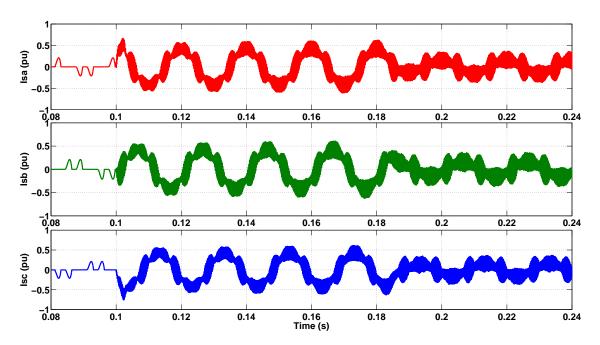

| 4.9  | Simulation result: Three phase line currents $I_{sa}$ , $I_{sb}$ and $I_{sc}$ at the starting of 3-phase 3-wire FEC                             | 49 |

| 4.10 | Simulation result: Three phase line currents $I_{sa}$ , $I_{sb}$ and $I_{sc}$ at the steady state of 3-phase 3-wire FEC                         | 50 |

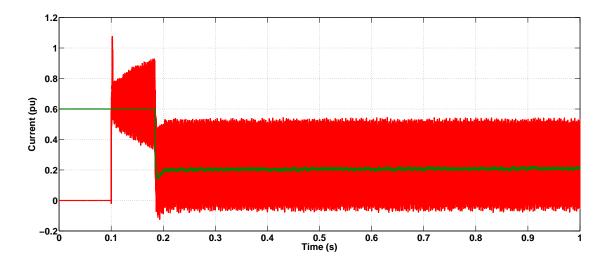

| 4.11 | Simulation result: $I_{sd}$ and $I_{sd}^*$ of a 3-phase 3-wire FEC                                                                              | 50 |

| 4.12 | textit<br>Simulation result: $I_{sq}$ and $I_{sq}^*$ of a 3-phase 3-wire FEC<br>                                                                | 51 |

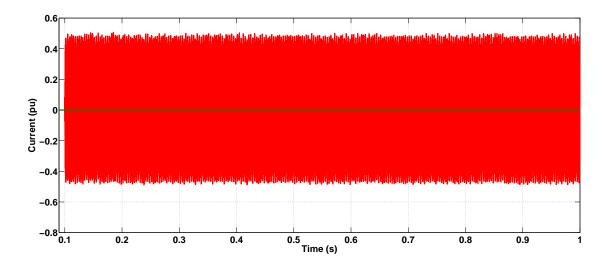

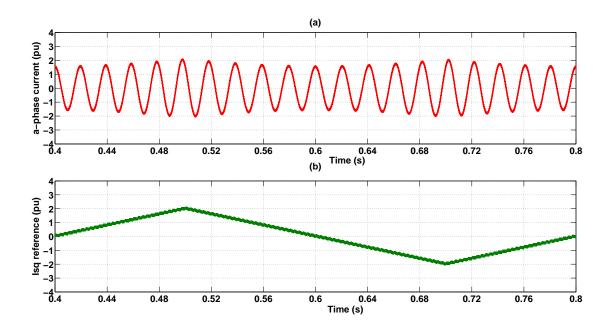

| 4.13 | Simulation result: The variation in line current $I_{sa}$ (a) with respect to change in $I_{sq}^*$ (b)                                          | 52 |

| 4.14 | Simulation result: Variation in $I_{sq}$ with respect to change in $I_{sq}^*$ of a 3-phase 3-wire FEC                                           | 52 |

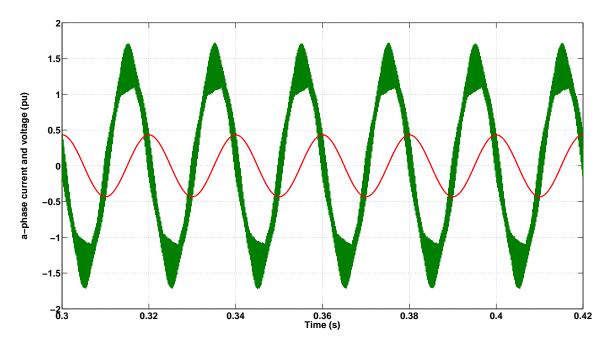

| 4.15 | Simulation result: Phase voltage $V_{sa}$ and line current $I_{sa}$ of a 3-phase 3-wire FEC at $10kW$ (full load) load                          | 53 |

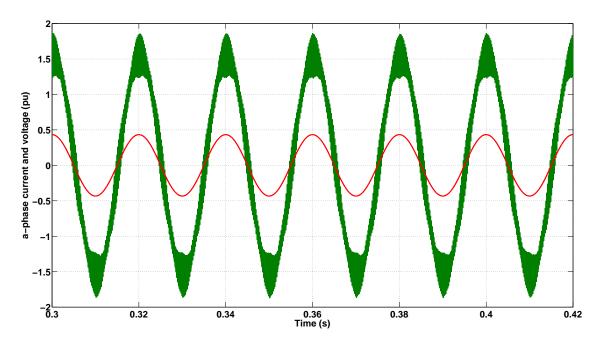

| 4.16 | Simulation result: Phase voltage $V_{sa}$ and line current $I_{sa}$ of a 3-phase 3-wire FEC at $I_{sq}^* = 2pu \dots \dots \dots \dots \dots$ . | 53 |

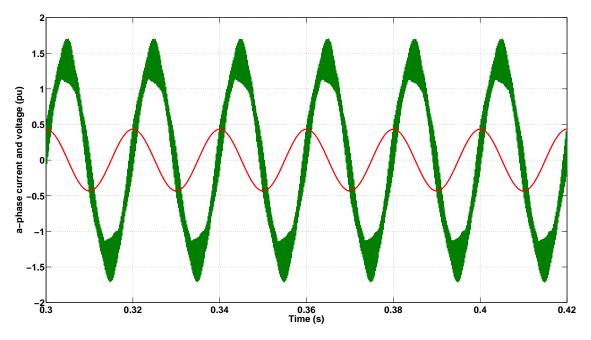

| 4.17 | Simulation result: Phase voltage $V_{sa}$ and line current $I_{sa}$ of a 3-phase 3-wire FEC at $I_{sq}^* = -2pu \dots \dots \dots \dots$        | 54 |

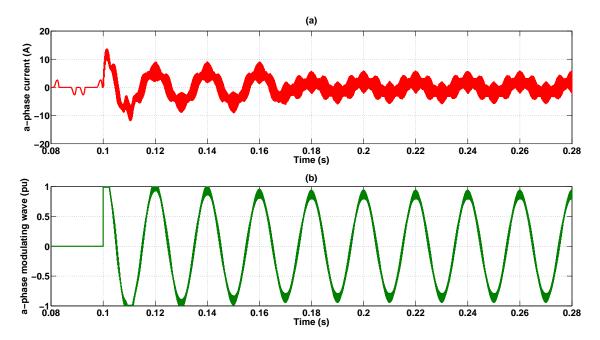

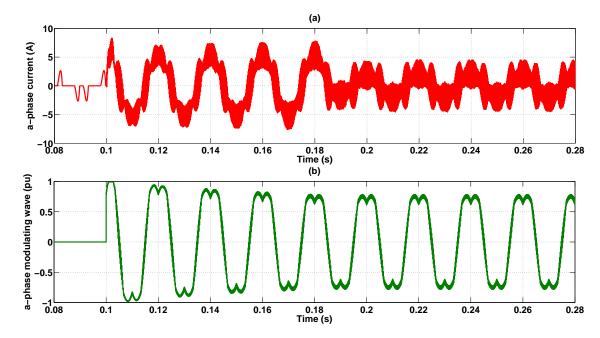

| 4.18 | Simulation result: Line current $I_{sa}$ and $a$ -phase modulating signal at the starting of a 3-phase 3-wire FEC using SPWM scheme             | 55 |

| 4.19 | Simulation result: Line current $I_{sa}$ and $a$ -phase modulating signal at the starting of a 3-phase 3-wire FEC using SVPWM scheme .          | 56 |

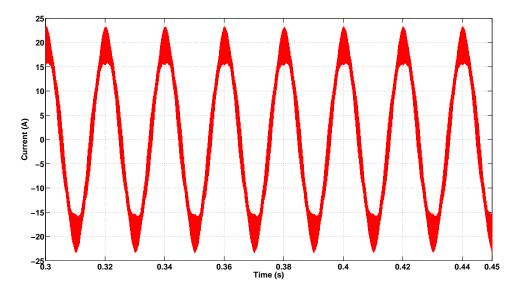

| 4.20 | Simulation result: The steady state line current $I_{sa}$                                                                                       | 57 |

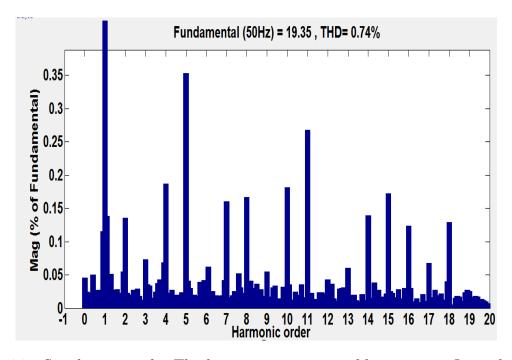

| 4.21 | Simulation result: The harmonic spectrum of line current $I_{sa}$ without eliminating harmonic components                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

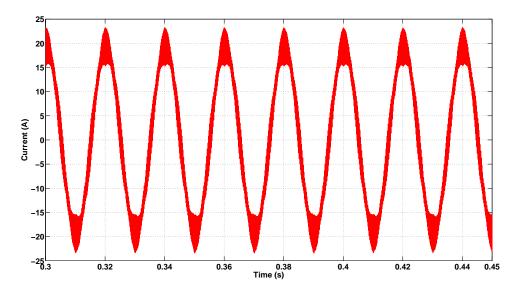

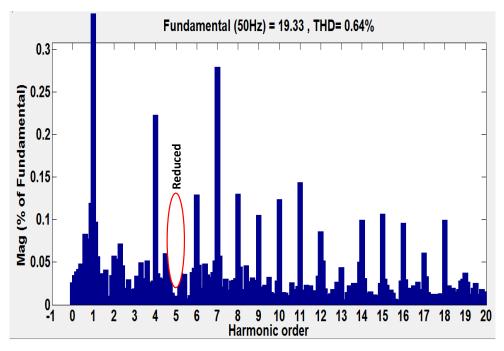

| 4.22 | Simulation result: The steady state line current $I_{sa}$ after eliminating $5th$ harmonic component                                                           |

| 4.23 | Simulation result: The harmonic spectrum of line current $I_{sa}$ after eliminating $5th$ harmonic component                                                   |

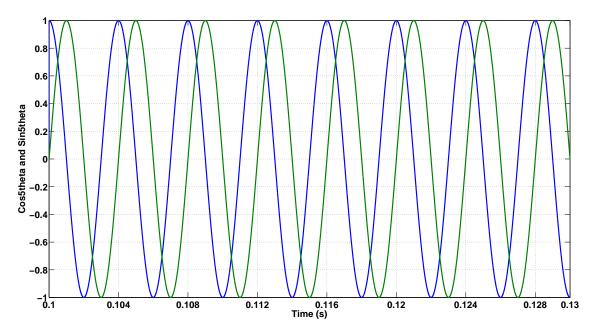

| 4.24 | Simulation result: $Cos5\theta$ and $Sin5\theta$                                                                                                               |

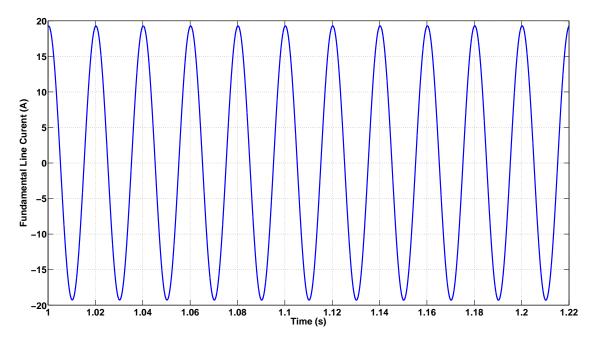

| 4.25 | Simulation result: Fundamental component of the line current $I_{sa}$                                                                                          |

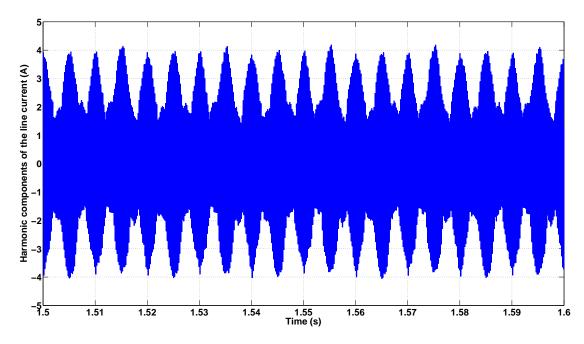

| 4.26 | Simulation result: Harmonic components of the line current $I_{sa}$                                                                                            |

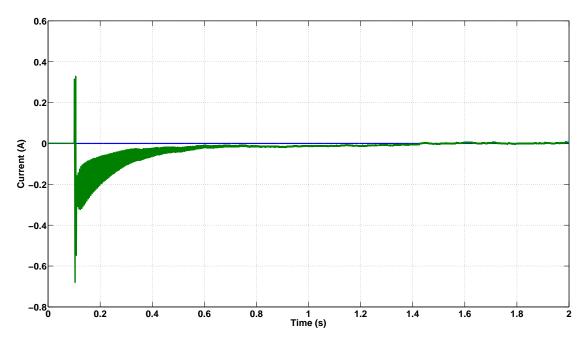

| 4.27 | Simulation result: $I_{sd_5}^*$ and $I_{sd_5}$                                                                                                                 |

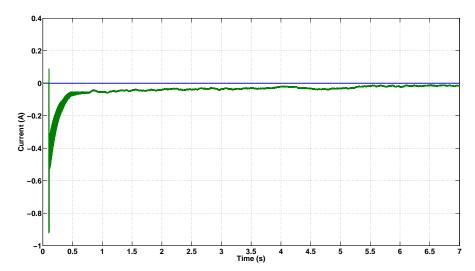

| 4.28 | Simulation result: $I_{sq_5}^*$ and $I_{sq_5}$                                                                                                                 |

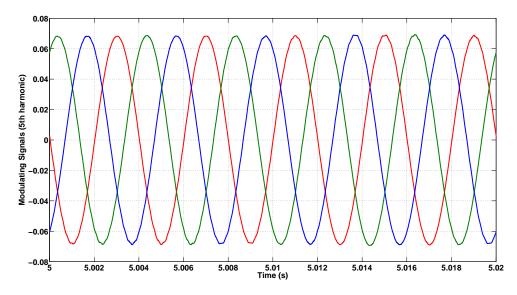

| 4.29 | Simulation result: Three phase reference modulating signals $V_{ina\_5}^*$ , $V_{inb\_5}^*$ , $V_{inc\_5}^*$ corresponding to $5th$ harmonic                   |

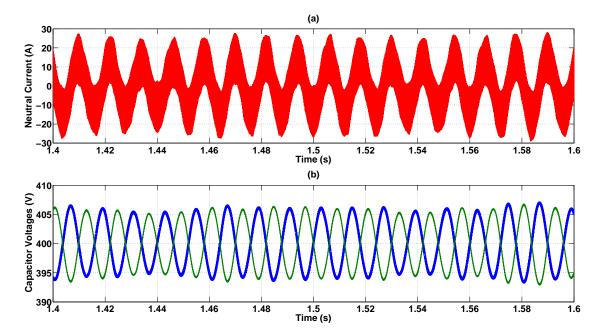

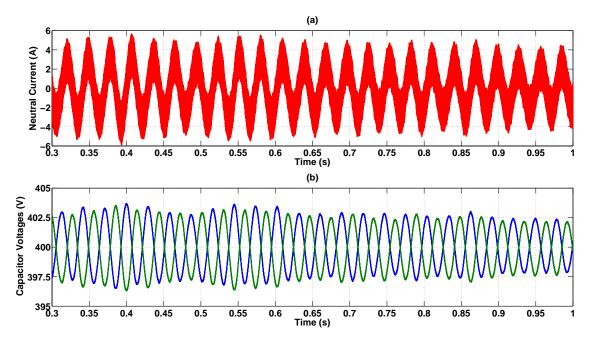

| 4.30 | Simulation result: (a)<br>Neutral current(b) Two DC capacitor voltages without the<br>$\mathcal{L}_c$ and without $\mathcal{I}_n$ controller using SPWM scheme |

| 4.31 | Simulation result: (a)<br>Neutral current(b) Two DC capacitor voltages without the<br>$L_c$ and with $I_n$ controller using SPWM scheme                        |

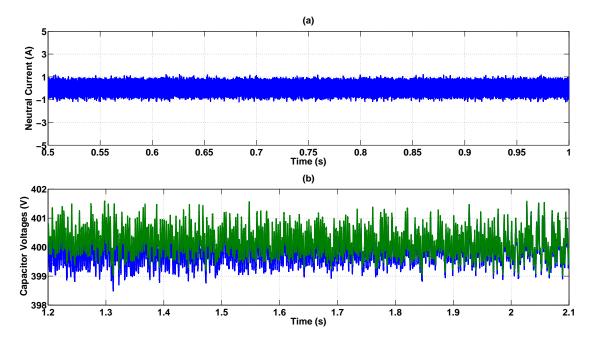

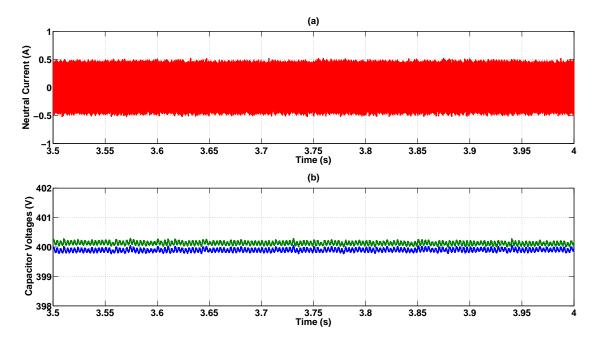

| 4.32 | Simulation result: (a)<br>Neutral current (b) Two DC capacitor voltages with the<br>$L_c$ and without $I_n$ controller using SPWM scheme                       |

| 4.33 | Simulation result: (a) Neutral current(b) Two DC capacitor voltages with the $L_c$ and with $I_n$ controller using SPWM scheme                                 |

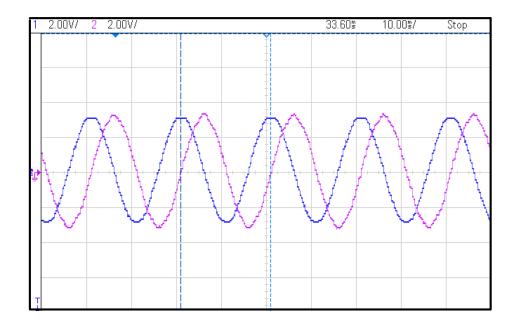

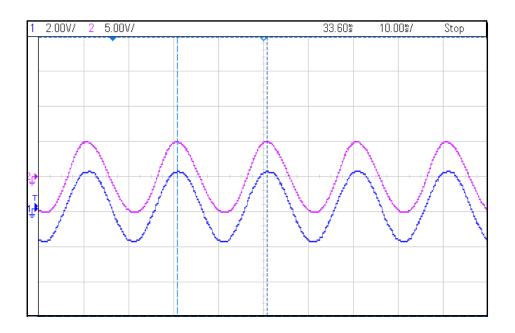

| 4.34 | Hardware result: $V_{s\alpha}$ and $V_{s\beta}$                                                                                                                |

| 4.35 | Hardware result: $V_{s\alpha}$ and $V_{s\beta}$ after passing through first low pass filter                                                                    |

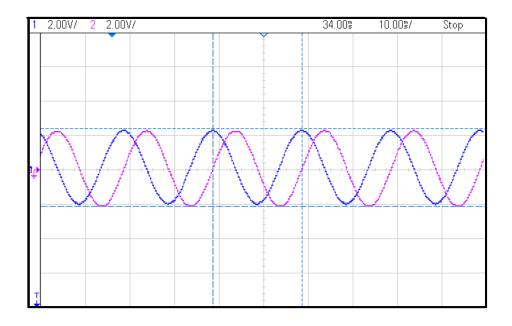

| 4.36 | Hardware result: $V_{s\alpha}$ and $V_{s\beta}$ after passing through second low pass filter                                                                   |

| 4.37 | Hardware result: $Cos\theta$ and $Sin\theta$                                                                                                                   |

| 4.38 | Hardware result: $V_{sa}$ and $Cos\theta$                                                                                                                      |

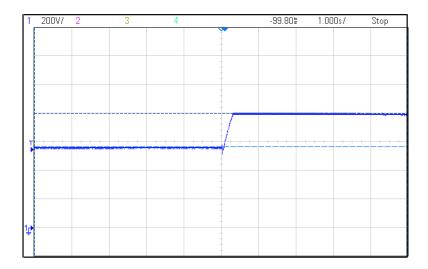

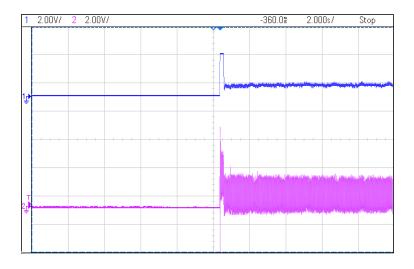

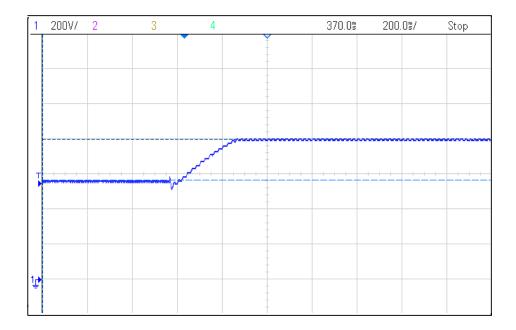

| 4.39 | Hardware result: DC bus voltage rising from the initial pre-charged value to $800V$                                                                            |

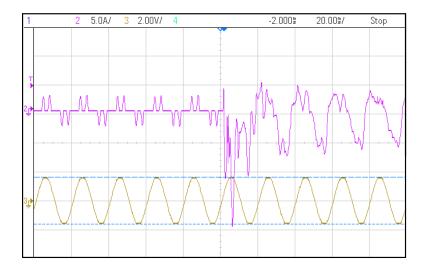

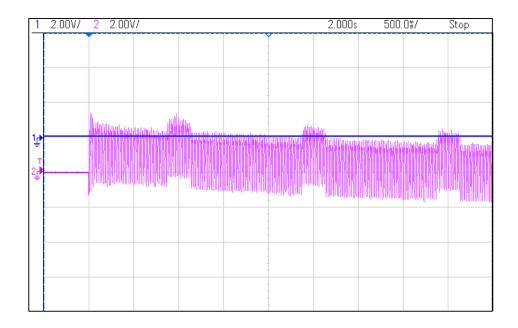

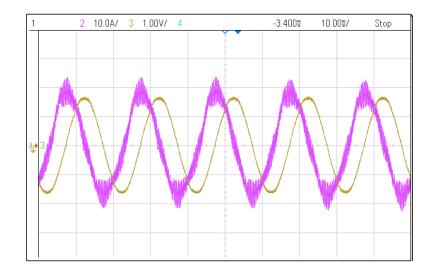

| 4.40 | Hardware result: Line current $I_{sa}$ and phase voltage $V_{sa}$ of a 3-phase 3-wire FEC at the starting                                                      |

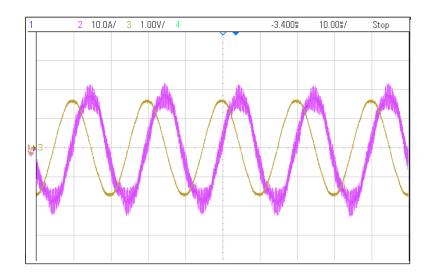

| 4.41 | Hardware result: Line current $I_{sa}$ and phase voltage $V_{sa}$ of a 3-phase 3-wire FEC at the steady state                                                  |

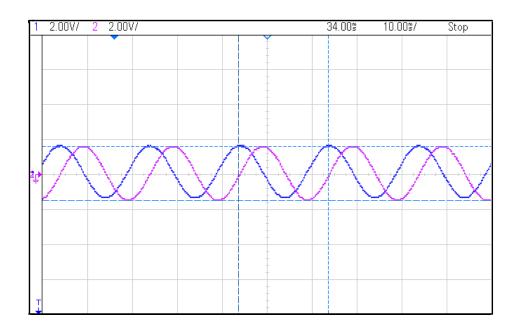

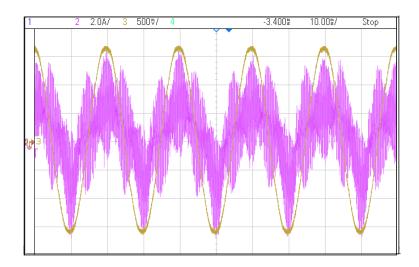

| 4.42 | Hardware result: $I_{sd}$ and $I_{sd}^*$ of a 3-phase 3-wire FEC                                                                                               |

| 4.43 | Hardware result: $I_{sq}$ and $I_{sq}^*$ of a 3-phase 3-wire FEC                                                                                               |

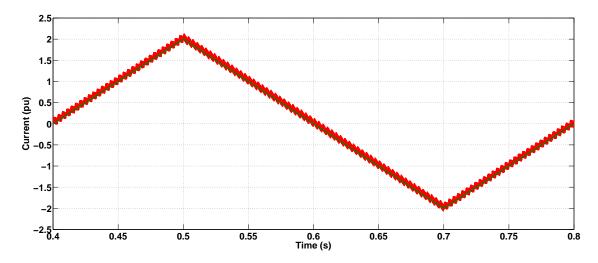

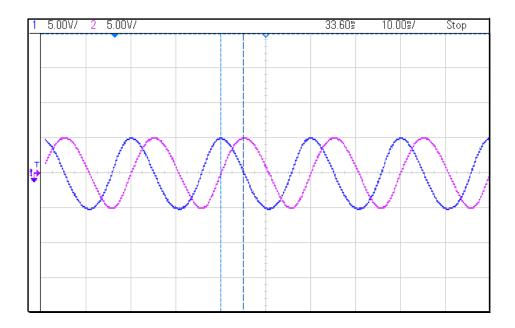

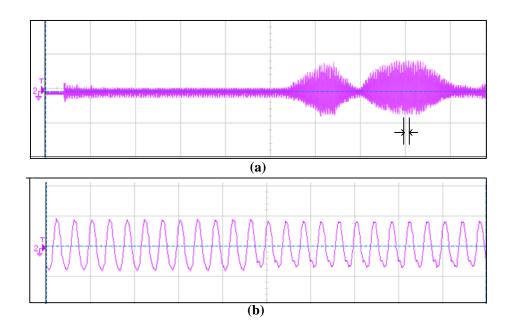

| 4.44 | Hardware result: Variation in $I_{sq}(\mathbf{a})$ with respect to change in $I_{sq}^*(\mathbf{b})$                                                            |

| 4.45 | $Hardware\ result$ : Variation in $I_{sq}$ with respect to change in $I_{sq}^*$ .                                                                         | 72 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.46 | Hardware result: Line current $I_{sa}$ and phase voltage $V_{sa}$ of a 3-phase 3-wire FEC at $I_{sq}^*=2pu$                                               | 73 |

| 4.47 | Hardware result: Line current $I_{sa}$ and phase voltage $V_{sa}$ of a 3-phase 3-wire FEC at $I_{sq}^* = -2pu$                                            | 73 |

| 4.48 | $Hardware\ result$ : DC bus voltage rising from the initial pre-charged value to $800V$                                                                   | 74 |

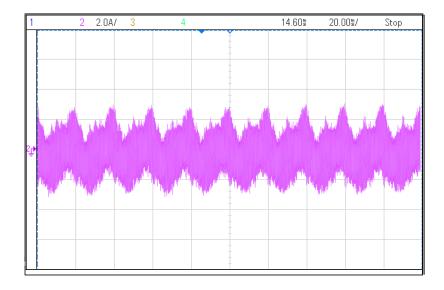

| 4.49 | Hardware result: Current through the neutral wire of a 3-phase diode bridge rectifier                                                                     | 75 |

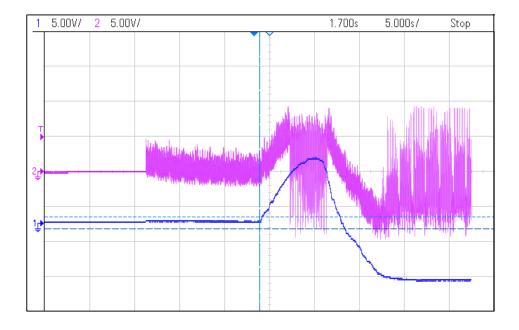

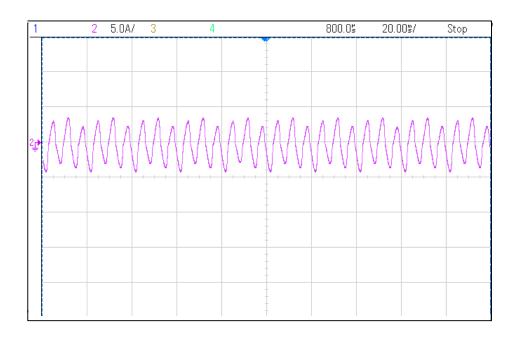

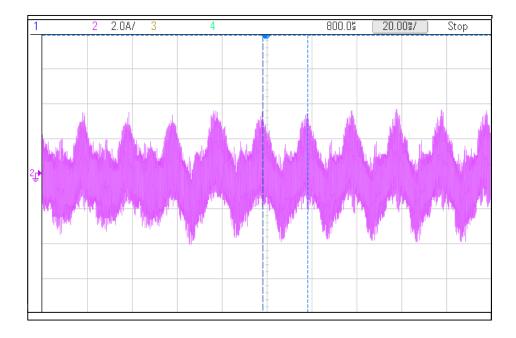

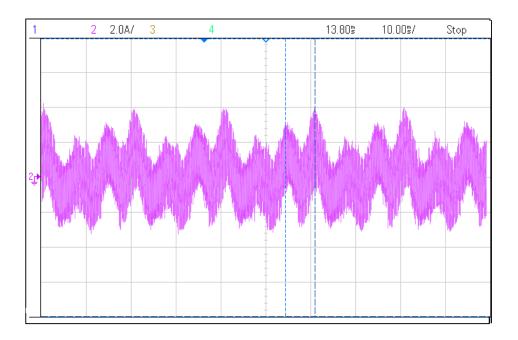

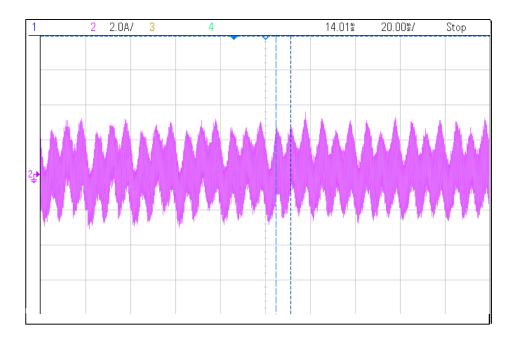

| 4.50 | Hardware result: Current through the neutral wire of a 3-phase 4-wire FEC without the neutral current controller using SPWM technique                     | 75 |

| 4.51 | Hardware result: Current through the neutral wire of a 3-phase 4-wire FEC with the neutral current controller using SPWM technique                        | 76 |

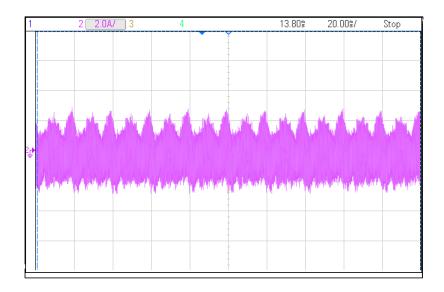

| 4.52 | Hardware result: Current through the neutral wire of a 3-phase 4-wire FEC without the neutral current controller using SVPWM technique $(V_{mid} = 0.01)$ | 77 |

| 4.53 | Hardware result: Current through the neutral wire of a 3-phase 4-wire FEC with the neutral current controller using SVPWM technique $(V_{mid} = 0.01)$    | 77 |

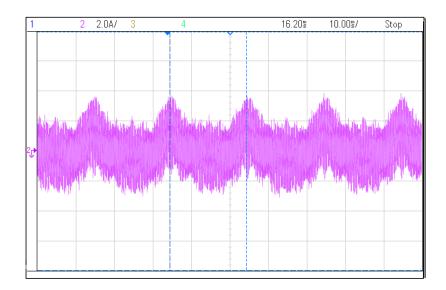

| 4.54 | Hardware result: Current through the neutral wire of a 3-phase 4-wire FEC without the neutral current controller using SVPWM technique $(V_{mid} = 0.1)$  | 78 |

| 4.55 | Hardware result: Current through the neutral wire of a 3-phase 4-wire FEC with the neutral current controller using SVPWM technique (V 0.1)               | 70 |

#### **ABBREVIATIONS**

**AFEC** Active Front End Converter

FEC Front End Converter

**AC** Alternating Current

**DC** Direct Current

VSI Voltage Source Inverter

FOC Field Oriented Control

PI Proportional and Integral

IGBT Insulated Gate Bipolar Transistor

**UPS** Uninterpretable Power Supply

**PWM** Pulse Width Modulation

PLL Phase Locked Loop

**KVL** Kirchhoff's voltage law

**SPWM** Sinusoidal Pulse Width Modulation

**SVPWM** Space Vector Pulse Width Modulation

**THD** Total Harmonic Distortion

CCS Code Composer Studio

ADC Analog to Digital Converter

$I^2C$  Inter Integrated Circuit

**CAN** Controller Area Network

JTAG Joint Test Action Group

**DMA** Direct Memory Access

PIE Peripheral Interrupt Expansion

**OTP** One Time Programmable

**SARAM** Single Access RAM

**ROM** Read Only Memory

PD Protection and Delay

# NOTATION

| $V_{sa}, V_{sb}, V_{sc}$    | Instantaneous grid voltages in $abc$ frame, $V$                         |

|-----------------------------|-------------------------------------------------------------------------|

| $V_m$                       | peak value of the grid voltage                                          |

| $V_{s\alpha}, V_{s\beta}$   | Instantaneous grid voltages in $\alpha\beta$ frame, $V$                 |

| $V_{sd}, V_{sq}, V_{s0}$    | Instantaneous grid voltages in $dq0$ frame, $V$                         |

| $I_{sa}, I_{sb}, I_{sc}$    | Instantaneous line currents in $abc$ frame, $A$                         |

| $I_{slpha},I_{seta}$        | Instantaneous line currents in $\alpha\beta$ frame, A                   |

| $I_{sd}, I_{sq}, I_{s0}$    | Instantaneous line currents in $dq\theta$ frame, A                      |

| $L_f$                       | Line side inductance, $mH$                                              |

| $L_c$                       | Common mode inductance, $mH$                                            |

| $R_f$                       | Coil resistance associated with the line side inductor, $\Omega$        |

| $C_{dc}$                    | DC bus capacitance , $\mu F$                                            |

| $R_d c$                     | Load resistance , $\Omega$                                              |

| $V_{ina}, V_{inb}, V_{inc}$ | Instantaneous pole voltages of the inverter in $abc$ frame, $V$         |

| $V_{inlpha}, V_{ineta}$     | Instantaneous pole voltages of the inverter in $\alpha\beta$ frame, $V$ |

| $V_{ind}, V_{inq}$          | Instantaneous pole voltages of the inverter in $dq$ frame, $V$          |

| $\omega$                    | Grid frequency, $rad/s$                                                 |

| heta                        | Instantaneous angle of $a$ -phase grid voltage, $rad$                   |

| $V_{dc}$                    | Instantaneous DC bus voltage, $V$                                       |

| $e_{ffd}, e_{ffq}$          | d and $q$ -axis feed forward terms, $V$                                 |

| $K_p$                       | Proportional gain of the PI controller                                  |

| $K_i$                       | Integral gain of the PI controller                                      |

| G                           | Gain of the inverter                                                    |

| $I_{sd\_n}, I_{sq\_n}$      | nth harmonic component in the line currents in $dq$ frame, $A$          |

| $I_n$                       | Instantaneous neutral current, A                                        |

|                             |                                                                         |

#### CHAPTER 1

#### INTRODUCTION

In the present scenario renewable energy has become major focus for the research. Among renewable sources Solar Power is efficient and environment friendly one. India has tremendous scope of generating solar energy. The geographical location of the country stands a benefit to this. Almost all parts of India receive 4-7 kWh of solar radiation per sq meters. To meet the surge demand of electricity, solar energy is the best form of energy needs of India and bridge the energy demand-supply gap.

In near future, solar energy must be used as the prime source of electricity. But one of the main challenge to supply solar power is its synchronization from all the distributed generation. Solar PV panels supplies power at different DC voltage levels. They are converted to 3-phase AC voltages and connected to the conventional 440 V grid. A 3-phase grid tied front end converter generally used for the DC to AC conversion. In this project both 10 kVA front end 3-phase 3-wire and 3-phase 4-wire grid tied inverter controller implemented and tested.

# 1.1 Back ground of the project

A Grid-Tied inverter is a power converter that converts DC current to AC current with an ability to synchronize with distribution Grid. Unlike in the transmission 3-phase 3-wire system, a 3-phase 4-wire system is necessary in the distribution side. A 3-phase 4-wire system requires additional controllers from a 3-phase 3-wire system. The inverter implemented in the laboratory has a 800 V DC bus and it is connected to a 440 V supply.

In the implemented system AC power from the grid will be converted to a DC voltage of 800 V, and this DC power will in turn fed into a resistance. The implemented converter is capable of bi-directional power flow. A two-level voltage

source inverter (VSI) is used as grid tied inverter. The implemented converter is essentially a current controlled voltage source. This type of converters are generally classified as Front End Converter (FEC), since these are connected to front/utility side of the supply. The implemented converter can also be used as a replacement for a diode bridge rectifier for a induction motor drive. In this way the regulation capability of the drive can be ensured with superior input current quality.

The ideal requirements of a FEC are as follows

- DC bus voltage control

- Sinusoidal input current with any given power factor

- Bi-directional power flow

- Good dynamic response

#### 1.1.1 Vector Control for FEC

The principle of Vector Control or Field Oriented Control (FOC) was originally developed by F. Blaschke and K. Hasse in Germany by the late 1960s for control of induction machine. The basic idea of this scheme is to control the flux producing and torque producing components of the induction motor in an independent manner. In induction machine the outer loop controls the speed of the motor, while the inner loop controls the current vector, which are producing torque and flux. Because of this fact the speed control of induction machine can be easily achieved[1]. Similar control technique can be adopted for power flow control of FEC [2; 3].

In this method, 3-phase grid voltages and line currents are converted into an equivalent 2-axes reference frame, which is stationary in nature. They are further converted into a synchronous reference frame, which rotates with grid (synchronous) frequency. In synchronous reference frame, the components of current corresponding to active and reactive power are controlled in an independent (orthogonal coordinates) manner similar to the torque and flux producing components in a motor drive. It is important to note that in synchronous reference

frame voltage and current become DC quantity. Therefore it is easy to implement these controllers using conventional PI controllers.

Though the technique of vector control was developed at late 1960's, it could not be readily realized in practice as the method is computationally intensive. However, with the advancement in the digital processors, today implementation of vector control algorithm is simple.

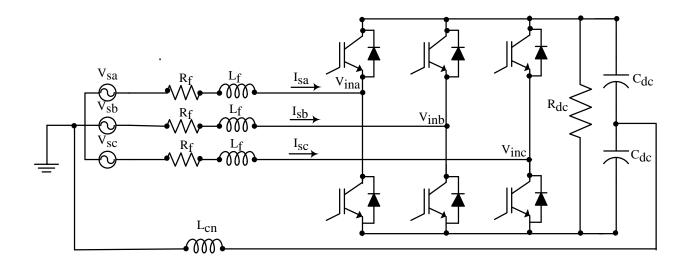

#### 1.2 Power Structure of the System

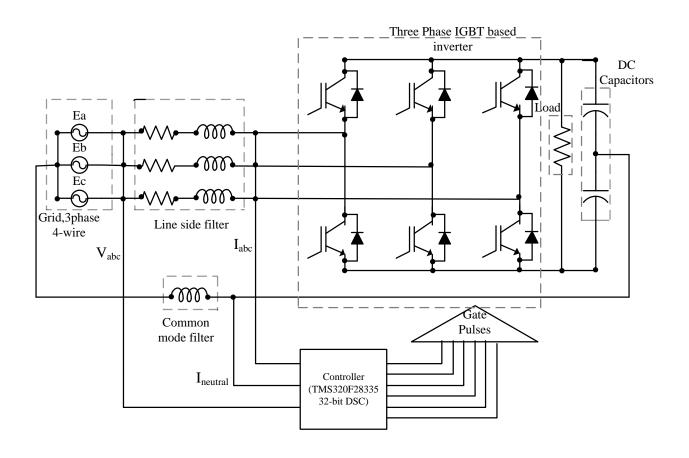

Fig. 1.1 Power structure of the system

The power structure of FEC consists of, a 3-phase 4-wire grid-tied inverter through line inductance, common mode filter, resistive load across DC bus and Digital Signal Controller(DSC). The power structure of FEC used is shown in Fig. 1.1. The controller is an indigenously developed 32-bit floating point Digital Signal Controller(DSC).

### 1.3 Goals of the Project Work

In this project two FEC configurations are implemented in a 10 kVA setup. The two configurations are 3-phase 3-wire and 3-phase 4-wire system. In applications where neutral wire connection to the inverter is of mandatory, there 3-phase 4-wire system is used. In general for motor drive applications, 3-phase 3-wire systems are used. In applications like battery charger, UPS and grid tied inverter 3-phase 4-wire inverter connection is mandatory [4; 5; 6]. For a 3-phase 4-wire system, the control techniques needs few modifications from the 3-phase 3-wire system.

# 1.3.1 Vector control of 3-phase 3-wire FEC and 3-phase 4-wire FEC

Achievements with the 3-phase 3-wire FEC and 3-phase 4-wire FEC, in this project are listed below.

**Vector control:** In synchronous reference frame independent control of both active and reactive power control is possible. Since in the synchronous reference frame all the quantities are DC, a simple PI controller will make steady state error zero.

**Soft start-up:** Soft start-up algorithm helps the output voltage build gradually, keeping the starting current low.

**DC** bus voltage regulation: DC bus will remain same voltage as reference voltage within the prescribed load.

**Operation at desired power factor:** Achieved both lagging and leading power factor operation of FEC.

**Different PWM techniques:** Both sinusoidal and space vector modulation schemes has been experimented.

Elimination of lower order harmonic components from the line current: Effective elimination of 5th and 7th harmonic components of line current without increasing bandwidth of the controllers has been done.

Elimination of zero sequence current: Eliminated zero sequence current, that is current that flowing through the neutral wire in a 3-phase 4-wire FEC with the help of a neutral current controller.

**Neutral current distortions:** Analyzed the effect on neutral current distortions with sinusoidal and space vector modulation schemes in a 3-phase 4-wire FEC.

### 1.4 Organisation of Thesis

Chapter 2 presents a detailed description on the theory of space phasors, detailed modeling and analysis of 3-phase 3-wire Front End converter and 3-phase 4-wire FEC with different modulation techniques. The chapter also describes the control strategy for the FEC and techniques for elimination of harmonics from the line current. Front End Converter (FEC) is presented along with the relevant equations.

Chapter 3 deals with the hardware organization for the implementation of FEC on a 10 kVA laboratory prototype. Some of the basic capabilities and features of the control platform, which is indigenously developed in the laboratory based on the TMS320F28335 Digital Signal Controller (DSC), from Texas Instruments, that are used in the control implementation. And the protection and delay card that acts as the interface between the controller and the inverter is discussed. It also describes the digital implementation FEC control system using per unitisation technique. The design of current controllers and voltage controllers used in the vector control scheme are presented.

**Chapter 4** Discusses the results obtained from the simulation for the 10 kVA FEC (both 3-wire and 4-wire) as well as that from the actual hardware implementation on the 10 kVA FEC (both 3-wire and 4-wire).

Chapter 5 Presents the summary of the work done and the future scope for improving the work.

#### CHAPTER 2

# Modeling, Analysis and Control of 3-phase 3-wire and 3-phase 4-wire Front End Converter

#### 2.1 Introduction

In this chapter modeling and control technique for a 3-phase 3-wire and a 3-phase 4-wire front end converter (FEC) are discussed. The three phase voltages and line currents of a FEC are analyzed with complex space vectors and control techniques adopted for the FEC are implemented in a synchronous reference frame. Proposed control uses coordinate transformations which transforms voltages and currents of a three phase stationary system to a revolving two coordinate time invariant system which rotates at the grid frequency and synchronized with a-phase grid voltage.

Relevant equations for control are derived in rotating reference frame and the basic scheme for the control is presented. Deign methodology of a simple phase locked loop (PLL) adopted to determine the rotating voltage reference frame is discussed. Elimination of lower order harmonics (5th and 7th) from the line current of the FEC also described in this chapter.

#### 2.2 Vector Control of FEC

The concept of vector control for a 3-phase 3-wire FEC is described in following section.

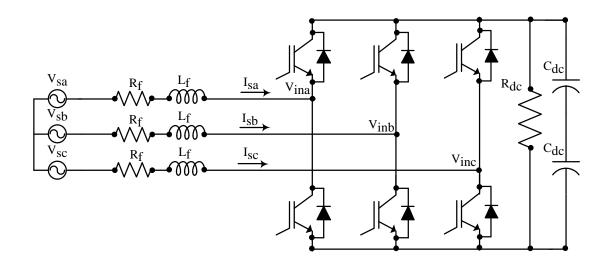

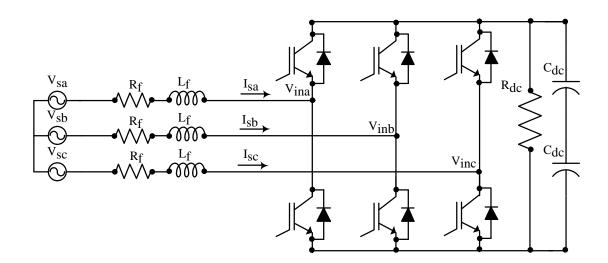

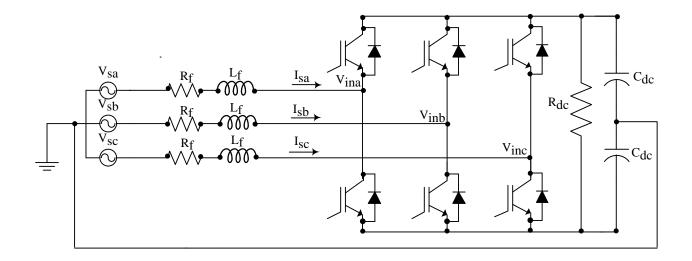

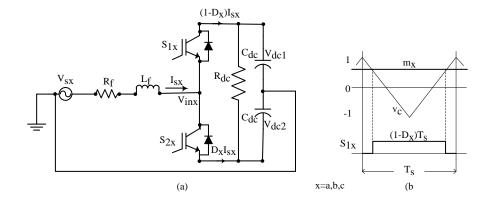

Figure 2.1, shows power architecture of a 3-phase 3-wire PWM rectifier which have a IGBT based two-level VSI, necessary filter inductor and DC bus capacitor. DC bus of the rectifier is formed by two identical series connected capacitors.

Fig. 2.1 3-phase 3-wire FEC

The three phase balanced grid voltages are given below

$$Vsa(t) = VmCos(wt) (2.1)$$

$$Vsb(t) = VmCos(wt - 2\pi/3)$$

(2.2)

$$Vsc(t) = VmCos(wt + 2\pi/3)$$

(2.3)

Where  $V_{sa}$ ,  $V_{sb}$  and  $V_{sc}$  are three phase voltages. Transforming equations (2.1)-(2.3) into  $\alpha$ - $\beta$  (stationary) reference frame [7].

$$\vec{V}_{3-\phi} = [V_{sa}(t) + V_{sb}(t)e^{j(2\pi/3)} + V_{sc}(t)e^{j(4\pi/3)}]$$

(2.4)

$$= V_{s\alpha} + jV_{s\beta} \tag{2.5}$$

where

$$V_{s\alpha} = V_{sa}(t) - \frac{1}{2}V_{sb}(t) - \frac{1}{2}V_{sc}(t)$$

(2.6)

$$= \frac{3}{2}V_m Cos(wt) \tag{2.7}$$

$$V_{s\beta} = \frac{\sqrt{3}}{2} [V_{sb}(t) - V_{sc}(t)]$$

(2.8)

$$= \frac{3}{2}V_m Sin(wt) \tag{2.9}$$

Thus the grid voltage can be written in space vector format as given in Eq.(2.12).

$$\vec{V}_s = V_{s\alpha} + jV_{s\beta} \tag{2.10}$$

$$= V_{s\alpha} + jV_{s\beta}$$

$$= \frac{3}{2}V_m[Cos(wt) + jSin(wt)]$$

$$= \frac{3}{2}V_me^{jwt}$$

(2.10)

$$(2.11)$$

$$= \frac{3}{2}V_m e^{jwt} \tag{2.12}$$

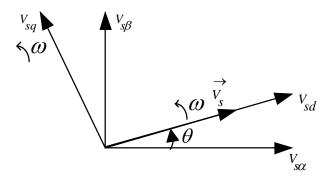

The Eq.(2.12) explains that, the voltage space vector  $(\vec{V}_s)$  has a magnitude of  $\frac{3}{2}V_m$  and it rotates with an angular speed of w with respect to a stationary reference frame in the anti-clockwise direction. Hence space vector  $(\vec{V}_s)$  makes an angle  $wt = \theta$  at any given instant of time with respect to the  $\alpha$ -axis. Therefore, it is able to choose a synchronous d-q reference frame which rotates with an angular speed of w in the anti-clockwise direction and making an angle  $wt = \theta$  at any given instant of time with respect to the  $\alpha$ -axis as shown in the figure 2.2. Here the synchronous reference frame is selected in such a way that grid voltage space vector  $(\vec{V}_s)$  is aligned along d-axis so that its component along q-axis is zero. Since grid voltage space vector  $(\vec{V}_s)$  and d-q axis rotating at same speed w as shown in figure 2.2, then these are seemed to be stationary with respect to each other thus grid voltage space vector appeared as DC quantity in d-q reference frame.

Fig. 2.2  $\alpha$ - $\beta$  and d-q frames phasor representation

From the figure 2.2 derivation of the equation for  $\vec{V}_s$  in d-q reference frame is

given below

$$V_{sd} = V_{s\alpha}Cos\theta + V_{s\beta}Sin\theta \tag{2.13}$$

$$V_{sq} = V_{s\beta}Cos\theta - V_{s\alpha}Sin\theta \tag{2.14}$$

## 2.3 Ideal Operation of Front End Converter

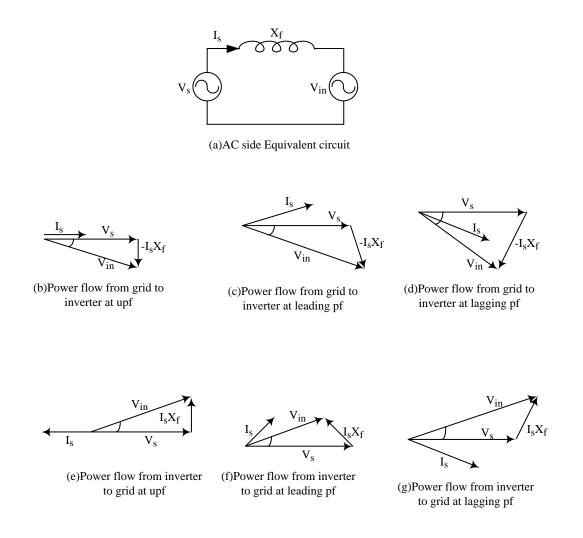

The possible modes of operations of a FEC are shown using phasor diagrams in figure 2.3.

In the figure 2.3,  $V_s$  indicates grid voltage and  $V_{in}$  indicates per phase inverter

Fig. 2.3 Equivalent circuit and phasor diagrams of the FEC

output voltage. It is known that active power flows from leading voltage to lagging voltage, and reactive power flows from higher magnitude of voltage to lower mag-

nitude of voltage. Therefore in FEC control, phase and magnitude of the inverter voltage is adjusted in such a way that desired reactive and real power flows into the inverter from the grid. If unity power factor current of magnitude  $I_s$  is desired to be drawn from the grid, then the inverter voltage can be obtained by vectorially adding grid voltage  $(V_s)$  and negating the reactive drop  $(I_sX_f)$  as shown in figure 2.3(b). In the similar way vector diagram for real power flow and reactive power flow at different possible operating conditions are shown in figures 2.3(b)-2.3(g).

# 2.4 Modeling of 3-phase 3-wire Front End Converter

In this section modeling of a 3-phase 3-wire FEC is discussed. As mentioned earlier, the modeling and controller design has carried out in the rotating d-q reference frame. The rotating reference frame is obtained from the grid voltage.

Fig. 2.4 3-phase 3-wire FEC circuit diagram

3-phase balanced grid voltages for the 3-phase 3-wire FEC are given below.

$$Vsa(t) = VmCos(wt) (2.15)$$

$$Vsb(t) = VmCos(wt - 2\pi/3) \tag{2.16}$$

$$Vsc(t) = VmCos(wt + 2\pi/3)$$

(2.17)

Applying KVL to circuit 2.4, voltage equations for 3-phase 3-wire FEC can be obtained as given below.

$$Vsa = R_f I_{sa} + L_f \frac{dI_{sa}(t)}{dt} + V_{ina}$$

(2.18)

$$Vsb = R_f I_{sb} + L_f \frac{dI_{sb}(t)}{dt} + V_{inb}$$

(2.19)

$$Vsc = R_f I_{sc} + L_f \frac{dI_{sc}(t)}{dt} + V_{inc}$$

(2.20)

Eq.(2.21) can be obtained by transforming the equations (2.18), (2.19) and (2.20) into the  $\alpha$ - $\beta$  reference frame.

$$\vec{V}_s^{\alpha-\beta} = R_f \vec{I}_s^{\alpha-\beta} + L_f \frac{d\vec{I}_s^{\alpha-\beta}(t)}{dt} + \vec{V}_{in}^{\alpha-\beta}$$

(2.21)

In Eq.(2.21),  $\vec{V}_s^{\alpha-\beta}$  is the grid voltage space vector in  $\alpha$ - $\beta$  reference frame,  $\vec{I}_s^{\alpha-\beta}$  is the line current space vector in  $\alpha$ - $\beta$  reference frame and  $\vec{V}_{in}^{\alpha-\beta}$  is the inverter pole voltage in  $\alpha$ - $\beta$  reference frame.

$\vec{V}_s^{d-q}$  is the grid voltage space phasor observed from rotating (d-q) reference frame. Therefore Eq.(2.21) can be rewritten as

$$\vec{V}_s^{d-q}(t)e^{j\theta} = R_f \vec{I}_s^{d-q} e^{j\theta} + L_f \frac{d(\vec{I}_s^{d-q}(t)e^{j\theta})}{dt} + \vec{V}_{in}^{d-q} e^{j\theta}$$

(2.22)

$$(V_{sd} + jV_{sq})e^{j\theta} = R_f(I_{sd} + jI_{sq})e^{j\theta} + L_f \frac{d(I_{sd} + jI_{sq})e^{j\theta}}{dt} + (V_{ind} + V_{inq})e^{j\theta}$$

(2.23)

where

$$L_f \frac{d(I_{sd}+jI_{sq})e^{j\theta}}{dt} = L_f \frac{dI_{sd}}{dt}e^{j\theta} + j\omega L_f I_{sd}e^{j\theta} + jL_f \frac{dI_{sq}}{dt}e^{j\theta} - \omega L_f I_{sq}e^{j\theta}$$

(2.24)

It is important to note that equations (2.22) and (2.23) are still in the  $\alpha$ - $\beta$  reference frame.

Substituting equation Eq.(2.24) in equation Eq.(2.23), FEC equation in d-q reference frame can be obtained after multiplying Eq.(2.23) with  $e^{-j\theta}$ . The d-axis and q-axis components of FEC voltage equation in d-q reference frame can be obtained by multiplying Eq.(2.23) with  $e^{-j\theta}$  and equating real and imaginary parts

as follows

$$V_{sd} = R_f I_{sd} + L_f \frac{dI_{sd}}{dt} - \omega L_f I_{sq} + V_{ind}$$

(2.25)

$$V_{sq} = R_f I_{sq} + L_f \frac{dI_{sq}}{dt} + \omega L_f I_{sd} + V_{inq}$$

(2.26)

Eq. (2.25) and Eq. (2.26) together explain the front end converter equation in d-q reference frame. Eq. (2.25) and Eq. (2.26) can be rewrite as given in Eq. (2.27) and Eq. (2.28) (since,  $V_{sq} = 0$ ).

$$V_{ind} = -R_f I_{sd} - L_f \frac{dI_{sd}}{dt} + e_{ffd}$$

(2.27)

$$V_{inq} = -R_f I_{sq} - L_f \frac{dI_{sq}}{dt} + e_{ffq}$$

(2.28)

Where,  $e_{ffd} = -V_{sd} - \omega L_f I_{sq}$  and  $e_{ffq} = \omega L_f I_{sd}$  are the *d*-axis and *q*-axis feed forward terms respectively.

### 2.5 Control Strategy for FEC

As mentioned earlier, control of the FEC has been done in synchronous (d-q) reference frame. The objectives of the FEC control are as follows.

- Maintaining DC bus voltage at a fixed reference value

- Control of real power flow from the grid

- Control of reactive power flow from the grid

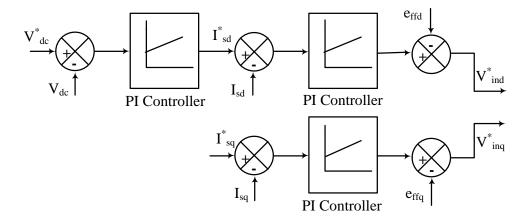

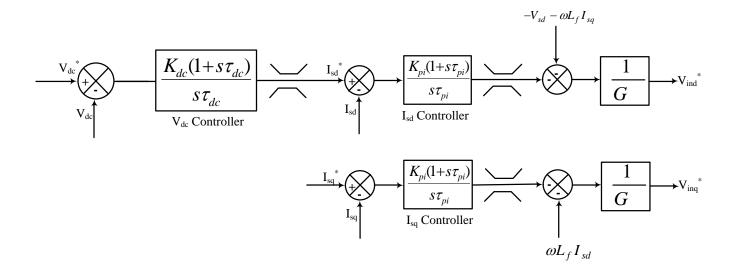

All the above criteria for the control can be achieved through conventional vector control techniques [8]. All the above vector controller loops are shown in figure 2.5. In figure 2.5,  $V_{dc}$  and  $V_{dc}^*$  are the actual and reference DC bus voltage respectively,  $I_{sd}$  and  $I_{sq}$  are the d and q-axis component of the line current vector in the d-q reference frame,  $I_{sd}^*$  and  $I_{sq}^*$  are the reference for d and q-axis component of the line current vector in the d-q reference frame,  $e_{ffd}$  and  $e_{ffq}$  are the feed forward terms in the d and q-axis respectively and  $V_{ind}^*$  and  $V_{inq}^*$  are the reference pole voltage of the inverter in the d-q reference frame.

Fig. 2.5 Vector Controller Loops

The DC bus voltage regulation is possible through a PI controller, which takes the difference between actual DC bus voltage and reference DC value as the input. The output of the DC bus voltage controller will be the reference for  $I_{sd}$  controller.  $I_{sd}$  controller controls the real power flow from the grid, since  $I_{sd}$  is a measure of real power (P) as shown in Eq.(2.29). The reactive power flow control from the grid is possible through by controlling  $I_{sq}$ , since  $I_{sq}$  is a measure of reactive power (Q) as shown in Eq.(2.30). Feed forward terms  $e_{ffd}$  and  $e_{ffq}$  are added at the output of  $I_{sd}$  and  $I_{sq}$  controller respectively, in order to get the  $V_{ind}^*$  and  $V_{inq}^*$ .  $V_{ind}^*$ and  $V_{inq}^*$  will then used for the PWM generation.

$$P = \frac{2}{3}[V_{sd}I_{sd} + V_{sq}I_{sq}] = \frac{2}{3}V_{sd}I_{sd}$$

$$Q = \frac{2}{3}[V_{sq}I_{sd} - V_{sd}I_{sq}] = -\frac{2}{3}V_{sd}I_{sq}$$

(2.29)

$$Q = \frac{2}{3}[V_{sq}I_{sd} - V_{sd}I_{sq}] = -\frac{2}{3}V_{sd}I_{sq}$$

(2.30)

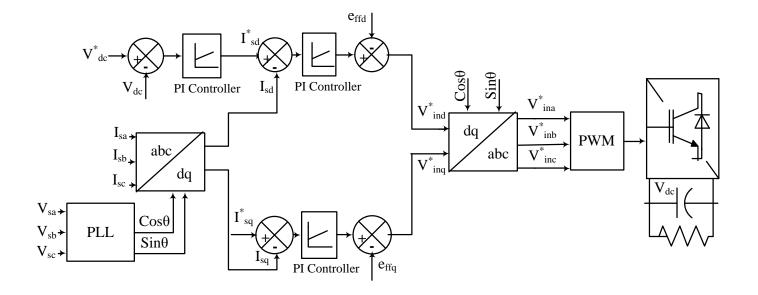

The overall block diagram of a vector controlled 3-phase 3-wire FEC in dq reference frame is shown in figure 2.6. The grid voltages and line currents are transformed into d-q reference frame from the stationary reference frame, and are used as feedback variables for the controller. The control calculations are performed in the d-q reference frame.

The vector controller has an outer DC voltage controller loop and two inner

Fig. 2.6 Control structure of FEC in d-q reference frame

current controller loops.  $V_{ind}^*$  and  $V_{inq}^*$ , which are obtained after adding feed forward terms to the inner controller loops are transformed into stationary reference frame as  $V_{ina}^*$ ,  $V_{inb}^*$  and  $V_{inc}^*$ .  $V_{ina}^*$ ,  $V_{inb}^*$  and  $V_{inc}^*$  are the three phase modulating voltages in the stationary reference frame, which are used to generate PWM pulses. The generated pulses will go to the IGBT gate driver and required pole voltages will be generated at the inverter terminals.

The transformations from the stationary to d-q reference frame and d-q to stationary reference frame requires information about  $Cos\theta$  and  $Sin\theta$ , where  $\theta$  is angle made by d-axis with  $\alpha$ -axis at any instant of time. The information about  $Cos\theta$  and  $Sin\theta$  can be obtained from a Phase Locked Loop (PLL). The structure of a PLL is explained in the following section.

The details about PI controller design, feed-forward terms and PWM generation are also explained in the subsequent sections.

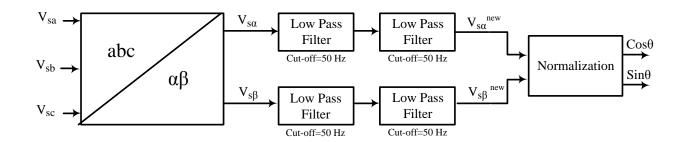

### 2.5.1 Phase Locked Loop (PLL)

PLL plays a major role in the controller part as it will give position information of the utility grid voltage at any instant of time. These  $Cos\theta$  and  $Sin\theta$  will be used in the transformations of voltage and current between stationary reference

frame and synchronous reference frame [9]. The block diagram of PLL which is used in the project is shown in figure 2.7. The three phase balanced grid voltages

Fig. 2.7 PLL Block Diagram

are transformed into  $\alpha$ - $\beta$  reference frame. After that it will pas through two low pass filters of cut-off frequency equals to 50Hz. By normalizing the output with appropriate values,  $Sin\theta$  and  $Cos\theta$  can be generated.

The three phase balanced grid voltages are given below, here the assumption is that grid frequency  $w=2\pi*50 rad/s$  is a constant.

$$Vsa(t) = VmCos(wt)$$

$Vsb(t) = VmCos(wt - 2\pi/3)$

$Vsc(t) = VmCos(wt + 2\pi/3)$

3-phase to  $\alpha$ - $\beta$  transformations yield

$$V_{s\alpha} = V_{sa}(t) - \frac{1}{2}V_{sb}(t) - \frac{1}{2}V_{sc}(t)$$

$$= \frac{3}{2}V_{sa}(t)$$

$$= \frac{3}{2}V_{m}Cos(wt)$$

$$V_{s\beta} = \frac{\sqrt{3}}{2}[V_{sb}(t) - V_{sc}(t)]$$

$$= \frac{3}{2}V_{m}Cos(wt - \pi/2)$$

$$= \frac{3}{2}V_{m}Sin(wt)$$

(2.31)

Since each low pass filter will produce a gain of  $\frac{1}{\sqrt{2}}$  and a phase shift of  $\frac{-\pi}{4}$ , the output of two cascaded low pass filters with the corresponding inputs  $V_{s\alpha}$  and  $V_{s\beta}$ will be

$$[V_{s\alpha}^{new} + jV_{s\beta}^{new}] = \frac{1}{2}[V_{s\alpha} + jV_{s\beta}]e^{-j\pi/2}$$

$$V_{s\alpha}^{new} = \frac{1}{2} * \frac{3}{2} * V_m Cos(wt - \pi/2)$$

$$= \frac{1}{2} * \frac{3}{2} * V_m Sin(wt)$$

$$V_{s\beta}^{new} = \frac{1}{2} * \frac{3}{2} * V_m Sin(wt - \pi/2)$$

$$= [-1]\frac{1}{2} * \frac{3}{2} * V_m Cos(wt)$$

(2.33)

$$(2.34)$$

The normalization in order to get  $Sin\theta$  and  $Cos\theta$  is explained below

$$Cos\theta = \frac{-V_{s\beta}^{new}}{\sqrt{(V_{s\alpha}^{new})^2 + (V_{s\beta}^{new})^2}}$$

(2.36)

$$Cos\theta = \frac{-V_{s\beta}^{new}}{\sqrt{(V_{s\alpha}^{new})^2 + (V_{s\beta}^{new})^2}}$$

$$Sin\theta = \frac{V_{s\alpha}^{new}}{\sqrt{(V_{s\alpha}^{new})^2 + (V_{s\beta}^{new})^2}}$$

(2.36)

#### 2.5.2PI Controllers

Using the output of PLL, it is possible to convert grid voltages and line currents from a stationary reference frame to a synchronous reference frame, where all the quantities appeared as DC. Here, DC bus voltage controller will acts as outer loop controller and two current  $(I_{sd} \text{ and } I_{sq})$  controllers act as inner controller loops.

#### Real Power and Reactive Power Controller

In a FEC, real power control is possible by controlling the real part of current  $I_{sd}$ and reactive power control is done by controlling  $I_{sq}$ . The controller draws current from the grid based on the load requirement, while keeping the DC bus voltage at the reference. In the case of reactive power control, by varying  $I_{sq}^*$  variation in reactive power flow from the grid is possible. As mentioned in section 2.5, the output of the real power controller and reactive power controller will be  $V_{ind}^*$  and  $V_{inq}^*$  respectively, which is the reference for modulating signal.

By referring to equation Eq. (2.25) and Eq. (2.26), rearranging the terms and removing feed forward terms from the equations,

$$V_{ind}(t) = -R_f I_{sd}(t) - L_f \frac{dI_{sd}(t)}{dt}$$

(2.38)

$$V_{inq}(t) = -R_f I_{sq}(t) - L_f \frac{dI_{sq}(t)}{dt}$$

(2.39)

Converting Eqs. (2.38) and (2.39) into frequency domain

$$V_{ind} = -R_f I_{sd} - sL_f I_{sd} (2.40)$$

$$V_{inq} = -R_f I_{sq} - s L_f I_{sq} (2.41)$$

Where  $I_{sd}$  and  $I_{sq}$  are the d-axis and q-axis component of current in the frequency domain respectively. While,  $V_{ind}$  and  $V_{inq}$  are the d-axis and q-axis inverter voltage in frequency domain respectively.

From the equations 2.40 and 2.41, the plant transfer functions for active and reactive power controllers are given as

$$\frac{I_{sd}}{V_{ind}} = \frac{-1}{R_f + sL_f} \tag{2.42}$$

$$\frac{I_{sq}}{V_{inq}} = \frac{-1}{R_f + sL_f} \tag{2.43}$$

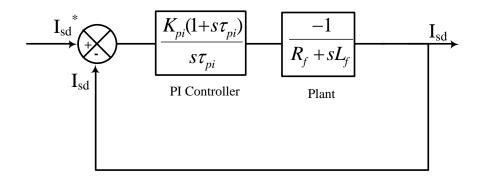

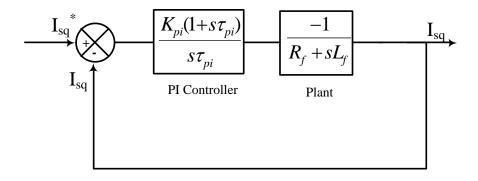

From the above discussion, the derived controller block diagrams for active and reactive power controllers are shown in figures 2.8 and 2.9 respectively. Where,  $K_{pi}$  is the current controller gain and  $\tau_{pi}$  is the current controller time constant.

Fig. 2.8 Block diagram for  $I_{sd}$  controller

Fig. 2.9 Block diagram for  ${\cal I}_{sq}$  controller

#### DC bus voltage controller

DC bus voltage controller is responsible for controlling the DC bus voltage at any prescribed load conditions. The plant for the DC voltage controller can be derived as follows.

The current through the DC load (DC current) is

$$I_{dc}(t) = C_{dc} \frac{dV_{dc}(t)}{dt}$$

(2.44)

Where,  $C_{dc}$  is the capacitance of DC bus capacitor,  $I_{dc}(t)$  is the instantaneous DC current and  $V_{dc}(t)$  is the instantaneous DC bus voltage. The above equation can

be converted into frequency domain as follows

$$I_{dc} = sC_{dc}V_{dc} (2.45)$$

In the equation (2.45),  $I_{dc}$  represents the DC current in the frequency domain and  $V_{dc}$  represents the DC voltage in the frequency domain. The equation (2.45) can be rewritten as

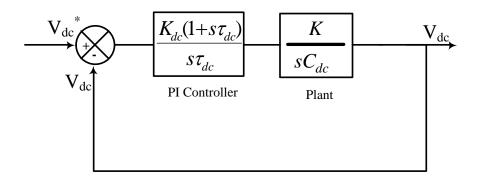

$$V_{dc} = \frac{I_{dc}}{sC_{dc}} \tag{2.46}$$

But, here as explained above DC bus controller acts as outer loop and output of the controller will be the reference for inner real power controller. From the equation (2.46), it is able to obtain the DC bus controller Plant transfer function as  $\frac{1}{sC_{dc}}$ .

Here, the obtained transfer function is between DC bus voltage  $(V_{dc})$  and DC current  $(I_{dc})$ . But in the case of a FEC controller, this controller acts as outer loop controller. So the DC voltage controller will generate the reference for  $I_{sd}$  controller. So there is a necessity of deriving transfer function of  $V_{dc}$  with respect to  $I_{sd}$ .

From the power balance equation following derivation is carried out.

$$3-\phi power = \sqrt{3} * V_{l-l} * I_{l-l}$$

$$= V_{dc} * I_{dc}$$

$$= \sqrt{3} * \sqrt{3} * V_{ph} * I_{ph}$$

$$= 3 * \frac{V_{peak}}{\sqrt{2}} * \frac{I_{peak}}{\sqrt{2}}$$

$$= \frac{3}{2} * V_{peak} * I_{peak}$$

$$= \frac{3}{2} (\frac{2}{3} V_{sd}) (\frac{2}{3} I_{sd})$$

(2.49)

From Eq.(2.49),  $I_{dc}$  in terms of  $I_{sd}$  can be derived as

$$I_{dc} = \frac{2}{3} * \frac{V_{sd}I_{sd}}{V_{dc}}$$

(2.50)

$I_{dc} = K * I_{sd}$  (2.51)

$$I_{dc} = K * I_{sd} (2.51)$$

Where  $K = \frac{2}{3} \frac{V_{sd}}{V_{dc}}$ , which is the constant relating between  $I_{dc}$  and  $I_{sd}$ . With the above information the controller block diagram for DC bus voltage controller is given in figure 2.10. Where,  $K_{dc}$  is the voltage controller gain and  $\tau_{dc}$  is the voltage controller time constant.

Fig. 2.10 Block diagram for  $V_{dc}$  controller

#### 2.5.3Feed-forward Terms and Inverter Gain

As observed in equations (2.25) and (2.26), there is cross coupling exists between d-axis and q-axis voltage. To ensure the decoupled control in d-q reference frame, feed forward terms  $e_{ffd}$  and  $e_{ffq}$  are subtracted from the outputs of  $I_{sd}$  and  $I_{sq}$ controllers respectively. The expressions for  $e_{ffd}$  and  $e_{ffq}$  are given below.

$$e_{ffd} = -V_{sd} - \omega L_f I_{sq} \tag{2.52}$$

$$e_{ffq} = \omega L_f I_{sd} \tag{2.53}$$

While designing the above mentioned controllers, inverter gain  $(G = \frac{V_{dc}}{2})$  has not been considered. The inverter gain can be incorporated after feed-forward terms are subtracted at the output of the controllers. To limit the starting inrush current, the average pole voltage is required to be close to the supply voltage through out the start-up process. The average pole voltage of an inverter is determined by  $V_{sd}^*$  and  $V_{sq}^*$ . Even though in FEC, G is constant during steady state, it increases from the pre-charged value to the reference value during the starting. Hence, instead of holding G constant at its steady state value, it could be varied dynamically in order to reduce the starting current.

All the controllers with the relevant parameters is shown in figure 2.11

Fig. 2.11 Controller Structure

#### 2.5.4 PWM generation

In order to get PWM pulses which goes to the IGBT gate, basically two modulation schemes have been used. They are sine-triangle PWM and space vector pulse width modulation (SVPWM). To obtain 3-phase balanced comparing signals,  $V_{ind}^*$  and  $V_{inq}^*$  are transformed into  $V_{ina}^*$ ,  $V_{ina}^*$  and  $V_{inc}^*$  using  $Cos\theta$  and  $Sin\theta$

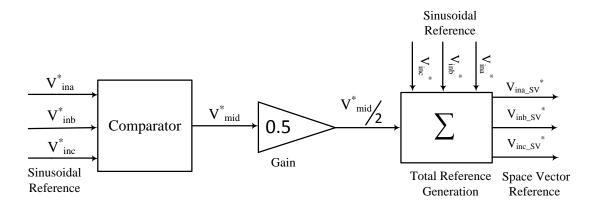

In the case of sinusoidal PWM (SPWM), the highest average phase voltage that can be applied is  $\frac{V_{dc}}{2}$  and in the case of SVPWM is  $\frac{V_{dc}}{\sqrt{2}}$ . Hence in the case of SPWM, the comparing signals will go to the over modulation at the starting, but in the case of SVPWM this effect is not pronounced. In this project, the half of middle value of modulating waves at any instant is added to the original 3-phase modulating signals to generate reference signals equivalent to SVPWM [10]. The

generation of modulating signal equivalent to space vector from the sinusoidal reference signals is shown in figure 2.12.

Fig. 2.12 Generation of SVPWM modulating signals from the SPWM modulating signals

The SVPWM adds zero sequence voltage to the three phase pole voltages. In 3-phase 4-wire system, because of this zero sequence voltage zero sequence current flows through the neutral wire. Also in back-to-back connected converters zero sequence current will circulate between the converters due to the presence of zero sequence voltage. Hence, SVPWM is not suitable for 3-phase 4-wire system and back-to-back converters.

# 2.6 Elimination of lower order harmonics from the line current of a 3-phase 3-wire FEC

In this section a simple control technique to eliminate the lower order harmonics present in the line current of 3-phase 3-wire FEC has been explained. Lower order harmonics are present in the grid current due to dead time in the IGBT module, low switching frequency and low filter inductance size. Moreover grid current controller only with the L-filter pollutes the line current with lower order harmonics and the grid current THD become worse in light load conditions. All the above reasons will allow a low impedance path for 5th harmonic current in the grid current which increases the line current THD [11].

The situation is not that much pronounced in the low voltage converters or high voltage/high currents converters. So there should be a different scheme apart from the conventional technique implemented in order to eliminate this lower order harmonics. The implemented technique has one loop parallel harmonic compensation structure, which is implemented parallel to the fundamental vector control loop. This type of implementation does not effect the dynamics of the original controller loop and also removes further hardware modifications.

### 2.6.1 Harmonic elimination technique

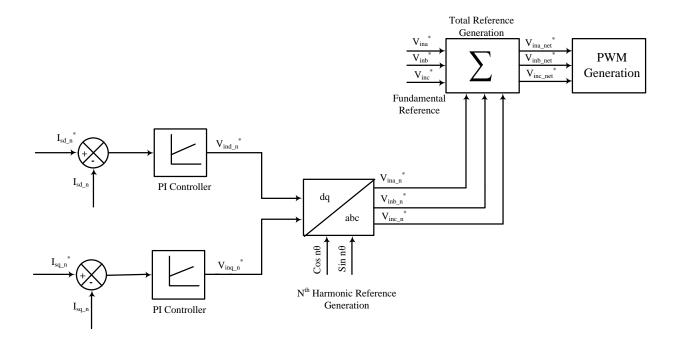

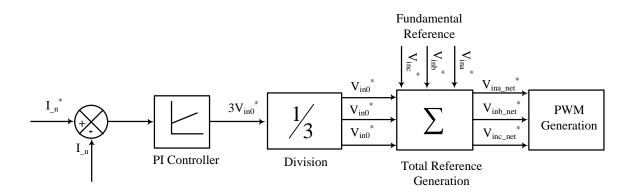

The basic control structure for nth harmonic elimination is shown in figure 2.13. The elimination control of each lower order harmonic is done in its own synchronous reference frame, where it behaves like a DC quantity. So PI controllers are sufficient to make each harmonic's d-axis component and q-axis component to zero.

The transformation from the stationary reference frame to the nth harmonic reference frame is only possible, if  $Cosn\theta$  and  $Sinn\theta$  are available. These quantities can be obtained from fundamental unit vectors  $Cos\theta$  and  $Sin\theta$  using trigonometric expansion formulas. Out put of the nth harmonic  $I_{sd\_n}$  and  $I_{sq\_n}$  controllers will be  $V_{ind\_n}^*$  and  $V_{inq\_n}^*$  respectively.  $V_{ind\_n}^*$  and  $V_{inq\_n}^*$  will then transform into stationary quantities  $V_{ina\_n}^*$ ,  $V_{inb\_n}^*$  and  $V_{inc\_n}^*$ . All these harmonic voltage references  $(V_{ina\_n}^*, V_{inb\_n}^*, V_{inc\_n}^*)$  are then added together with the fundamental reference voltages  $(V_{ina}^*, V_{inb}^*, V_{inc}^*)$  to generate the resultant voltage references  $(V_{ina\_net}^*, V_{inb\_net}^*, V_{inc\_net}^*)$  which are used to generate PWM pulses.

Each step by step procedure for elimination technique are explained in subsequent sections.

### PLL for nth harmonic

As explained above, in order to transform the quantities from stationary reference frame to the nth harmonic rotating reference frame information about  $Cosn\theta$  and  $Sinn\theta$  are necessary. Information on  $Cos\theta$  and  $Sin\theta$  are obtained from funda-

Fig. 2.13 Control structure for *nth* Harmonic elimination

mental PLL as explained in section 2.5.1. In this project 5th (ie n = 5) harmonic content is eliminated from the actual grid current. The derivation of  $Cos5\theta$  and  $Sin5\theta$  from the  $Cos\theta$  and  $Sin\theta$  are explained below.

$$Cos2\theta = 2Cos^{2}\theta - 1$$

$$Sin2\theta = 2Sin\theta Cos\theta$$

$$Cos3\theta = Cos2\theta Cos\theta - Sin2\theta Sin\theta$$

$$Sin3\theta = Sin2\theta Cos\theta + Cos2\theta Sin\theta$$

$$Cos5\theta = Cos3\theta Cos2\theta - Sin3\theta Sin2\theta$$

$$Sin5\theta = Sin3\theta Cos2\theta + Cos3\theta Sin2\theta$$

$$(2.54)$$

### **Harmonic Extraction Process**

Since harmonic elimination controllers are implemented in nth harmonic reference frame, there is a need for harmonic current/voltage extraction from the actual current/voltage. This process of extraction is explained in figure 2.14.

The algorithm basically consists of two cascaded stages. In the first stage, ac-

Fig. 2.14 Harmonic Extraction Algorithm

tual signal is transformed into fundamental reference frame using low pass filters. From the fundamental reference frame which will again convert back to stationary reference frame, but in this case the stationary signal only contains the fundamental component. Then this fundamental component is subtracted from the actual signal to get the only the harmonic components. Second stage involves the required nth harmonic extraction in the nth harmonic d-q reference frame using nth harmonic PLL and low pass filters. This algorithm ensures that the fundamental ripples are eliminated from the harmonic reference frame.

## 2.7 Three-phase Four-wire FEC

3-phase 4-wire FEC is necessary in the case of domestic applications and single phase load. For this supply neutral should be connected to converter which ensures earth fault protection.[12; 13]

The neutral connection mainly done in two ways. One is supply neutral wire could be connected to the mid-point of the DC bus and another option is to have an additional leg in the converter and to connect the supply neutral to the mid-point of this additional leg. [14; 15]. In this project supply neutral has been connected to the mid-point of the DC bus as shown in figure 2.15

So far controlling and modeling concerned, the basic structure of controller and modeling will remain same as in 3-phase 3-wire FEC. Additional modeling

Fig. 2.15 3-phase 4-wire FEC

and control techniques should be implemented in 3-phase 4-wire FEC compared to 3-phase 3-wire FEC in order to take care of common mode current, which will flow through the neutral wire. The detailed modeling and controller design for 3-phase 4-wire FEC are explained in subsequent sections.

## 2.7.1 Modeling and control of 3-phase 4-wire FEC

The main challenge in modeling of 3-phase 4-wire FEC is taking care of common mode (zero sequence) current, which flows through the neutral wire. The converter in the figure 2.15 can be regarded as three independent single-phase half-bridge FEC (see figure 2.16(a)) sharing common DC bus [16].

Fig. 2.16 xth phase half bridge FEC

In three phase four wire system instantaneous line current consists of a differential mode current and common mode current. In this case the *xth* phase current can be written as given below.

$$i_x = i_{xd} + i_{CM} (2.56)$$

where

$$i_{CM} = \frac{i_a + i_b + i_c}{3}$$

(2.57)

Where  $i_x$  is the instantaneous current at xth phase,  $i_{CM}$  is the common mode current and  $i_{xd}$  is the differential mode current.

The common mode current  $i_{CM}$  is same in three phases. The inductors offer inductance  $L_f$  for both common mode and differential mode currents, because there is no mutual coupling between the inductors.

#### Reasons for common mode current

From the circuit 2.16(a), it is clear that common mode current can flow through the neutral wire, if there is a mismatch in the voltages of two DC capacitors  $(V_{dc1} \neq V_{dc2})$  at the steady state. This mismatch in voltage arises due to various reasons such as[17; 18]

- Small offsets in the input current measurement

- Offsets in the reference current and measured input voltage

- Small mismatch in the two DC capacitors  $C_{dc}$

- Shunt resistance associated with  $C_{dc}$

- Difference in initial voltage of two DC capacitors

### Elimination of common mode current

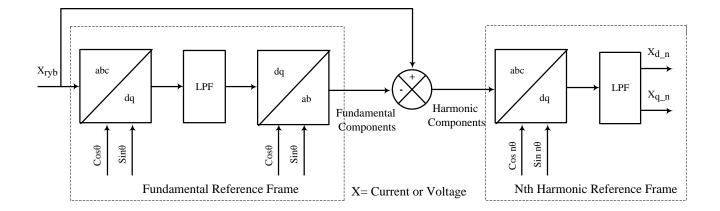

In this project the elimination of zero sequence (common mode) component has been implemented with a PI controller. Since PI controllers can eliminate lower order harmonics from the system, it is sufficient for the elimination of zero sequence component. The additional neutral current controller along with the basic controller is shown in figure 2.17.

Fig. 2.17 Controller block diagram for 3- $\phi$  4-wire FEC

The controller additionally making neutral current to zero using a PI controller along with the other basic controllers of the 3-phase 3-wire FEC. The reference for the PI controller is zero and the feed back should be sensed from neutral current. The output of the PI controller will be divided by three and then added to the each 3-phase reference, which generated using basic controller loops. The above controller make sure that there is no voltage difference between the two DC capacitors and thereby neutral current is zero.

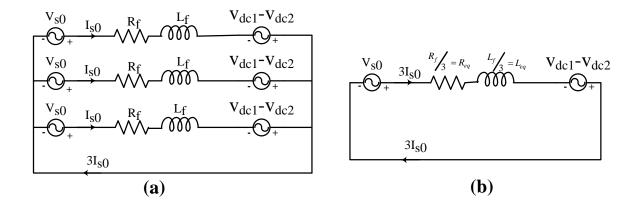

The plant for the PI controller can be derived with the help of figure 2.18(a) and 2.18(b). Figure 2.18(a) shows the zero-axis electrical circuit of 3-phase 4-wire FEC, where  $V_{s0}$  is the zero sequence component present in the grid voltage,  $I_{s0}$  is the zero sequence component in the line current,  $3I_{s0} = I_N$  is the current flows through neutral wire and  $(V_{dc1} - V_{dc2})$  is the difference between the voltage of two DC capacitors  $C_{dc}$ .

Figure 2.18(b) shows the simplified circuit of the zero-axis circuit, where  $R_f/3 = R_{eq}$  is the effective resistance in the zero-axis path and  $L_f/3 = L_{eq}$  is the effective inductance in the zero-axis path. From Figure 2.18(b), the transfer function between common mode voltage  $V_{CM}$  and neutral current  $I_N$  can be derived as shown below.

$$\frac{V_{CM}}{I_N} = \frac{1}{R_{eq} + sL_{eq}} {2.58}$$

Fig. 2.18 (a) Zero-axis circuit of 3-phase 4-wire FEC(b) Equivalent zero-axis circuit of 3- $\phi$  4-wire

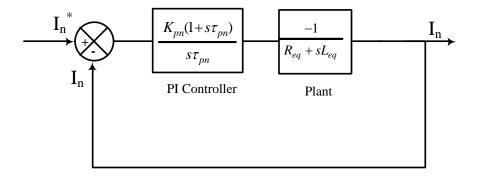

With the above discussion the derived controller block diagram for neutral current controller is given in figure 2.19, where  $K_{pn}$  is the neutral current controller gain and  $\tau_{pn}$  is the neutral current controller time constant.

Fig. 2.19 (a) Neutral current controller for a 3-phase 4-wire FEC

## 2.7.2 Switching frequency distortions in line and neutral current

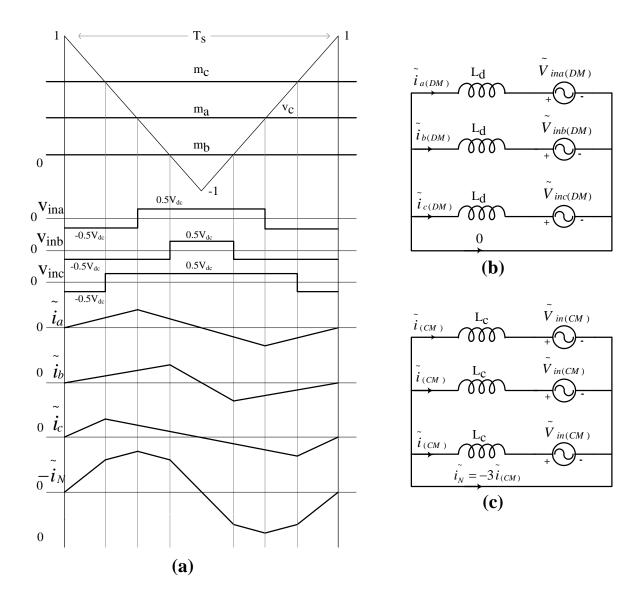

The switching frequency distortions in the line and neutral currents of a four wire FEC causes EMI, power loss and device stress [19; 20]. So over all distortions in the line currents and neutral currents must be reduced. The distortions in a two-level, 3-phase 4-wire FEC with sine-triangle PWM is shown in figure 2.20(a).

The instantaneous pole voltage  $v_{inx}$  shown in figure 2.20(a) can be divided into average value  $V_{inx}$  and a switching frequency ripple  $\tilde{v}_{inx}$ . The ripple voltage  $\tilde{v}_{inx}$  causes ripple current  $\tilde{i}_x$  in xth phase as shown in figure 2.20(a).

The ripple current  $\tilde{i}_x$  at any phase x is zero both at the start and the end of switching cycle  $T_s$ . Figure 2.20(a) qualitatively shows the variations of line and neutral current ripples over the switching cycle  $T_s$ . From the figure 2.20(a), it can be interpreted that the distortions in the neutral current  $\tilde{i}_N$  is much higher than line current ripples  $(\tilde{i}_a, \tilde{i}_b, \tilde{i}_c)$  as  $\tilde{i}_N = -(\tilde{i}_a + \tilde{i}_b + \tilde{i}_c)$ .

Fig. 2.20 (a)Line and neutral current distortions with SPWM(b)Differential mode ripple equivalent circuit(c)Common mode ripple equivalent circuit

### Analysis of line and neutral current distortions

As discussed above difference in DC capacitors voltage causes common mode current through neutral. Besides this unbalance in the pole voltage causes switching frequency current in the neutral wire. The unbalance in the pole voltage, that is common mode component in the pole voltage is given in Eq.(2.59). Therefore switching ripple in xth phase can be written as a combination of differential mode switching ripple  $(\tilde{V}_{inx(DM)})$  and common mode switching ripple  $(\tilde{V}_{in(CM)})$  as given in Eq.(2.60).

$$\tilde{V}_{in(CM)} = \frac{\tilde{V}_{ina} + \tilde{V}_{inb} + \tilde{V}_{inc}}{3} \tag{2.59}$$

$$\tilde{V}_{inx} = \tilde{V}_{inx(DM)} + \tilde{V}_{in(CM)} \tag{2.60}$$

The ripple voltages  $\tilde{V}_{inx(DM)}$  and  $\tilde{V}_{in(CM)}$  causes ripple currents  $\tilde{i}_{j(DM)}$  and  $\tilde{i}_{(CM)}$  in the xth phase line. This is shown in figure 2.20(b) and 2.20(c) respectively. Where  $\tilde{i}_{x(DM)}$  is the differential mode current in xth phase and  $\tilde{i}_{(CM)}$  is the common mode current in the system. The expression for common mode current  $\tilde{i}_{(CM)}$  is given in Eq.(2.61). Similar to pole voltage, ripple current in the xth phase can be written as a combination of differential mode switching ripple current  $(\tilde{i}_{x(DM)})$  and common mode switching ripple current  $(\tilde{i}_{(CM)})$  as given in Eq.(2.62). This common mode ripple current causes common mode switching distortion in the neutral wire as shown Eq.(2.63).

$$\tilde{i}_{(CM)} = \frac{\tilde{i}_a + \tilde{i}_b + \tilde{i}_c}{3} \tag{2.61}$$

$$\tilde{i}_x = \tilde{i}_{x(DM)} + \tilde{i}_{(CM)} \tag{2.62}$$

$$\tilde{i}_N = -3\tilde{i}_{(CM)} \tag{2.63}$$

### Elimination of neutral current distortions

From the above discussion it is clear that neutral current distortions is happening because of unbalance in the pole voltage ripple  $(\tilde{V}_{in(CM)})$ . The ripple voltage  $\tilde{V}_{inx(DM)}$  and  $(\tilde{V}_{in(CM)})$  depend on a number of factors such as system frequency, switching frequency and PWM scheme. As basic controller for the 3-phase 4-wire

FEC is same as that of 3-phase 3-wire FEC, nothing can be done to eliminate  $\tilde{V}_{in(CM)}$ . So the only possibility is to reduce the neutral current distortions.

From the figure 2.20(c), it is clear that  $\tilde{i}_{(CM)}$  not only depend on magnitude of the  $\tilde{V}_{inv(CM)}$  but also the impedance offered by three common mode inductance. In the case of three single phase inductors inductance offered by  $L_f$  will be same for both common mode current and differential mode current, that is  $L_c = L_d = L_f$ .

Also from figure 2.20(b), it is clear that differential mode current in xth phase  $\tilde{i}_{x(DM)}$ , does not flows through the neutral wire. Thus the figure 2.20(b) represents the current in a 3-phase 3-wire FEC and figure 2.20(c) represents the additional common mode equivalent circuit in the case of a 3-phase 4-wire system. So the basic controller for both 3-phase 3-wire FEC and 3-phase 4-wire FEC will be same as long as there is no changes in the equivalent circuit shown in figure 2.20(b). Therefore an additional change in the equivalent circuit shown in figure 2.20(c) does not effect the main controller part.

So an additional modifications should be done in the figure 2.20(c) in order to reduce the common mode current distortions. One such possibility is to have an additional inductance  $(L_{cn})$  in the neutral path as shown in figure 2.21, which will offer additional impedance for the common mode switching current and thereby reducing the switching distortions from the neutral wire. Thus without affecting the main controller reduction in neutral current distortions is possible.

Fig. 2.21 3-phase 4-wire FEC with additional inductance  $(L_{cn})$  in the neutral wire

## 2.8 Conclusion

This chapter discussed the concept of vector control and modeled FEC in synchronous reference frame. PLL has been used in the modeling and controller in order to synchronize with the grid. The complete derivation and block diagram of all the controllers are discussed. The difference in control strategy of 3-phase 3-wire FEC and 3-phase 4-wire FEC has been taken care off. Discussed the technique for elimination of lower order harmonics from the line current of a FEC with relevant equations.

### CHAPTER 3

# HARDWARE ORGANISATION AND CONTROL IMPLEMENTATION OF FEC

## 3.1 Introduction

In this chapter, the features about TMS320F28335, 32-bit floating point Digital Signal Controller from Texas Instruments and the brief overview about the hardware organization that help in implementing vector control of FEC will be explained. The additional circuitry developed for proper interfacing and protection will also be discussed. The chapter also explains about the controller design and implementation for the vector control of FEC. The design is done following a per unit system with defined base quantities.

## 3.2 Brief Overview of the TMS320F28335