## COMPACT MODELING OF SOI-LDMOS TRANSISTORS

A Project Report

submitted by

#### **NITIN PRASAD**

in partial fulfilment of the requirements

for the award of the degree of

#### **BACHELOR OF TECHNOLOGY**

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS. JUNE 2014

#### THESIS CERTIFICATE

This is to certify that the thesis titled **Compact Modeling of SOI-LDMOS Transistors**, submitted by **Nitin Prasad**, to the Indian Institute of Technology, Madras, for the award of the degree of **Bachelor of Technology**, is a bona fide record of the research work done by him under our supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

**Prof. Anjan Chakravorty**

Research Guide Associate Professor Dept. of Electrical Engg. IIT-Madras, 600 036

Place: Chennai

Date: June 6, 2014

**Prof. Nandita Dasgupta**

Research Guide Professor Dept. of Electrical Engg. IIT-Madras, 600 036 **Prof. Amitava Dasgupta** Research Guide

Professor

Dept. of Electrical Engg.

IIT-Madras, 600 036

## Contents

| A            | ckno             | wledge   | ements                                                    | i   |

|--------------|------------------|----------|-----------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra            | ct       |                                                           | iii |

| C            | ontei            | nts      |                                                           | v   |

| Li           | $\mathbf{st}$ of | Figur    | es                                                        | vii |

| A            | bbre             | viation  | ls                                                        | ix  |

| Sy           | mbc              | ols      |                                                           | xi  |

| 1            | Inti             | roducti  | ion                                                       | 1   |

|              | 1.1              | Overv    | iew of power semiconductor devices                        |     |

|              | 1.2              |          | nt scenario in LDMOS transistor modeling                  |     |

|              | 1.3              | •        | tives                                                     |     |

|              | 1.4              | Struct   | sure of the thesis                                        | 5   |

| 2            | Ana              | alysis o | of Physical Effects                                       | 7   |

|              | 2.1              | Device   | e Structure                                               | 7   |

|              | 2.2              | Static   | Currents                                                  | 9   |

|              |                  | 2.2.1    | Analysis of potential drops across the three regions      | 10  |

|              |                  | 2.2.2    | Gate and drain voltage dependence of the quasi-saturation |     |

|              |                  |          | current.                                                  |     |

|              |                  |          | 2.2.2.1 Drain voltage dependence                          |     |

|              |                  | ъ.       | 2.2.2.2 Gate voltage dependence                           |     |

|              | 2.3              |          | nal Charge assignments                                    |     |

|              |                  | 2.3.1    | Region-I surface charges                                  |     |

|              |                  | 2.3.2    | Region-II surface charges                                 |     |

|              |                  | 2.3.3    | p-n junction charges                                      |     |

|              |                  | 2.3.4    | Region-III charges                                        | 16  |

| 3            | Mo               | del and  | d Verilog-A implementation                                | 17  |

|              | 3.1              | Static   | current model                                             | 18  |

|              |                  | 3.1.1    | Formulation of current in channel region                  | 19  |

|              |                  | 3.1.2    | Formulation of current under gate oxide                   | 20  |

|              |                  | 3.1.3    | Formulation of current under field oxide                  | 22  |

*Contents* vi

|          |     | 3.1.3.1        | 2-D resistor under velocity saturation        | 22        |

|----------|-----|----------------|-----------------------------------------------|-----------|

|          |     | 3.1.3.2        | Modeling the Gate voltage dependence          |           |

|          |     | 3.1.3.3        | Region-III model                              | 25        |

|          | 3.2 | Charge Model   |                                               | 26        |

|          |     | 3.2.1 The MI   | M20 approach                                  | 26        |

|          |     | 3.2.1.1        | Model proposed by [1]                         | 27        |

|          |     | 3.2.1.2        | Model proposed by [2]                         | 30        |

|          |     | 3.2.1.3        | A Comparative study                           | 31        |

|          |     | 3.2.1.4        | EC Model for MM20 charge partitioning         | 32        |

|          |     | 3.2.2 A New    | Charge Partitioning scheme                    | 32        |

|          |     | 3.2.2.1        | Need for an additional internal node          | 32        |

|          |     | 3.2.2.2        | The proposed charge partitioning scheme       | 33        |

|          |     | 3.2.2.3        | Formulation of charge in region-I             | 34        |

|          |     | 3.2.2.4        | Formulation of charge in region-II            | 37        |

|          |     | 3.2.2.5        | Formulation of the p-n junction charges       | 36        |

|          |     | 3.2.2.6        | EC Model for the proposed charge partitioning | 40        |

| 4        | Dog | ults and Discı | vegione.                                      | 41        |

| 4        | 4.1 |                |                                               | <b>41</b> |

|          | 4.1 |                |                                               | 41        |

|          |     |                |                                               | 42        |

|          | 4.2 |                | haracteristics                                | 42        |

|          | 4.2 | Transient Curr |                                               | 49        |

|          | 4.4 |                | the model and reasons for inaccuracies        | 50        |

|          | 1.1 | Draw sacing of | no model did reasons for maccardess 1111111   |           |

| <b>5</b> | Con |                | •                                             | 57        |

|          | 5.1 |                | e thesis                                      | 57        |

|          | 5.2 | Scope of Futur | e Work                                        | 58        |

|          |     |                |                                               |           |

|          |     |                |                                               |           |

| A        |     |                | s and Constants                               | 59        |

|          | A.1 |                | ter Values                                    | 59        |

|          | A.2 | Constants      |                                               | 61        |

| В        | Sou | rce Codes      |                                               | 63        |

|          | B.1 | MEDICI SOI-I   | LDMOS Source Code                             | 63        |

|          |     | B.1.1 Device   | Definition and Formalism                      | 63        |

|          |     | B.1.2 DC Ana   | alysis                                        | 64        |

|          |     | B.1.3 AC Ana   | alysis                                        | 66        |

|          |     | B.1.4 Transie  | nt Analysis                                   | 68        |

|          | B.2 | 2-D SOI-Resist | for MEDICI Source                             | 69        |

|          | B.3 | Verilog-A Sour | ce Code                                       | 71        |

Bibliography 83

## List of Figures

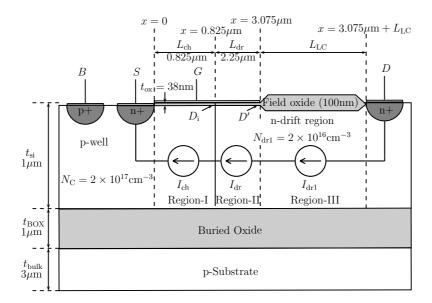

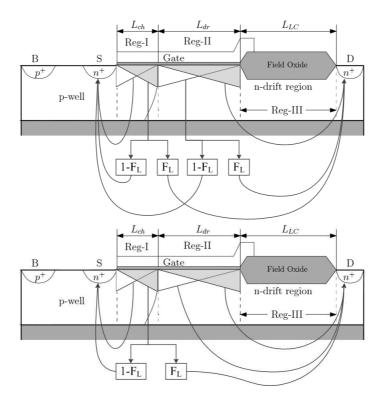

| 2.1 | Schematic cross-section of the investigated SOI-LDMOS transistor.                                                                                                                                                            | 8  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

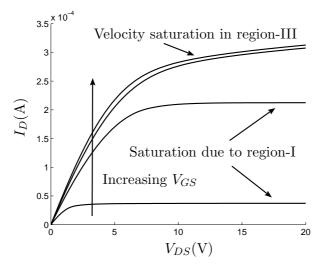

| 2.2 | $I_D - V_{DS}$ characteristics for $V_{GS} = 5, 10, 15$ and 20V, simulated in MEDICI                                                                                                                                         | 10 |

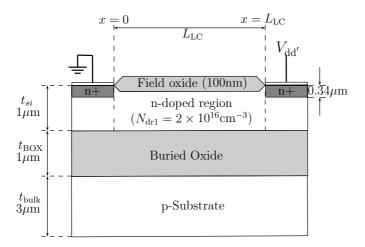

| 2.3 | Schematic cross-section of the 2-D resistor structure simulated to model the velocity saturation characteristics                                                                                                             | 11 |

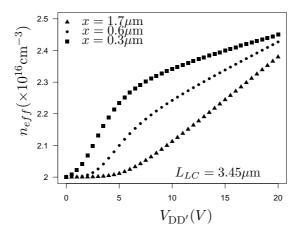

| 2.4 | Variation of charge carrier concentration as a function of voltage across the resistor. The $n_{eff}$ data from MEDICI is probed at $t_{si}/2$ below the top oxide-silicon interface.                                        | 12 |

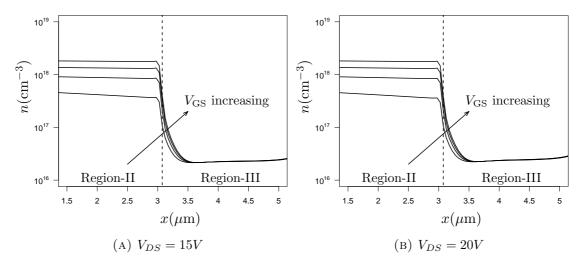

| 2.5 | Net electron density (obtained from MEDICI) as a function of $x$ along the top oxide-semiconductor surface of the device for $V_{GS} = 5, 10, 15, 20V$ . The vertical dashed line represents the $D'$ node shown in Fig. 2.1 | 13 |

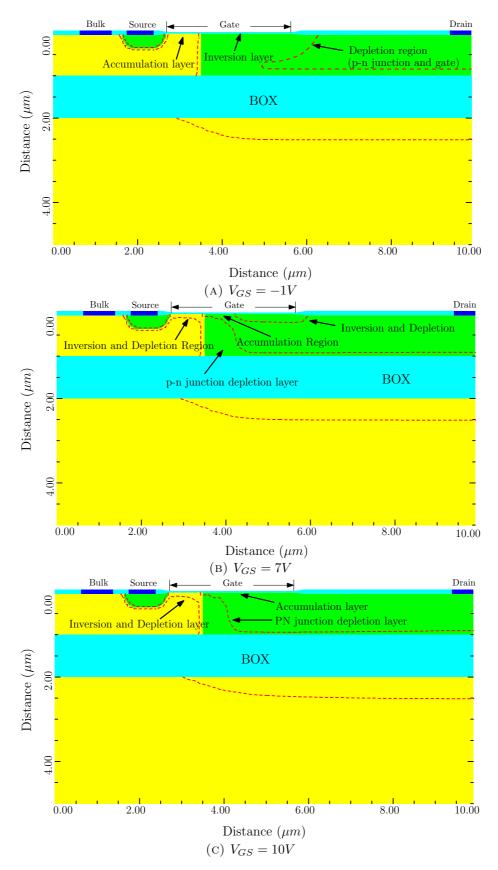

| 2.6 | Cross-section of the SOI-LDMOS transistor indicating the depletion region and other associated charges at various bias points                                                                                                | 14 |

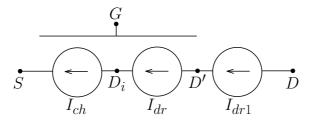

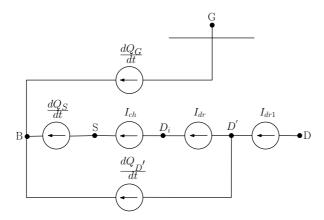

| 3.1 | EC Model for static MOSFET currents                                                                                                                                                                                          | 18 |

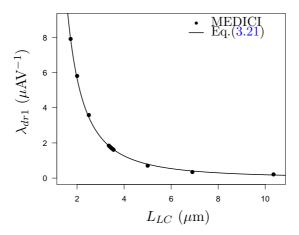

| 3.2 | Inverse square law behaviour (as described in (3.21)) of $\lambda_{dr1}$ at high $V_{DD'}(=20V)$                                                                                                                             | 24 |

| 3.3 | Charge partitioning under strong (top) and weak (bottom) inversions of region-I                                                                                                                                              | 29 |

| 3.4 | EC Model for static and dynamic and LDMOS transistor currents using MM20 formulation                                                                                                                                         | 30 |

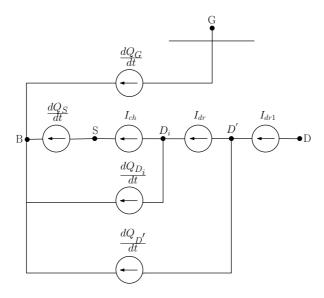

| 3.5 | EC Model for static and dynamic and LDMOS transistor currents using the proposed formulation                                                                                                                                 | 40 |

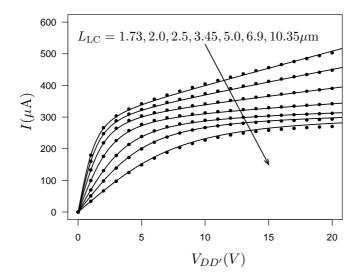

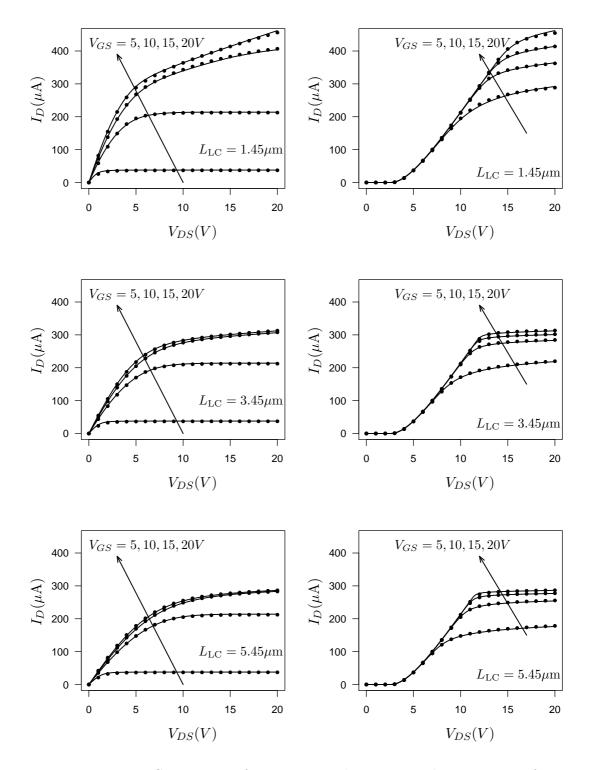

| 4.1 | Comparison of 2-D resistor characteristics for different resistor lengths obtained using the proposed model (solid lines) with MEDICI data                                                                                   |    |

| 4.2 | (symbols)                                                                                                                                                                                                                    | 42 |

|     | and $5.45\mu m$ , with MEDICI data (symbols)                                                                                                                                                                                 | 43 |

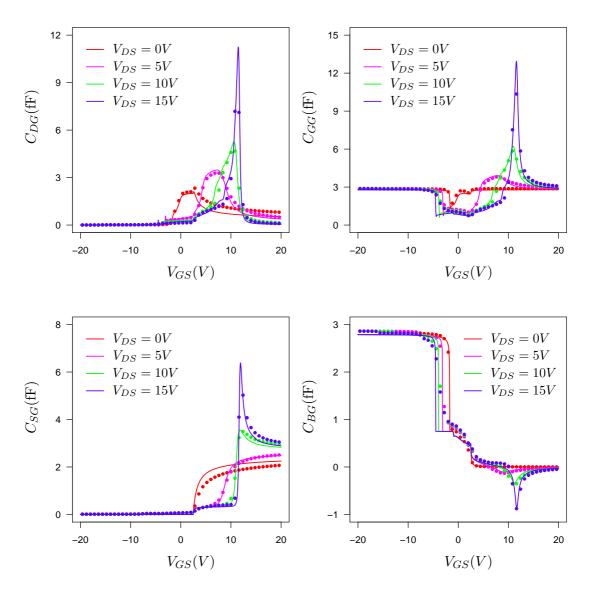

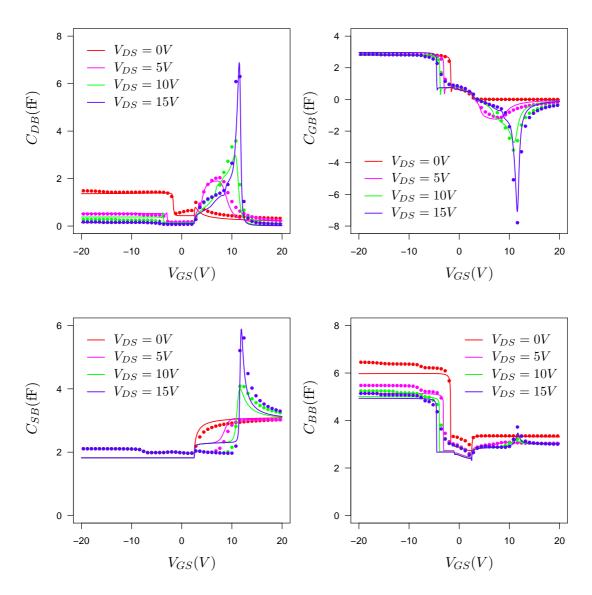

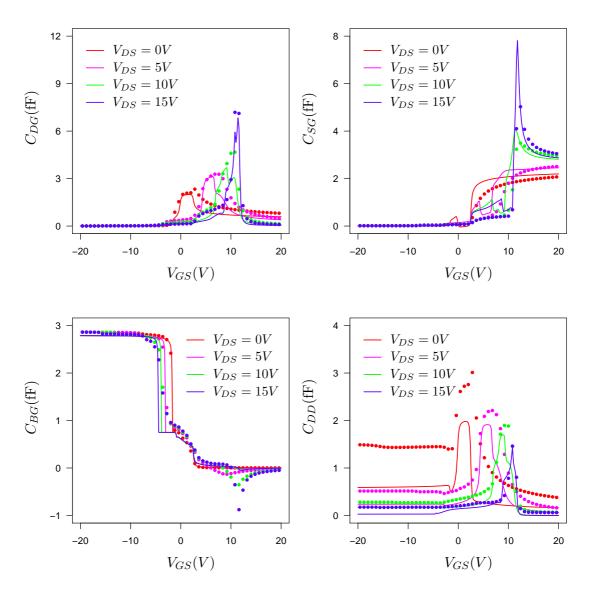

| 4.3 | Comparison of $C_{xG} - V_{GS}$ ( $x \in \{D, G, S, B\}$ ) plots obtained by using the proposed model (solid lines), for $V_{DS} = 0, 5, 10, 15V$ , with                                                                     |    |

|     | MEDICI data (symbols)                                                                                                                                                                                                        | 45 |

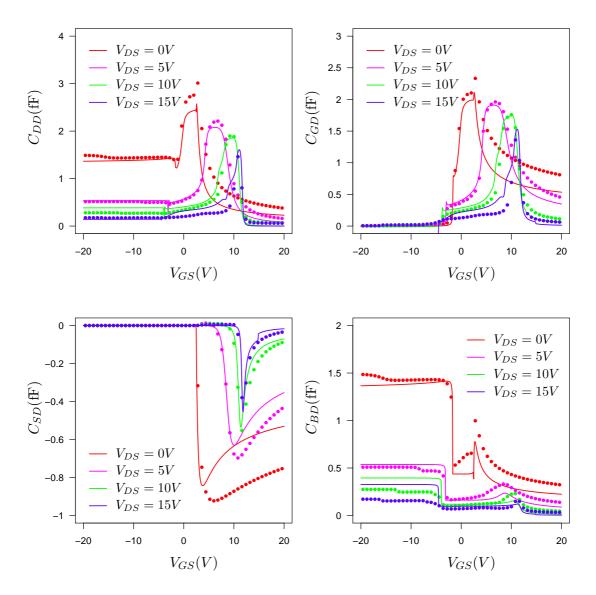

| 4.4 | Comparison of $C_{xD} - V_{GS}$ ( $x \in \{D, G, S, B\}$ ) plots obtained by using the proposed model (solid lines), for $V_{DS} = 0, 5, 10, 15V$ , with                                                                     |    |

|     | MEDICI data (symbols)                                                                                                                                                                                                        | 46 |

List of Figures viii

| 4.5  | Comparison of $C_{xS} - V_{GS}$ $(x \in \{D, G, S, B\})$ plots obtained by            |    |

|------|---------------------------------------------------------------------------------------|----|

|      | using the proposed model (solid lines), for $V_{DS} = 0, 5, 10, 15V$ , with           |    |

|      | MEDICI data (symbols)                                                                 | 47 |

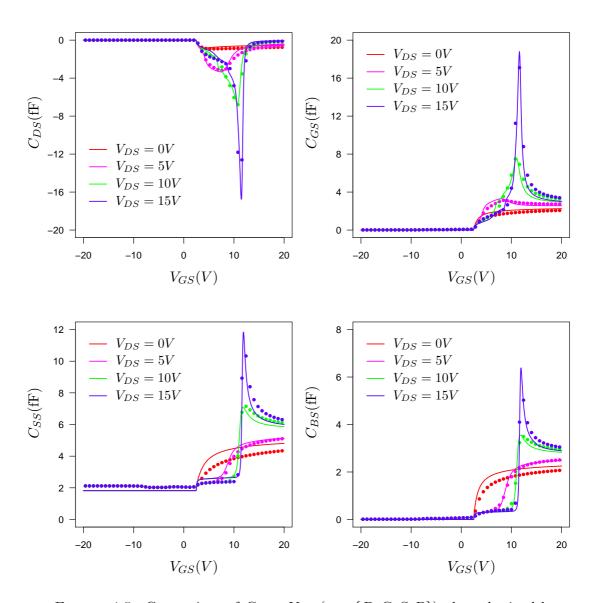

| 4.6  | Comparison of $C_{xB} - V_{GS}$ $(x \in \{D, G, S, B\})$ plots obtained by            |    |

|      | using the proposed model (solid lines), for $V_{DS} = 0, 5, 10, 15V$ , with           |    |

|      | MEDICI data (symbols)                                                                 | 48 |

| 4.7  | Comparison of a few Capacitance plots obtained using the MM20                         |    |

|      | charge partitioning scheme (solid lines), for $V_{DS} = 0, 5, 10, 15V$ ,              | 40 |

| 4.0  | with MEDICI data (symbols)                                                            | 49 |

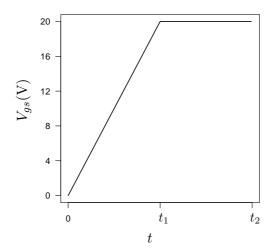

| 4.8  | Input voltage profile at the gate terminal for transient simulations.                 | 50 |

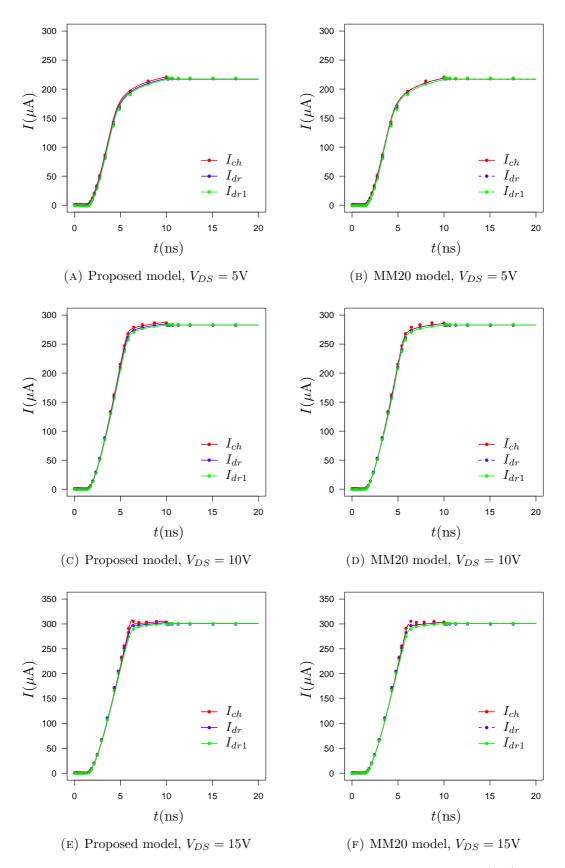

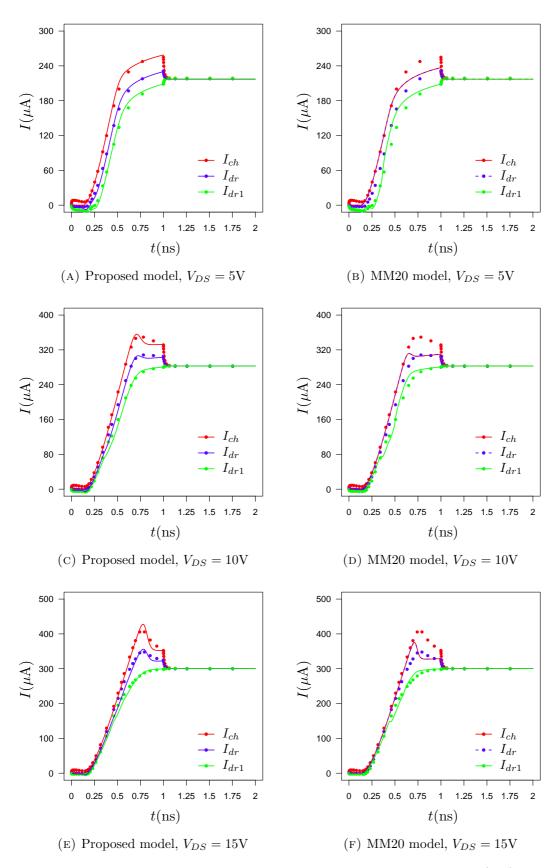

| 4.9  | Response of $I_{ch}$ , $I_{dr}$ and $I_{dr1}$ from the proposed model (left) and that |    |

|      | of MM20 (right) when $V_{GS}$ is ramped up at peak to peak rise time                  |    |

|      | of 10ns. Solid lines represent model results and symbols represent                    |    |

|      | MEDICI data                                                                           | 51 |

| 4.10 | Response of $I_{ch}$ , $I_{dr}$ and $I_{dr1}$ from the proposed model (left) and that |    |

|      | of MM20 (right) when $V_{GS}$ is ramped up at peak to peak rise time                  |    |

|      | of 1ns. Solid lines represent model results and symbols represent                     |    |

|      | MEDICI data                                                                           | 52 |

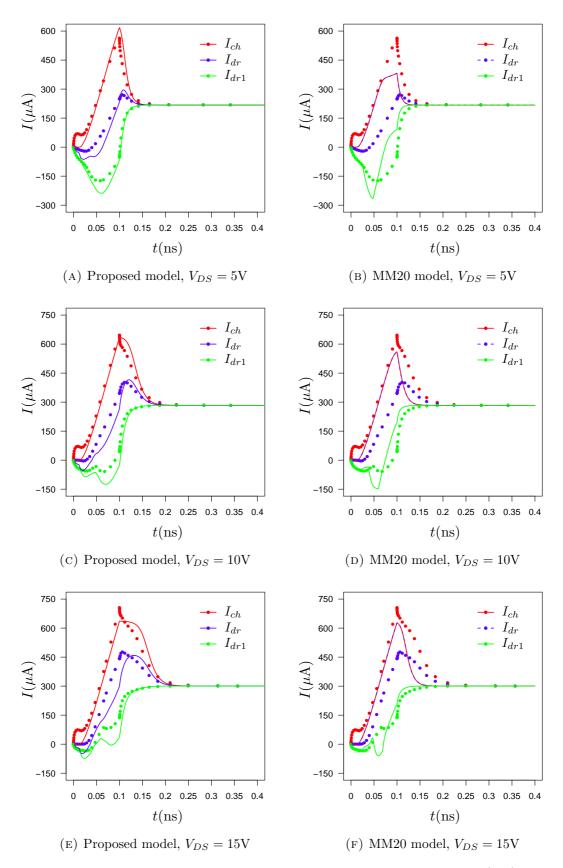

| 4.11 | Response of $I_{ch}$ , $I_{dr}$ and $I_{dr1}$ from the proposed model (left) and that |    |

|      | of MM20 (right) when $V_{GS}$ is ramped up at peak to peak rise time                  |    |

|      | of 0.1ns. Solid lines represent model results and symbols represent                   |    |

|      | MEDICI data                                                                           | 53 |

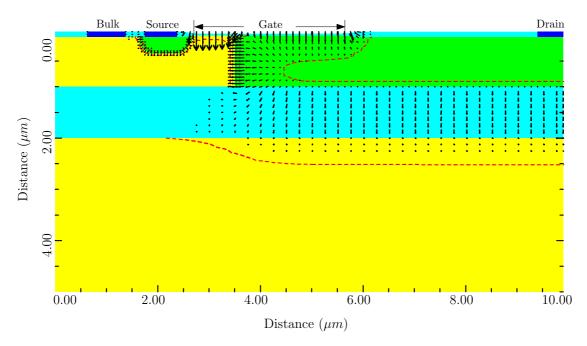

| 4.12 | Electric Field lines for $V_{GG} = 4V$ and $V_{DG} = 10V$                             | 54 |

### Abbreviations

MOSFET Metal Oxide Semiconductor Field Effect Transistor

SOI Silicon On Insulator

**BOX** Buried Oxide

**LDMOS** Lateral Double Diffused MOS

**VDMOS** Vertical Double Diffused MOS

**HVIC** High Voltage Integrated Circuit

**RFIC** Radio Frequency Integrated Circuit

JFET Junction Field Effect Transistor

NMOS N-channel MOSFET

PMOS P-channel MOSFET

**DC** Direct Current

**AC** Alternating Current

**WD** Ward-Dutton

MWD Modified Ward-Dutton

## **Symbols**

$V_{GS}$  Gate to source voltage

$V_{GB}$  Gate to bulk voltage

$V_{GC}$  Gate to quasi-Fermi level voltage

$V_{DS}$  Drain to source voltage

$V_{DiS}$  Voltage drop across channel (region-I)

$V_{D'D_i}$  Voltage drop across drift region under gate oxide (region-II)

$V_{DD^{\prime}}$  Voltage drop across drift region under field oxide (region-III)

$V_{GD_i}$  Gate to  $D_i$  voltage  $V_{GD'}$  Gate to D' voltage

$V_{sat.ch}$  Channel saturation voltage

$V_{sat.dr}$  region-II saturation voltage

$V_{DiS,eff}$  Effective voltage drop in region-I

$V_{D'D_{i},eff}$  Effective voltage drop in region-II

$I_{DS}$  Drain to source current

$I_{ch}$  Channel region current

$I_{dr}$  Current in region-II

$I_{dr1}$  Current in region-III

$L_{ch}$  Length of region-I

$L_{dr}$  Length of region-II

$L_{LC}$  Length of region-III

W Width of LDMOS

$C_{ox}$  Oxide capacitance

$t_{ox}$  Oxide thickness

A Cross section area of LDMOS

$t_{si}$  Silicon film thickness

$t_{BOX}$  Thickness of buried oxide

Symbols xii

| $N_{ch}$        | Doping concentration in region-I               |

|-----------------|------------------------------------------------|

| $N_{dr}$        | Doping concentration in region-II              |

| $N_{dr1}$       | Doping concentration in region-III             |

| $V_T$           | Thermal voltage                                |

| $\epsilon_{si}$ | Permittivity of silicon                        |

| $\epsilon_{ox}$ | Permittivity of silicon dioxide                |

| $\psi_s^{ch}$   | Surface potential in region-I                  |

| $\psi_s^{dr}$   | Surface potential in region-II                 |

| $Q_{inv}^{ch}$  | Inversion charge per unit area in region-I     |

| $Q_{acc}^{ch}$  | Accumulation charge per unit area in region-I  |

| $Q_{dep}^{ch}$  | Depletion charge per unit area in region-I     |

| $Q_{gate}^{ch}$ | Total gate charge in region-I                  |

| $Q_{acc}^{dr}$  | Accumulation charge per unit area in region-II |

| $Q_{dep}^{dr}$  | Depletion charge per unit area in region-II    |

| $Q_{inv}^{dr}$  | Inversion charge per unit area in region-II    |

| $Q_{gate}^{dr}$ | Total gate charge in region-II                 |

| $Q_G$           | Charge assigned to gate terminal               |

| $Q_D$           | Charge assigned to drain terminal              |

| $Q_S$           | Charge assigned to source terminal             |

| $Q_B$           | Charge assigned to bulk terminal               |

| $Q_{D_i}$       | Charge assigned to $D_i$ terminal              |

| $Q_{D'}$        | Charge assigned to $D^{'}$ terminal            |

| $V_{FB}^{ch}$   | Flat band voltage in channel                   |

| $V_{FB}^{dr}$   | Flat band voltage in region-II                 |

| $v_{sat}^{ch}$  | Saturation velocity of electrons in region-I   |

| $v_{sat}^{dr}$  | Saturation velocity of electrons in region-II  |

| $v_{sat}$       | Saturation velocity of electrons in region-III |

| $\mu_{ch}$      | Effective mobility in channel                  |

| $\mu_{dr}$      | Effective mobility in region-II                |

| $\mu_{dr1}$     | Zero field mobility in region-III              |

| $\theta_{3,ch}$ | Velocity saturation parameter in channel       |

| $	heta_1$       | Channel mobility reduction parameter           |

| $\theta_2$      | Channel mobility reduction parameter           |

| $\theta_{3,dr}$ | Velocity saturation parameter in region-II     |

Symbols xiii

| $\theta_{dr1}$   | Velocity saturation parameter in region-III    |

|------------------|------------------------------------------------|

| $\theta_{1,dr1}$ | Velocity saturation parameter in region-III $$ |

| $\lambda_{ch}$   | Channel length modulation parameter            |

| $\lambda_{dr1}$  | Drift length modulation parameter              |

| $C_{ij}$         | Capacitance between terminals $i$ and $j$      |

## Chapter 1

#### Introduction

#### 1.1 Overview of power semiconductor devices

Power semiconductor devices have become integral components of the semiconductor industry in designing high voltage integrated circuits (HVICs). They have come a long way since the inception of bipolar junction transistors and thyristors. Although the first commercial HV devices were introduced by Texas Instruments in 1954, it took almost a decade for them to find practical applications in high voltage circuits. Thyristors were the first class of power devices but they had the disadvantage of poor switching speed and difficulty of integration.

Further advancement in silicon fabrication technology let to the development of novel device structures such as power MOSFETs. These devices were introduced in late seventies [3] and they made way for the development of new generation of devices. By breaking the symmetry of a conventional MOSFET, the power MOSFETs were developed. The symmetry was broken to improve the the reverse blocking capability of the device [4]. One such power MOSFET that was developed was the lateral double diffused metal oxide semiconductor (LDMOS) transistors.

One of the main advantages of LDMOS devices is that they can be easily integrated with low voltage circuitry. They continue to be industry standard even today for medium voltage power applications. Their main drawback is the fact that they suffer from low current rating and breakdown voltage on-resistance trade off. To increase the voltage handling capabilities of this device, we need to increase the

length of lightly doped drain region across which the reverse voltage is dropped. This increases the area requirements of the device.

To circumvent this problem, vertical double diffused MOS (VDMOS) technology was developed. VDMOS provides larger current ratings and higher breakdown voltage compared to LDMOS[5], but requires complicated process steps and integration with low voltage circuitry is not easy. Though VDMOS finds applications in high voltage industries, medium power applications are still dominated by LDMOS devices.

Nowadays, HVICs and power integrated circuits (PICs) are replacing discrete elements such as DC-DC converter, switch mode power supplies and power amplifiers [6],[7],[8]. Integration of high and low voltage circuits on the same chip improves the overall performance and reduces the chip size. PICs are used as a bridge between power load and low voltage digital logic[9],[10]. They are also useful in Power line communications (PLCs) where digital information is transmitted over a power line. LDMOS devices form an integral part of many of these interesting applications.

## 1.2 Current scenario in LDMOS transistor modeling

With the advent of LDMOS devices in interesting consumer and automotive applications, it becomes essential to develop an accurate model for LDMOS transistors. Recently, fabrication of LDMOS devices on a Silion-on-Insulator (SOI) substrate has become popular. LDMOS fabricated on an SOI substrate offers additional advantages such as lower leakage currents, higher latchup, higher packing density and reduced parasitics[11]. Further, the use of an SOI substrate enables isolation between power devices and low voltage circuitry which is essential in smart power ICs. Thus compact models for SOI-LDMOS transistors capable of modeling device characteristics over wide range of bias and temperature and for various lengths is essential for a fail safe design of power integrated circuits.

There have been many approaches for modeling LDMOS transistors. Two main approaches followed are (i) macro-modeling and (ii) compact modeling. Macro

modeling procedure consists of trying to describe the behavior of device through a circuit consisting of several discrete elements or modules. As the number of effects rises, the number of elements in the circuit increases and results in increase in computation time and convergence problems. There are many existing macro models based on SPICE which consider SPICE models for MOSFETs, JFETS and diodes to model LDMOS[12],[13],[14]. One such macro model uses BSIM4 to model the MOSFET and JFET to model drift region and a shorted PMOS transistors to model capacitance behavior of drift region[15]. These models have a large number of non-physical model parameters.

Compact modeling, on the other hand, maintains device unity through a set of self consistent expressions which are able to produce device behavior. All internal node equations are solved in the model itself, thereby reducing computation time. Also, the expressions obtained are from physical principles and do away with non-physical parameters introduced in macro-modeling. There are several compact models available for SOI-LDMOS, important among them being HiSIM-HV [16][17], EKV model[18],[19],[20] and MM20 HVMOS model[21]. In this thesis, MM20 model developed by NXP semiconductors is used as a basis upon which further formulations have been built. MM20 HVMOS model is a surface potential based model. It models the channel and drift region under the gate oxide of the LDMOS transistor. It does not model the region under field oxide and hence cannot be used for high voltage devices.

The effect of quasi-saturation in drift region under field oxide was considered in [22]. Further, high voltage effects such as impact-ionization, snapback and self-heating in an SOI-LDMOS was successfully modeled by [23]. However, the bias voltage dependence of the quasi-saturation current was not studied in detail in these works. This thesis deals with modeling this effect, along with displaying the scalability of the model with respect to the length of the drift region under the field oxide.

Apart from accurately predicting the DC characteristics of a device, a good model must also accurately predict various capacitances which are important for the AC characteristics of the device. With the integration of LDMOS in high speed circuits such as RFICs, predicting the high speed performance of LDMOS becomes important. In literature, there have been few detailed studies on modeling capacitances in devices such as LDMOS and SOI-LDMOS and some of them have resulted in model development[1],[24],[25],[26]. One of the basic principles used for modeling capacitances is charge partitioning. The charges are modeled accurately and then they are partitioned between different terminals of the device based on Ward-Dutton partition principle[27]. MM20 model uses a modified version of Ward-Dutton model to obtain various capacitances. It does not clearly explain the basis behind such a partition and charge modeling also has some inherent approximations. Also, the match obtained between the device and model simulations are not satisfactory.

Therefore, there is a need for a comprehensive charge model which accounts for aforementioned effects. An attempt was made to modify the MM20 charge partitioning scheme by [31]. But, several inaccuracies in the charge model was reported. In this thesis, an extensive model to describe the static and dynamic characteristics of SOI-LDMOS is proposed. MM20 model and the model proposed by [31] serves as a starting point for describing various currents and charges in the device, but the model description goes a long way from these approaches. The model considers field dependent mobility reduction, velocity saturation in channel and quasi-saturation in the drift region. A new charge partitioning scheme is proposed and physical reasoning behind such a partition is explained.

#### 1.3 Objectives

The main objectives of this thesis are as follows.

- To analyze the behavior of SOI-LDMOS in channel, drift region under gate oxide and drift region under field oxide for various gate and drain bias voltages.

- To develop a scalable quasi-saturation model for the drift region under the field oxide which accounts for the bias dependence of the quasi-saturation current.

- To analyze the charges present in the device and provide a physics based charge-partition model to partition charges between various terminals.

• To predict various capacitances from the developed charge model.

#### 1.4 Structure of the thesis

The thesis is organized as follows.

#### • Chapter 2: Analysis of physical effects

A physical description of the working of LDMOS device is provided in this section. This is done by analyzing the internal node voltages to arrive at a typical output characteristic of an SOI-LDMOS. Further, various charges present in the operation of the SOI-LDMOS are pointed out along with a crude charge assignment scheme. The device behavior is analyzed with the help of a physics-based device simulator - MEDICI.

#### • Chapter 3: Model and Verilog-A implementation

In this chapter, first, a compact DC model to explain the observed physical effects is proposed. The model uses MM20 model for channel and drift region under gate oxide and a new quasi-saturation model is developed to capture the bias dependence of the quasi-saturation current and to account for scalability of region-III length. Later, a comprehensive charge model is proposed, based on a modified Ward-Dutton charge partitioning scheme.

#### • Chapter 4: Results and discussions

Static output characteristics, various capacitance plots and transient plots are compared with MEDICI simulation results.

#### • Chapter 5: Conclusions

Contributions offered by with work are presented. Scope for future work is listed.

## Chapter 2

## Analysis of Physical Effects

In this chapter, we focus on the physical effects which gives rise to unique AC and DC output characteristics of an SOI-LDMOS transistor. Firstly, the effect of gate and drain voltage on static currents is analyzed. A particular focus is laid on the effects caused my the presence of the drift region of the transistor. Next, we study various charges that arises in an SOI-LDMOS transistor with application of a gate and a drain bias. A 2-D device simulator Taurus MEDICI [28] is used for studying these effects.

#### 2.1 Device Structure

SOI-LDMOS transistor is an asymetric device which is constructed by adding an additional resistive drift region to a conventional MOSFET structure. The schematic cross-section of the device is as shown in Fig. 2.1. The channel region is self aligned to the gate and is formed by p-diffusion through the source opening. This creates a p-well structure under the gate, although it has a non-uniform doping profile; the source end of the channel has a higher doping concentration under he gate. Once the p-well for the channel is created, the source contact is formed by an n+ diffusion through the same opening. Since there are two lateral diffusions processes, this device is called as the lateral double-diffused MOSFET. The n-drift region sustains the reverse voltage applied at the drain end, and hence is lightly doped in comparison to the channel. Thus, the depletion region at

FIGURE 2.1: Schematic cross-section of the investigated SOI-LDMOS transistor.

the junction of the channel and the drift region extends mostly into the drift region. The gate electrode covers the surface of the drift region and a part of the drift region. The gate oxide and the field oxide are of different thicknesses. A thicker field oxide helps in reducing the gate drain overlap capacitance, and hence improving the speed of the device. The active part of the device is isolated from the bulk by a thick buried oxide which reduces parasitics.

As seen in Fig 2.1, the LDMOS transistor is divided into three important regions (denoted by region, region-II and region-III, corresponding to channel region in the p-well, drift region under the gate oxide and the drift region under the field oxide, respectively). The transition between region-I and region-Ii ids denoted by  $D_i$  and that between region -II and region-III is denoted by D'. While modeling the LDMOS structure, we analyze these three regions separately to obtain current and charge expressions for each of these regions.

The non-uniformity of the the doping concentration from the source to the drain side poses complexities in modeling the current and the associated charges. Hence, as a simplifying assumption, the channel doping is maintained constant in further formalisms and simulations. For the device under discussion, the p-well (region-I) has a uniform doping concentration of  $2 \times 10^{17} \text{cm}^{-3}$ , the drift region (region-II and region-III) has a doping concentration of  $2 \times 10^{16} \text{cm}^{-3}$  (ten times lower than

channel doping). A contact doping of  $1 \times 10^{20} \mathrm{cm}^{-3}$  is used for (n+) source and (n+) drain contacts (the same doping is assumed for the gate polysilicon) and  $5 \times 10^{21} \mathrm{cm}^{-3}$  is used for the (p+) bulk contact. The length of the channel region (region-I)  $L_{ch} = 0.825 \mu \mathrm{m}$  and the length of the drift region under the gate oxide (region-II)  $L_{dr} = 2.25 \mu \mathrm{m}$ . The default length for the drift region under the field oxide (region-III) is  $L_{dr1} = 3.45 \mu \mathrm{m}$ , unless explicitly stated. The gate oxide and field oxide thickness are 38nm and 100nm respectively. The thickness of the active region is  $1 \mu \mathrm{m}$  and the thickness of the buried oxide used is  $1 \mu \mathrm{m}$ .

#### 2.2 Static Currents

To make the analysis of the LDMOS transistor simple, we separate the device into three distinct regions: region-I, II and III. Although this is not a physical separation, this helps to analyze the effects and model the device using a simple approach. All throughout the charge and current analysis, it is assumed that the source and bulk terminals are shorted. As a result, in this thesis, we use the notations  $V_{GB}$  and  $V_{GS}$ ,  $V_{DB}$  and  $V_{DS}$  interchangeably<sup>1</sup>. Current modeling has been dealt with in great detail in [29] and [30]. As far as the DC static current model is concerned, this thesis tries to explain the current modeling carried out by [29, 30] in a concise form, with more focus laid on analyzing the scaling the length of region-III.

As  $V_{GS}$  is increased beyond the threshold voltage<sup>2</sup> of the channel, the region-I gets inverted, allowing conduction between the source and the drain, just as in the case of a MOSFET. However, since there is a gate overlap in the drift region (region-II), accumulation layer of electrons is formed (if sufficiently high gate voltage is applied). Hence conduction in region-II comprises of two components: conduction due to accumulation layer charge and the bulk conduction. Further, region-III can enter velocity saturation for sufficiently high drain and gate voltages. These effects manifest in the output characteristics as shown in Fig. 2.2.

<sup>&</sup>lt;sup>1</sup>It is possible to easily extend the analysis for a case in which  $V_{SB} \neq 0$

<sup>&</sup>lt;sup>2</sup>The threshold voltage of the channel is assumed to be a constant throughout the channel. However, if we take into account the non-uniformity in the p-well doping caused because of fabrication related issues, the threshold voltage varies across the channel.

Figure 2.2:  $I_D - V_{DS}$  characteristics for  $V_{GS} = 5, 10, 15$  and 20V, simulated in MEDICI

#### 2.2.1 Analysis of potential drops across the three regions

For easier understanding of the behavior of the LDMOS transistor under different bias voltages, we need to understand the variation of intermediate voltages at  $D_i$  and D' as a function of terminal voltages. A detailed account of this analysis can be found in [30]. Only a brief summary is dealt with in this thesis.

For a low value of  $V_{GS}$ , the conductivity of region-I and II is lesser than or comparable to that of that of the drift region. Hence, a significant portion of the applied drain voltage gets dropped across region-I and II. Hence, as  $V_{DS}$  is increased, at low  $V_{DS}$ , the current saturation is caused because region-I and II enter velocity saturation or pinch-off.

For a high value of  $V_{GS}$ , the conductivity of region-I and region-II are much greater than that of region-III. Hence, most of the applied voltage is dropped across region-III. For a sufficiently high value of  $V_{DS}$ , the region-III enters velocity saturation and causes a current saturation. This kind of current saturation caused because region-III enters velocity saturation is referred to as the *quasi-saturation*. Due to quasi-saturation at high  $V_{GS}$ , the drain current almost becomes independent of the gate voltage<sup>3</sup>.

<sup>&</sup>lt;sup>3</sup>There is a small dependence of the quasi-saturation current on the gate voltage (as we shall see later), but this is a second-order effect.

FIGURE 2.3: Schematic cross-section of the 2-D resistor structure simulated to model the velocity saturation characteristics.

#### 2.2.2 Gate and drain voltage dependence of the quasisaturation current.

For a sufficiently high value of  $V_{GS}$ , since both region-I and II have high conductivity, almost all the applied voltage is dropped across region-III. Hence, region-III is expected to enter velocity saturation as  $V_{DS}$  is increased. The velocity saturation current of a resistor is not expected to depend on the applied voltage across it. Further, since the gate voltage does not affect the performance of region-III, we do not expect  $V_{GS}$  dependence of the drain current.

Contrary to our expectations, the quasi-saturation current shows both drain and gate voltage dependence as shown in Fig. 2.2.

#### 2.2.2.1 Drain voltage dependence

To understand the drain voltage dependence of the quasi-saturation current, let us first analyze a simple two-dimensional SOI-resistor shown in Fig. 2.3. Even in a case of a simple two-dimensional SOI-resistor, the velocity saturated drain current is not independent of the applied voltage; there is a mild increase in the velocity saturated current with increase in the applied voltage. Further, this rate of this increase in drain current increases with decrease in the length of the 2-D resistor.

FIGURE 2.4: Variation of charge carrier concentration as a function of voltage across the resistor. The  $n_{eff}$  data from MEDICI is probed at  $t_{si}/2$  below the top oxide-silicon interface.

This increase was said to be due to channel length modulation by [29]. But, as pointed out in [17], this parameter should be attributed to the increase in charge carrier concentration once velocity saturation condition is reached and not to the channel length modulation. This increase is caused by the presence of highly doped contacts and the 2-D geometry of the resistor. Fig. 2.4 shows that the electron concentration  $(n_{eff})$  at different locations of the resistor starts to increase after different  $V_{DD'}$  values. Threshold  $V_{DD'}$  values are much lower near the metal contacts.

#### 2.2.2.2 Gate voltage dependence

A plot of the net electron density along the top oxide-semiconductor surface of the device in 2.1. Fig.2.5 shows the simulated electron density for different values of  $V_{GS}$  and at high  $V_{DS}(=20V)$ . We observe that there is some amount of spill over of the electron concentration into region-III from region-II, which has very high electron concentration due to accumulation condition at the surface. As the gate to D' voltage  $(V_{GD'})$  is increased, the accumulation charge at D' increases and consequently the spill over of the electron concentration increases leading to a reduction in the effective length of region-III. This reduction of the effective length with increase in  $V_{GS}$  causes the increase in drain current with increase in  $V_{GD'}$ .

FIGURE 2.5: Net electron density (obtained from MEDICI) as a function of x along the top oxide-semiconductor surface of the device for  $V_{GS} = 5, 10, 15, 20V$ . The vertical dashed line represents the D' node shown in Fig. 2.1

#### 2.3 Regional Charge assignments

In this thesis, we are trying to carry out the AC model using a charge based approach for all bias voltages (negative and positive). Hence, a proper understanding of various charges present in the device is needed. Also, the identified charges need to be assigned to various terminals so that the associated capacitance of each terminal can be derived from the charges by using:

$$C_{ij} = (2\delta_{ij} - 1)\frac{\partial Q_i}{\partial V_i} \tag{2.1}$$

where  $i, j \in D, G, S, B$  and  $\delta_{ij}$  is the Kronecker delta function.

Fig. 2.6 shows various charges associated with the LDMOS structure for different representative bias points. To systematically analyze the various charges that one needs to account for while modeling these charges, let us look at various charges present in the device region wise.

#### 2.3.1 Region-I surface charges

The region-I analysis of charges is similar to that of a regular MOSFET. When  $V_{GS} < V_{FB,ch}$ , where  $V_{FB,ch}$  is the flat band voltage of region-I, the surface of region-I enters accumulation mode of operation. A accumulation layer of holes

FIGURE 2.6: Cross-section of the SOI-LDMOS transistor indicating the depletion region and other associated charges at various bias points

is formed along the surface of region-I. These accumulation charges (holes) are assigned to the bulk of the device (p doped) where the majority carriers are holes.

For  $V_{GS} > V_{FB,ch}$ , depletion and inversion layer charges are formed along the surface. The depletion layer charges is again associated with the bulk of the device. The inversion layer charge (formed by electrons) on the other hand is associated with S and  $D_i$  nodes (n doped). One needs to model the split of charges between the source and the drain terminal. This model is referred to as a 'charge partitioning scheme' in the literature.

#### 2.3.2 Region-II surface charges

When the LDMOS transistor is biased such that  $V_{GDi} > V_{FB,dr}$ , where  $V_{FB,dr}$  is the flat band voltage of region-II, the surface of region-II is in accumulation mode. This accumulation charges (electrons) must come from a n doped region. Hence, the charges need to be partitioned between the  $D_i$  and the D' nodes (n doped).

For  $V_{GDi} < V_{FB,dr}$ , region-II enters depletion and inversion modes. Similar to the case when the source and the drain (n-doped) regions give rise to the electron inversion charge in region-I (p-doped), when region-II (n-doped) is biased in inversion, the hole inversion layer charge should come from the bulk (p-doped) of the transistor. Hence the hole charge associated with region-II comes from the bulk. Further, The depletion layer charge in the drift region needs to be assigned to  $D_i$  and D' nodes of the device, just as the case where the depletion layer charge in region-I is assigned to the bulk.

#### 2.3.3 p-n junction charges

Apart from surface charges caused due to MOS capacitor action, region I and II have yet another source of charge: the depletion region caused due to the reverse biased p-n junctions present between region-I and II and between the source and region-I. These depletion layer charge assignments is similar to that of MOS capacitor depletion layer charge assignment. The depletion charges present

Table 2.1: Charge assignment to various terminals

|                     | Region-I      | Region-II      |

|---------------------|---------------|----------------|

| Accumulation charge | B             | $D_i$ and $D'$ |

| Depletion charge    | B             | $D_i$ and $D'$ |

| Inversion charge    | $S$ and $D_i$ | B              |

on the region-I side is assigned to the bulk of the device, on the region-II side is assigned to the  $D_i$  node<sup>4</sup> and on the source side is assigned to the source terminal.

#### 2.3.4 Region-III charges

The only charge variation in region-III of the LDMOS transistor is caused due to the increase in  $n_{eff}$  as seen in Fig. 2.4. This increase in effective carrier concentration is insignificant compared to the magnitude of charge variation caused due to other sources. Hence, these charges are neglected while modeling the charges,

The summary of charge assignment to various terminals can be seen in Table 2.1. Apart from the charges mentioned in Table. 2.1, the reverse biased p-n junction charges also need to be taken into account as discussed.

<sup>&</sup>lt;sup>4</sup>In principle, this depletion charges too need to be partitioned between the D' and the  $D_i$  nodes. However, we encounter a few technical issues if done so. These will be dealt in the later chapters.

## Chapter 3

# Model and Verilog-A implementation

A comprehensive model for any device must be capable of predicting the device performance over a wide range of biases, temperatures and device geometries. Since SOI-LDMOS forms an integral part of HVICs, accurate modeling of these devices is necessary to ensure fail-safe design of HVIC circuits.

Any good LDMOS model must have the following features:

- Accurate modeling of AC/DC terminal currents and the nodal charges in linear, saturation and off modes.

- Continuity of device models in different regions and continuity in their derivatives and double derivatives.

- Conservative nature of charge model.

- Accurate modeling of capacitances to predict the dynamic behavior of the device.

- Modeling high frequency behavior where device operates in Non-Quasi static regime.

- Capability to model impact ionization and snapback and in turn predict SOA.

FIGURE 3.1: EC Model for static MOSFET currents.

- Capability to model self heating which requires temperature dependence of model parameters.

- Modeling various types of noise i.e. 1/f noise, thermal noise etc.

- Scalability of the model over wide range of bias, geometries and temperatures.

Extensive work has been carried out by [29] in developing a DC model for low bias voltages. [30] extends this model to incorporate various high bias effects like snapback, self-heating and impact-ionization. An charge-partition based AC model is proposed by [31]. In this chapter, a summary of the models proposed by [29–31] is investigated, along with incorporating many changes in both the AC and DC models. The model proposed provides an improvement over one of the currently existing industrial standard compact models: the MM20 model [1, 2, 21].

#### 3.1 Static current model

For the ease of modeling, the LDMOS transistor is divided into three regions - region-I, II and III. For all the analysis to follow, we shall look at these three regions separately and develop compact models for these three regions individually. The LDMOS transistor model is modeled using three current sources [29, 30] as shown in Fig. 3.1. Here  $I_{ch}$  is the channel current which is a function of the potential drop across region-I  $(V_{DiS})$ . The potential drop across region-II is given by  $V_{D'Di}$  and it determines the current flowing through region-II, given by  $I_{dr}$ . The current through region-III is  $I_{dr1}$  and it is a function of the potential drop across region-III, given by  $V_{DD'}$ . The current source models are explained in the following subsections.

#### 3.1.1 Formulation of current in channel region

Channel current is modeled using a surface potential approach. The current  $I_{ch}$  through the channel is obtained by adding the drift and the diffusion components of the current, i.e.,

$$I_{ch} = \frac{W\mu_{ch}}{L_{ch}} \left( \int_{\psi_{s,0}^{ch}}^{\psi_{s,L}^{ch}} \left( -Q_{inv}^{ch} \right) d\psi_s^{ch} + V_T \left( Q_{inv,L}^{ch} - Q_{inv,0}^{ch} \right) \right)$$

(3.1)

where W is the channel width,  $\mu_{ch}$  is the channel mobility taking into account the effect of lateral and vertical electric fields.  $L_{ch}$  is the channel length,  $\psi_s^{ch}$  is the surface potential,  $V_T$  is the thermal voltage and  $Q_{inv}^{ch}$  is the inversion charge per unit area given as  $Q_{inv}^{ch} = -C_{ox}V_{inv}$  with  $Q_{inv,0}^{ch}$  and  $Q_{inv,L}^{ch}$  being the inversion charges at the source and the drain  $(D_i)$  terminals. Inversion potential  $V_{inv}$  is given by

$$V_{inv} = V_{GB} - V_{FB,ch} - \psi_s^{ch} - k_{ch} \sqrt{\psi_s^{ch}}$$

(3.2)

where  $V_{GB}$  is the applied gate to bulk voltage,  $V_{FB,ch}$  is the flatband voltage of the channel region and  $k_{ch}$  is the channel body effect coefficient. On linearizing  $V_{inv}$  with respect to the source surface potential  $\psi_{s,0}^{ch}$ , we get

$$V_{inv} = V_{inv,0} - \zeta \left( \psi_s^{ch} - \psi_{s,0}^{ch} \right) \tag{3.3}$$

with  $\zeta = \left(1 + \frac{k_{ch}}{2\sqrt{\psi_{s,0}^{ch}}}\right)^1$  and the inversion potential on the source side is given by

$$V_{inv,0} = V_{inv} \mid_{\psi_{s}^{ch} = \psi_{s,0}^{ch}} = V_{GB} - V_{FB,ch} - \psi_{s,0}^{ch} - k_{ch} \sqrt{\psi_{s,0}^{ch}}$$

(3.4)

Using (3.2), (3.3) and (3.4), (3.1) can be simplified as

$$I_{ch} = \frac{W\mu_{ch}C_{ox}}{L_{ch}} \left( V_{inv,0} - \frac{1}{2}\zeta\Delta\psi_s^{ch} + \zeta V_T \right) \Delta\psi_s^{ch}$$

(3.5)

take a zero value. Of course, this can be completely avoided by not linearizing  $V_{inv}$ . But that will add just on to the complexity of the model.

<sup>&</sup>lt;sup>1</sup>This linearization becomes invalid around  $\psi_{s,0}^{ch}=0$  as  $\zeta$  blows up. To avoid this condition, we use  $\zeta=\left(1+\frac{k_{ch}}{2\sqrt{\psi_{s,0}^{ch}+\delta}}\right)$ , where  $\delta$  is a small increment, sufficiently to never allow  $\psi_{s,0}^{ch}$  to

where  $\Delta \psi_s^{ch} = \psi_{s,L}^{ch} - \psi_{s,0}^{ch}$ ,  $\psi_{s,0}^{ch}$  and  $\psi_{s,L}^{ch}$  are the surface potential at S and  $D_i$  nodes respectively. Mobility reduction due to lateral fields which accounts for velocity saturation is given by

$$\mu_{ch} = \frac{\mu_{eff,ch}}{1 + \theta_{3,ch} \Delta \psi_s^{ch}} \tag{3.6}$$

where  $\theta_{3,ch} = \frac{\mu_{0,ch}}{L_{ch}v_{sat}^{ch}}$  is the parameter that takes care of velocity saturation in the channel, where  $\mu_{0,ch}$  is the zero field channel mobility and  $v_{sat}^{ch}$  is the saturation velocity in channel.  $\mu_{eff,ch}$  accounts for mobility reduction due to the vertical field and is given by

$$\mu_{eff,ch} = \frac{\mu_{0,ch}}{\left(1 + \theta_1 V_{inv,0} + \theta_2 \left(\sqrt{\psi_{s,0}^{ch}} - \sqrt{\psi_{s,0}^{ch}} \mid_{V_{SB}=0}\right)\right)}$$

(3.7)

where  $\theta_1$  and  $\theta_2$  are model parameters. Further, if we incorporate the channel length modulation effects, the expression for channel current becomes

$$I_{ch} = \left(1 + \lambda_{ch} V_{DiS}\right) \frac{W \mu_{ch} C_{ox}}{L_{ch}} \left(V_{inv,0} - \frac{1}{2} \zeta \Delta \psi_s^{ch} + \zeta V_T\right) \Delta \psi_s^{ch}$$

(3.8)

where  $\lambda_{ch}$  is the channel modulation parameter. The surface potentials at the source and the  $D_i$  nodes are computed following the approach of [32]. The surface potential at the source and  $D_i$  nodes can be written as

$$\psi_{s,0}^{ch} = \psi \left[ V_{GB} - V_{FB,ch}, V_{SB}, k_{ch} \right]$$

$$\psi_{s,L_{ch}}^{ch} = \psi \left[ V_{GB} - V_{FB,ch}, V_{DiB}, k_{ch} \right].$$

(3.9)

#### 3.1.2 Formulation of current under gate oxide

The drift current formulation is done in terms of the Quasi-Fermi potential as opposed to the surface potential formulation for the channel current. The current in region-II is a combination of two currents: The surface current caused due to the presence of accumulation charges and the bulk current due to the presence of the n doped drift region. Hence, the current equations can be written as

$$I_{dr} = \frac{W\mu_{dr}}{L_{dr}} \int_{V_{D_i}}^{V_{D'}} \left(-Q_{acc}^{dr}\right) dV_c + \frac{qW\mu_{0,dr}N_{dr}t_{si}}{L_{dr}} V_{D'D_i}$$

(3.10)

where  $V_c$  represents the quasi-Fermi level along the top oxide semiconductor interface,  $Q_{acc}^{dr}$  represents accumulation charge per unit area, W is the drift region width  $L_{dr}$  is the drift region length,  $\mu_{dr}$  is region-II mobility taking into effect of mobility reduction due to lateral and vertical electric fields,  $\mu_{0,dr}$  is the low field mobility,  $V_{D'D_i}$  is the voltage across region-II,  $t_{si}$  is the thickness of the active layer above the buried oxide and q is the electronic charge. The first term of (3.10) refers to the surface current and the second term estimates the bulk current<sup>2</sup>. Note that a one-dimensional analysis is carried out in estimating the region-II current<sup>3</sup>.

The surface conduction happens only along the accumulation layer formed along the surface of region-II. This accumulation layer charge can be approximated using

$$Q_{acc}^{dr} = -C_{ox} \left( V_{GC} - V_{FB,dr} - \psi_s^{dr} \right). \tag{3.11}$$

When  $V_{GC} > V_{FB,dr}$ , accumulation layer will be formed and depletion charge is negligible. Also, under accumulation condition, most of the voltage drop occurs across the gate oxide and value of surface potential is negligible. Hence, one can rewrite (3.11) as

$$Q_{acc}^{dr} = -C_{ox} \left( V_{GC} - V_{FB,dr} \right). {3.12}$$

Following the same approach as previous section, one can linearize the above charge with respect to the terminal  $D_i$ . If we consider  $V_n^{dr} = -Q_{acc}^{dr}/C_{ox}$ , then one can write  $V_n^{dr}$  as

$$V_n^{dr} = V_n^{dr} \mid_{V_c = V_{D_i}} - (V_c - V_{D_i})$$

(3.13)

The mobility reduction due to lateral and perpendicular fields is modeled similar to the channel region as follows

$$\mu_{dr} = \frac{\mu_{eff,dr}}{\left(1 + \theta_{3,dr} V_{D'D_i}\right)} \tag{3.14}$$

where  $\theta_{3,dr} = \frac{\mu_{0,dr}}{L_{dr}v_{sat}^{dr}}$  is the parameter that takes into account velocity saturation in region-II, with  $v_{sat}^{dr}$  being the saturation velocity of region-II surface and  $\mu_{0,dr}$

<sup>&</sup>lt;sup>2</sup>The actual bulk current should be estimated by subtracting the depletion regions caused due to the presence of the p-n junction and the gate. However, it is seen that the above expression is a good enough approximation and removing the depletion layer charge does not cause significant improvement in the model.

<sup>&</sup>lt;sup>3</sup>This is a major drawback of this formulation, as we shall see in Chapter 4

being the low-field mobility.  $\mu_{eff,dr}$  account for the mobility reduction due to vertical field and is given by

$$\mu_{eff,dr} = \frac{\mu_{0,dr}}{\left(1 + \theta_{acc} \left(0.5 V_{GD_i} + 0.5 V_{GD'} - V_{FB,dr}\right)\right)}$$

(3.15)

where  $\theta_{acc}$  is a model parameter. Substituting (3.13, 3.15) in (3.10) gives region-II current as

$$I_{dr} = \frac{W\mu_{dr}C_{ox}}{L_{dr}} \left( V_n^{dr} \mid_{V_c = V_{D_i}} -0.5V_{D'D_i} \right) V_{D'D_i} + \frac{qW\mu_{0,dr}N_{dr}t_{si}}{L_{dr}} V_{D'D_i}.$$

(3.16)

This model is only till the onset of saturation. To model saturation, one must compute the saturation potential by forcing  $\frac{\partial I_{acc}}{\partial V_{D'D_i}} |_{V_{D'D_i}=V_{sat,dr}} = 0$ , where  $I_{acc}$  is the accumulation current of in region-II given by the first term of (3.16). This gives the region-II saturation potential as

$$V_{sat,dr} = \frac{2V_n^{dr} \mid_{V_c = V_{D_i}}}{1 + \sqrt{1 + 2\theta_{3,dr} V_n^{dr} \mid_{V_c = V_{D_i}}}}.$$

(3.17)

The final expression for region-II is given by

$$I_{dr} = \frac{W\mu_{eff,dr}C_{ox}}{L_{dr}} \frac{\left(V_n^{dr} \mid_{V_c = V_{D_i}} - 0.5V_{D'D_{i,eff}}\right)V_{D'D_{i,eff}}}{\left(1 + \theta_{3,dr}V_{D'D_{i,eff}}\right)} + \frac{qW\mu_{0,dr}N_{dr}t_{si}}{L_{dr}}V_{D'D_i}.$$

(3.18)

where  $V_{D'D_i,eff}$  is the effective potential drop across region-II which is the minimum of  $V_{D'D_i}$  and  $V_{sat,dr}$ . The transition from linear region to the saturation region is made differentiable by using appropriate smoothing function.

#### 3.1.3 Formulation of current under field oxide

#### 3.1.3.1 2-D resistor under velocity saturation

The drift region under the field oxide could be modeled as a conventional resistor incorporating velocity saturation effects. Using a conventional velocity saturation

model [33], the current I though the 1-D semiconductor block is given by

$$I = q\mu N_{dr1} t_{si} W E_{eff},$$

$$\mu = \frac{\mu_{dr1}}{\left(1 + \left(E_{eff}/E_{C}\right)^{\theta_{dr1}}\right)^{1/\theta_{dr1}}},$$

$$E_{eff} = V_{DD'}/L_{LC},$$

$$E_{C} = v_{sat}/\mu_{dr1},$$

(3.19)

where q is the electronic charge,  $N_{dr1}$  is the doping concentration,  $t_{si}$ , W and  $L_{LC}$  are the thickness, width and length of the resistor, respectively,  $\mu_{dr1}$  is the low field mobility,  $v_{sat}$  is the saturation velocity,  $\theta_{dr1}$  is a model parameter and  $V_{DD'}$  is the voltage applied across the resistor. For a large value of  $V_{DD'}$ , when  $E_{eff} \gg E_C$ , it can be shown that I saturates due to velocity saturation and becomes independent of  $V_{DD'}$ .

However, in the case of a 2-D SOI resistor (Fig. 2.3), it is observed that the current increases even after the velocity saturation condition is reached, due to the increase in carrier concentration. This is usually taken care by using a linear correction parameter  $\lambda_{dr1}$  [29] as

$$I' = I(1 + \lambda_{dr1} V_{DD'}), \tag{3.20}$$

where I is given by (3.19). As discussed in Chapter 2, the carrier concentration increase is not strictly linear. There exists threshold values of  $V_{DD'}$  beyond which carrier concentration  $n_{eff}$  increases. However, as seen in Fig. 2.4, there is no unique threshold value of  $V_{DD'}$  beyond which the carrier concentration increases. Further, if a single threshold is considered, as in [17], we found that the model is inaccurate for lower resistor lengths. Hence, considering the average effect of  $n_{eff}$  increase at different locations (Fig. 2.4), the  $n_{eff}$  is modeled to increase linearly with  $V_{DD'}$ .

Further, numerical simulations show that  $\lambda_{dr1}$  depends on the length of the resistor. To analyze this dependence, the slope of the I- $V_{DD'}$  characteristics (i.e.  $\lambda_{dr1}$ ) for different  $L_{LC}$  values are calculated from numerically simulated data at high  $V_{DD'}(=20V)$ . It is seen that the variation of  $\lambda_{dr1}$  with respect to  $L_{LC}$  follows an

FIGURE 3.2: Inverse square law behaviour (as described in (3.21)) of  $\lambda_{dr1}$  at high  $V_{DD'}(=20V)$ .

inverse square law, as shown in Fig. 3.2, given by

$$\lambda_{dr1} = \lambda_{VD} / L_{LC,eff}^2, \tag{3.21}$$

where  $L_{LC,eff} = L_{LC} - \Delta L_{LC}$  represents the effective length of the resistor taking into account the 2-D current flow, and  $\lambda_{VD}$  and  $\Delta L_{LC}$  are model parameters independent of length of the resistor.

Hence, the 2-D resistor, including velocity saturation effects, can be modeled as

$$I = q\mu_{eff}n_{eff}t_{si}WE_{eff},$$

$$\mu_{eff} = \frac{\mu_{dr1}}{\left(1 + \left(E_{eff}/E_{C}\right)^{\theta_{dr1}}\right)^{1/\theta_{dr1}}},$$

$$n_{eff} = N_{dr1}\left(1 + \left(\lambda_{Vd}/L_{LC,eff}^{2}\right)V_{DD'}\right),$$

$$E_{eff} = V_{DD'}/L_{LC,eff},$$

$$E_{C} = v_{sat}/\mu_{dr1}.$$

#### 3.1.3.2 Modeling the Gate voltage dependence

When an LDMOS transistor is subject to sufficiently high gate and drain voltages, the drain current is controlled by the velocity saturation current of region-III, and the transistor is said to be in quasi-saturation regime of operation. Under such operating conditions, one would expect that the gate voltage does not affect the region-III performance, and hence the drain current becomes independent of gate

voltage. However, the device simulation data indicates that the drain current continues to increase with increasing gate voltage. This effect has been modeled previously by a linear correction term [16], but the source of the effect has not been well studied. Further, the scalability of this effect for varying drift region lengths has not been demonstrated.

As discussed in Chapter 2, the gate voltage dependence is caused due to change in region-III length due to the carrier spill over effect.

This control of effective region-III length by the gate voltage can be modeled by a linear approximation, i.e.,

$$L'_{LC,eff} = L_{LC,eff}(1 - \lambda_{VG}V_{GD'}), \qquad (3.22)$$

where  $\lambda_{VG}(=\Delta L_{LC,VG}/L_{LC,eff})$  is the region-III length modulation factor (which is the fractional change in the drift region length for a unit change in  $V_{GD'}$ ),  $\Delta L_{LC,VG}$  is the change in region-III length for a unit change in  $V_{GD'}$  and is independent of region-III length. The parameter  $\Delta L_{LC,VG}$  used in the model is obtained from measuring the change in the effective region-III length from Fig. 2.5.

#### 3.1.3.3 Region-III model

The final model for region-III of the SOI-LDMOS transistor, taking into account the 2-D velocity saturation effects, can be written as

$$I_{dr1} = \frac{q n_{eff} \mu_{eff} V_{DD'} W t_{si}}{L_{LC,eff} (1 - \lambda_{VG} V_{GD'})},$$

$$\mu_{eff} = \frac{\mu_{dr1}}{\left(1 + \left(E_{eff}/E_{C}\right)^{\theta_{dr1}}\right)^{1/\theta_{dr1}}},$$

$$n_{eff} = N_{dr1} (1 + \lambda_{dr1} V_{DD'}), \quad L_{LC,eff} = L_{LC} - \Delta L_{LC},$$

$$E_{eff} = V_{DD'}/L_{LC,eff}, \qquad E_{C} = v_{sat}/\mu_{dr1},$$

$$\lambda_{dr1} = \lambda_{VD}/L_{LC,eff}^{2}, \qquad \lambda_{VG} = \Delta L_{LC,VG}/L_{LC,eff}.$$

(3.23)

Here, the model parameters  $\Delta L_{LC}$ ,  $\Delta L_{LC,VG}$ ,  $\lambda_{Vd}$ ,  $\mu_{dr1}$ ,  $\theta_{dr1}$  and  $v_{sat}$  are invariant under any change in the region-III length.

# 3.2 Charge Model

In this thesis, the transient and AC analysis is carried out using a charge based modeling approach. This means that we need to assign charges to various nodes accurately. Once the charges are assigned accurately to each node, the corresponding time derivative gives the transient current through that node.

Charge modeling of an LDMOS transistor has been dealt with in great detail in [31]. However, there were several reported inaccuracies in the model in [31]. This was especially true in the negative  $V_{GS}$  regime where the accumulation charge in region-I and inversion charge in region-II were incorrectly assigned. Further, the p-n junction charges present due to the region-I and II reverse biased junction were not accounted for. In this section, a new accurate description of the charge model is proposed.

Table 2.1 gives the charge assignment of various kinds of charges in an SOI-LDMOS transistor. The accumulation charges in region-II and the inversion layer charges in region-I needs to be split between the S,  $D_i$  and D' nodes.

### 3.2.1 The MM20 approach

The MM20 model, which is taken as the base case for our model, uses a Modified Ward-Dutton partitioning scheme (MWD scheme) to achieve this split of charges. The MM20 group published two papers [1] and [2] where they seemingly advocated two different models for charge partitioning. In this section, we shall have a look at these two models individually and show the equivalence between the formulations in these two works.

#### 3.2.1.1 Model proposed by [1]

The following is the summary of the model proposed by [1]. This nodal charge model has four nodes: gate (G), drain (D), source (S) and bulk (B). Region-III is elimated from the discussion of charge model, as it is modeled as a voltage dependent resistor, void of any capacitive effects. Further, this model lifts the necessity of using an internal node  $(D_i)$ , which forms the distinction between region-I and region-II, by carefully handling the charge partitioning at the source and drain terminals. The source terminal is the reference node, and the charge at this terminal  $Q_S$  is computed by the conservation of charge, given by:

$$Q_S = -(Q_G + Q_B + Q_D) (3.24)$$

where  $Q_G$ ,  $Q_B$  and  $Q_D$  represents the gate, bulk and drain charges respectively.

The total gate charge is given by adding the channel region (region-I) contribution  $(Q_G^{ch})$  and the drift region (region-II) contribution  $(Q_G^{dr})$ , i.e.,  $Q_G = Q_G^{ch} + Q_G^{dr}$ , where

$$Q_G^{ch} = -W \int_0^L (Q_{acc}^{ch} + Q_{dep}^{ch} + Q_{inv}^{ch}) dx,$$

$$Q_G^{dr} = -W \int_L^{L+L_D} (Q_{acc}^{dr} + Q_{dep}^{dr} + Q_{inv}^{dr}) dx.$$

(3.25)

Here,  $Q_{acc}$  is the accumulation charge density,  $Q_{inv}$  is the inversion layer charge density and  $Q_{dep}$  is the depletion layer charge density. The superscripts ch and dr represents channel (region-I) and drift (region-II) regions respectively of the LDMOS transistor (the same convention has been adopted throughout).

The hole charge when Region-I is biased in accumulation  $(Q_{acc}^{ch})$  and the depletion layer charge  $(Q_{dep}^{ch})$  when biased in weak/strong inversion is attributed to the bulk terminal of the transistor. Further, similar to the case when the source and the drain (n-doped) regions give rise to the electron inversion charge in the channel (p-doped), when region-II (n-doped) is biased in inversion, the hole inversion layer charge  $(Q_{inv}^{dr})$  can be assumed to come from the bulk (p-doped) of the transistor.

Hence the total bulk  $Q_B = Q_B^{ch} + Q_B^{dr}$  is given by

$$Q_B^{ch} = -W \int_0^L (Q_{acc}^{ch} + Q_{dep}^{ch}) dx,$$

$$Q_B^{dr} = -W \int_L^{L+L_D} Q_{inv}^{dr} dx.$$

(3.26)

Now, all that is left is to assign charge to the drain terminal. According to [1], the charge assignment to the drain terminal is done in two different ways corresponding to the weak and the strong inversion conditions of region-I. This charge partitioning scheme is referred to as the MWD scheme.

Before jumping into the charge assignment equations proposed by [1], we shall understand the motivation behind the MWD source-drain charge partitioning.

- 1. The entire depletion layer charge  $Q_{dep,D}^{dr}$  that arises in region-II (during inversion) is attributed to the drain, just as bulk terminal gives rise to the depletion charge in region-I.

- 2. Following the usual WD partitioning scheme, we assign a part of the drift region accumulation charge  $Q_{acc,D}^{dr}$  to the drain terminal.

- 3. The other portion of the drift region accumulation charge  $Q_{acc,S}^{dr}$ , which is supposed to be assigned to the source, is further divided into two portions, and assigned to the source and the drain respectively. This split depends on how close the source terminal is to the boundary of region-II, and is decided by the factor  $F_L = L/(L + L_D)$ . The source terminal is attributed  $(1 F_L)Q_{acc,S}^{dr}$  and the drain terminal is assigned  $F_LQ_{acc,S}^{dr}$ . Observe that smaller the L with respect to  $L_D$ , larger (smaller) is the fraction of charge assigned to the source (drain).

- 4. A similar partitioning is done for the electron inversion layer in region-I. A part of the inversion layer charge  $Q_{inv,S}^{ch}$ , following the usual WD partitioning is assigned to the source. Again, the other portion which should be assigned to the drain is split into two parts, and assigned to the source  $((1-F_L)Q_{inv,D}^{ch})$  and the drain  $(F_LQ_{inv,D}^{ch})$  respectively, owing to the isolation of the drain terminal caused by the region-II.

FIGURE 3.3: Charge partitioning under strong (top) and weak (bottom) inversions of region-I.

The last three points are summarized in Figure 3.3, which shows the source-drain charge partitioning of inversion/accumulation layer charges. Hence, the charge attributed to the drain can be written as

$$Q_D = F_L Q_{inv,D}^{ch} + Q_{acc,D}^{dr} + F_L Q_{acc,S}^{dr} + Q_{dep,D}^{dr},$$

(3.27)

where

$$Q_{inv,D}^{ch} = W \int_0^L \frac{x}{L} Q_{inv}^{ch} dx,$$

$$Q_{acc,D}^{dr} = W \int_0^{L_D} \frac{\tilde{x}}{L_D} Q_{acc}^{dr} d\tilde{x},$$

$$Q_{acc,S}^{dr} = W \int_0^{L_D} \left(1 - \frac{\tilde{x}}{L_D}\right) Q_{acc}^{dr} d\tilde{x},$$

$$Q_{dep,D}^{dr} = W \int_0^{L_D} Q_{dep}^{dr} dx.$$

(3.28)

Here,  $\tilde{x} = x - L$ , a shifted co-ordinate system.

FIGURE 3.4: EC Model for static and dynamic and LDMOS transistor currents using MM20 formulation

In the case when region-I is in accumulation or weak inversion, all the accumulation charge of the drain region is attributed to the drain (refer Figure 3.3). The motivation behind doing such a charge assignment probably lies in the fact that the region-II is isolated from the source when the channel is in weak inversion, and hence the source terminal is not responsible for the electron accumulation charge in region-II. Therefore, the drain drift region charge is approximated as

$$Q_D = F_L Q_{inv,D}^{ch} + Q_{acc,D}^{dr} + Q_{acc,S}^{dr} + Q_{dep,D}^{dr}.$$

(3.29)

#### 3.2.1.2 Model proposed by [2]

Many features of charge partitioning model given by [2] similar to that of [1]. Only the aspects in which [2] is different from [1] is discussed here.

The reference terminal in this model, instead of the source, is the bulk terminal. Further, the charge partitioning equations appear differently as compared to [1]. The gate charge equation is same as that in (3.25). The charge at the drain and source terminal is assigned as

$$Q_D = Q_D^{ch} + Q_D^{dr}, \quad Q_S = Q_S^{ch} + Q_S^{dr}.$$

(3.30)

The channel contributions to the source and the drain charges are

$$Q_D^{ch} = W \int_0^L \frac{x}{L + L_D} Q_{inv}^{ch} dx,$$

$$Q_S^{ch} = W \int_0^L \left( 1 - \frac{x}{L + L_D} \right) Q_{inv}^{ch} dx,$$

(3.31)

The region-II contribution is, as carried out in [1], is considered in two cases. When region-I is in strong inversion, the source and drain contributions to drift region charge is given by

$$Q_D^{dr} = W \int_L^{L+L_D} \frac{x}{L+L_D} (Q_{acc}^{dr} + Q_{dep}^{dr}) dx,$$

$$Q_S^{dr} = W \int_L^{L+L_D} \left(1 - \frac{x}{L+L_D}\right) (Q_{acc}^{dr} + Q_{dep}^{dr}) dx.$$

(3.32)

and under weak inversion, the contribution to the drift charge is completely given to the drain region.

$$Q_D^{dr} = W \int_L^{L+L_D} (Q_{acc}^{dr} + Q_{dep}^{dr}) dx,$$

$$Q_S^{dr} = 0.$$

(3.33)

#### 3.2.1.3 A Comparative study

Although the models proposed by [1] and [2] seem vastly different, they can be shown to be equivalent. Consider, for instance, the drift region contribution to the drain charge when region-I is in strong inversion. When region-I is in strong inversion, region-II is likely to be in accumulation. This means that the region-II depletion layer charge  $Q_{dep}^{dr} = 0$ . Hence, according to [1],

$$\begin{split} Q_D &= F_L Q_{inv,D}^{ch} + Q_{acc,D}^{dr} + F_L Q_{acc,S}^{dr} \\ &= \frac{WL}{L + L_D} \int_0^L \frac{x}{L} Q_{inv}^{ch} dx + W \int_0^{L_D} \frac{\tilde{x}}{L_D} Q_{acc}^{dr} d\tilde{x} + \frac{WL}{L + L_D} \int_0^{L_D} \left(1 - \frac{\tilde{x}}{L_D}\right) Q_{acc}^{dr} d\tilde{x} \\ &= W \int_0^L \frac{x}{L + L_D} Q_{inv}^{ch} dx + W \int_0^{L_D} \left(\frac{\tilde{x}}{L_D}\right) \left(\frac{L_D - \tilde{x}}{L + L_D}\right) Q_{acc}^{dr} d\tilde{x} \\ &= W \int_0^L \frac{x}{L + L_D} Q_{inv}^{ch} dx + W \int_L^{L + L_D} \left(\frac{x - L}{L_D}\right) \left(\frac{L_D - (x - L)}{L + L_D}\right) Q_{acc}^{dr} dx \\ &= W \int_0^L \frac{x}{L + L_D} Q_{inv}^{ch} dx + W \int_L^{L + L_D} \frac{x}{L + L_D} Q_{acc}^{dr} dx, \end{split}$$

which is precisely the expression for charge partitioning in [2] for the drain terminal, when region-I is in strong inversion. A similar equivalence can be shown for the charge partitioning when region-I is in weak inversion, or in accumulation.

#### 3.2.1.4 EC Model for MM20 charge partitioning

Figure 3.4 shows the equivalent circuit model of MM20 model. The charges are assigned to four terminals, i.e., G, D', S and B. From each of these terminals the displacement current source dQ/dt is connected to the bulk terminal which is a reference. Due to the circuit topology and by charge conservation,  $dQ_B/dt$  is calculated automatically.

#### 3.2.2 A New Charge Partitioning scheme

A new charge partitioning scheme is proposed in this section by the addition of an internal node.

#### 3.2.2.1 Need for an additional internal node

The following are the advantages of incorporating an internal node and assigning charges to the internal node in the charge partitioning scheme:

1. The MM20 equations elevates the necessity of the internal node by making several assumptions to the charge partitioning. One of the major unexplained feature of MM20 method of charge partitioning is the way in which there is a difference in the above threshold and below threshold charge assignments, as given by (3.27) and (3.29). Special care should be taken to implement this change in a smooth manner, so that there are no discontinuities in the model because of the usage of two different equations in two operating regions. However, as we shall see later, even if the model is implemented in a smooth manner, there are notable discontinuities in the capacitance plots. These discontinuities become more significant for wider region-II lengths (i.e.,  $L_{dr} \gg L_{ch}$ ). These discontinuities can be completely

avoided by the use of an internal node, in which there are no region based differences in charge partitioning.

- 2. The MM20 model assumes that  $I_{ch} = I_{dr}$  for all cases, including the transient situation. However, if the system is not in steady state, it is observed that  $I_{ch} \neq I_{dr}$ . This difference arises because the two regions are electrostatically different. Under a transient input, both the currents will achieve the same value only when the input stabilizes to a steady value. An addition of an internal node ensures that the electostatically different region-I and region-II charges are dealt with differently.

- 3. Finally, as an added advantage, the accuracy of the model increases further by the addition of an extra internal node.

#### 3.2.2.2 The proposed charge partitioning scheme

A physical basis for charge partitioning using an internal node  $D_i$  was discussed briefly in Chapter 2. A summary of the discussion can be found in Table 2.1. To split the inversion charge in region-I between the nodes S and  $D_i$ , and to split the accumulation and depletion charges in region-II between the nodes  $D_i$  and D' we use a Ward-Dutton partitioning scheme[27].

The following equations describe the new proposed charge partitioning scheme

$$Q_{S} = W \int_{0}^{L_{ch}} \left(1 - \frac{x}{L_{ch}}\right) Q_{inv}^{ch} dx + Q_{n}^{pns},$$

$$Q_{D_{i}} = W \int_{0}^{L_{ch}} \left(\frac{x}{L_{ch}}\right) Q_{inv}^{ch} dx + W \int_{0}^{L_{dr}} \left(1 - \frac{x'}{L_{dr}}\right) \left(Q_{acc}^{dr} + Q_{dep}^{dr}\right) dx' + Q_{n}^{pnd},$$

$$Q_{D'} = W \int_{0}^{L_{dr}} \left(\frac{x'}{L_{dr}}\right) \left(Q_{acc}^{dr} + Q_{dep}^{dr}\right) dx',$$

$$Q_{G} = -W \int_{0}^{L_{ch}} \left(Q_{acc}^{ch} + Q_{dep}^{ch} + Q_{inv}^{ch}\right) dx - W \int_{0}^{L_{dr}} \left(Q_{acc}^{dr} + Q_{dep}^{dr} + Q_{inv}^{dr}\right) dx',$$

$$Q_{B} = W \int_{0}^{L_{ch}} \left(Q_{acc}^{ch} + Q_{dep}^{ch}\right) dx + W \int_{0}^{L_{dr}} \left(Q_{inv}^{dr}\right) dx' + Q_{p}^{pnd} + Q_{p}^{pns}.$$

Here,  $Q_i$  represents total charge assigned to node i ( $i \in G, S, B, D_i, D'$ ),  $Q_{acc}$  is the accumulation charge density per unit area,  $Q_{inv}$  is the inversion layer charge density per unit area and  $Q_{dep}$  is the depletion layer charge density per unit area.

The subscripts ch and dr represents channel (region-I) and drift (region-II) regions respectively of LDMOS transistor. Further,  $Q_n^{pnd}$  ( $Q_n^{pns}$ ) represents the total p-n junction charge in the n-drift region (source junction) and  $Q_p^{pnd} = -Q_n^{pnd}$  ( $Q_p^{pns} = -Q_n^{pns}$ ) is the total p-n junction charge in the p-well on the drain (source) side. Note that x is a co-ordinate system starting from the source terminal and x' is a shifted co-ordinate system starting from the  $D_i$  node.

Notice that the total charge remains conserved, i.e,

$$Q_B + Q_G + Q_S + Q_{D'} + Q_{D_i} = 0. (3.34)$$

#### 3.2.2.3 Formulation of charge in region-I

Since the channel region of SOI-LDMOS is structurally similar to an NMOSFET, charge modeling should be similar to MOS charge modeling. Charges that are of interest to us are the depletion, inversion and accumulation charges. The (negative) depletion charge per unit area  $Q_{dep}^{ch}$  can be written as

$$Q_{dep}^{ch} = \begin{cases} -C_{ox} k_{ch} \sqrt{\psi_s^{ch}} & \text{for } \psi_s^{ch} \ge 0, \\ 0 & \text{for } \psi_s^{ch} < 0, \end{cases}$$

(3.35)

where  $\psi_s^{ch}$  is the surface potential of the channel. Similarly, the (negative) inversion  $(Q_{inv}^{ch})$  and the (positive) accumulation  $(Q_{acc}^{ch})$  charge are given by

$$Q_{inv}^{ch} = \begin{cases} -C_{ox} \left( V_{GB} - V_{FB,ch} - \psi_s^{ch} - k_{ch} \sqrt{\psi_s^{ch}} \right) & \text{for } \psi_s^{ch} \ge 0, \\ 0 & \text{for } \psi_s^{ch} < 0. \end{cases}$$

(3.36)

$$Q_{acc}^{ch} = \begin{cases} -C_{ox} \left( V_{GB} - V_{FB,ch} \right) & \text{for } \psi_s^{ch} < 0, \\ 0 & \text{for } \psi_s^{ch} \ge 0. \end{cases}$$

(3.37)