# MODELING OF GLITCHING EFFECTS IN ESTIMATION OF DYNAMIC POWER CONSUMPTION

A Project Report

submitted by

# K NITISH KUMAR & PRAKRUTHI P

in partial fulfilment of the requirements

for the award of the degree of

BACHELOR OF TECHNOLOGY (ELECTRICAL ENGINEERING)

&

MASTER OF TECHNOLOGY (MICROELECTRONICS AND VLSI)

DEPARTMENT OF ELECTRICAL ENGINERRING INDIAN INSTITUTE OF TECHNOLOGY MADRAS.

**June 2014**

THESIS CERTIFICATE

This is to certify that the thesis titled MODELING OF GLITCHING EFFECTS IN

ESTIMATION OF DYNAMIC POWER CONSUMPTION, submitted by K Nitish

Kumar and Prakruthi P, to the Indian Institute of Technology, Madras, for the award

of the degree of Bachelor of Technology and Master of Technology, is a bona fide

record of the research work done by them under my supervision. The contents of this

thesis, in full or in parts, have not been submitted to any other Institute or University

for the award of any degree or diploma.

Prof. Nitin Chandrachoodan

Research Guide Assistant Professor Dept. of Electrical Engineering IIT-Madras, 600 036

Date: June 13, 2014

Place: Chennai

# **ACKNOWLEDGEMENTS**

"It is good to have a happy end to a journey; but it is the journey that matters in the end."

Foremost, we would like to express our sincere and heartfelt gratitude to our project guide Dr. Nitin Chandrachoodan for his invaluable mentorship, motivation and support throughout the ups and downs of our project. The stimulating weekly discussions and bimonthly reviews helped us stay enthusiastic and head in the right direction all along. We learnt how to be careful about our assumptions and claims, and the importance of not ignoring the outliers in our analysis. Most importantly, he taught us how to cater to every small detail in the project while having the big picture at the back of our minds.

We are overwhelmed to be a part of one of the exemplary and well-knit departments of IIT Madras. We are grateful to all the professors for bestowing the finest knowledge upon us. We also thank the IE lab and DCF staff for their technical support and resources. It would be incomplete without a special mention to the department coffee shop where a lot of bonds were built and memories were made.

We were also privileged to have a really invigorating and supportive lab environment which kept us focused and simultaneously entertained. We are indebted to Celia and Seetal for their valuable inputs to our project at crucial times. A special note goes to Ananth, Nikhil and Jobin for reminding us to rightly pace ourselves throughout the course of our project. We would also like to credit our beloved lab-head, Karthikeyan, for all the encouragement from resolving minor technical problems to getting late-night coffees and mangoes.

We are particularly thankful to a bunch of special people who have made the good times better and the hard times easier - Meghana and Chitra for making the most of every moment, Jayant and Soorya for all the exhilarating technical discussions, Ankit and Anuja for all the emotional abutment, Shikha and Uday for being there as understanding friends at all times and Abraham for inspiring us to work harder and smarter.

Finally, words cannot express how grateful we are for our parents for all their blessings, their sacrifices made on our behalf and their constant belief in us to strive for excellence. We also thank our siblings for all the love and affection they showered upon us to rejoice every moment of our project experience.

# **ABSTRACT**

KEYWORDS: Process Variation; Dynamic Power; Glitches; Monte Carlo Anal-

ysis; Input Variation; Ambiguity Interval Propagation; Probability

Propagation

Process variation has an implicit impact on switching energy consumption by altering the propagation delays of gates in the circuit and thereby, resulting in glitches. We perform Monte Carlo analysis to identify the impact of process variation on switching energy consumption. We also estimate the contribution of glitches resulting due to input and process variation to overall switching energy consumption and signify the need to reduce their propagation to subsequent combinational logic in the design. A new approach to identify the nets in the circuit which result in maximal power reduction if glitches at that net are blocked is presented. Implementation of two algorithms, ambiguity interval propagation and probability propagation to estimate the average number of transitions at each net is also shown. A validation of the approach is done by blocking glitch propagation at nets using latches and estimating power consumption.

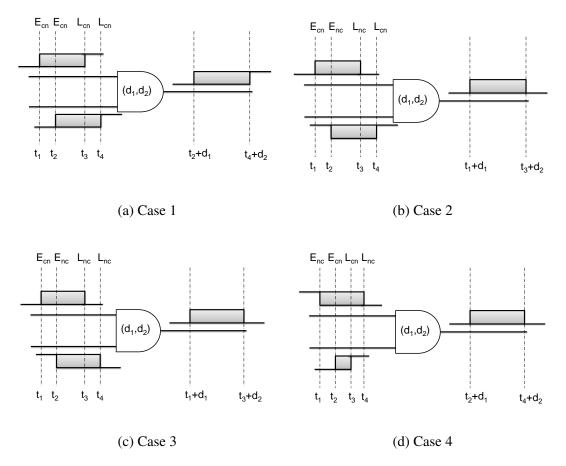

# TABLE OF CONTENTS

| A( | CKNO | OWLEDGEMENTS                                           | i   |

|----|------|--------------------------------------------------------|-----|

| AI | BSTR | ACT                                                    | iii |

| LI | ST O | F TABLES                                               | vii |

| LI | ST O | F FIGURES                                              | ix  |

| Al | BBRE | EVIATIONS                                              | X   |

| 1  | INT  | RODUCTION                                              | 1   |

|    | 1.1  | Motivation                                             | 1   |

|    | 1.2  | Problem Statement                                      | 2   |

|    | 1.3  | Related work                                           | 2   |

|    | 1.4  | Contributions                                          | 5   |

|    | 1.5  | Organization of the thesis                             | 6   |

| 2  | POV  | VER DISSIPATION IN CMOS CIRCUITS                       | 8   |

|    | 2.1  | Components of Power                                    | 8   |

|    |      | 2.1.1 Static Power                                     | 9   |

|    |      | 2.1.2 Dynamic Power                                    | 10  |

|    | 2.2  | VLSI Design Flow                                       | 12  |

|    | 2.3  | Glitches                                               | 13  |

|    | 2.4  | Process Variation                                      | 14  |

| 3  | TRA  | ANSISTOR LEVEL ANALYSIS                                | 16  |

|    | 3.1  | Spice Characterization of gates                        | 16  |

|    |      | 3.1.1 Characterization of AND gate                     | 17  |

|    | 3.2  | Transistor level simulation of a combinational circuit | 19  |

| 4  | COI  | NTRIBUTION OF GLITCHES TO DYNAMIC POWER CONSUMP-       |     |

|   | TIO | N      |                                                                                 | 22 |

|---|-----|--------|---------------------------------------------------------------------------------|----|

|   | 4.1 | Impac  | t of process variation on switching energy                                      | 23 |

|   |     | 4.1.1  | Monte Carlo Analysis using Design Compiler                                      | 23 |

|   |     | 4.1.2  | Power Extraction algorithm for Monte Carlo Analysis                             | 28 |

|   | 4.2 | •      | sis of impact of input variation and process variation on switching consumption | 31 |

|   |     | 4.2.1  | Combined impact of input variation and process variation .                      | 31 |

|   |     | 4.2.2  | Impact of process variation versus input variation                              | 33 |

|   | 4.3 | Analys | sis of glitch power variation                                                   | 37 |

|   |     | 4.3.1  | Procedure                                                                       | 37 |

|   |     | 4.3.2  | Results                                                                         | 38 |

| 5 | AM  | BIGUI  | ΓΥ INTERVAL PROPAGATION                                                         | 43 |

|   | 5.1 | Assum  | nptions                                                                         | 44 |

|   |     | 5.1.1  | Delays of gates                                                                 | 44 |

|   |     | 5.1.2  | Process Variation                                                               | 44 |

|   |     | 5.1.3  | Primary inputs                                                                  | 44 |

|   | 5.2 | Defini | tions                                                                           | 45 |

|   |     | 5.2.1  | Controlling and Non-controlling value                                           | 45 |

|   |     | 5.2.2  | Ambiguity Interval                                                              | 45 |

|   | 5.3 | Metho  | dology                                                                          | 46 |

|   |     | 5.3.1  | DAG representation of the netlist                                               | 46 |

|   |     | 5.3.2  | Evaluation of steady state values                                               | 46 |

|   |     | 5.3.3  | Evaluation of Ambiguity Intervals                                               | 47 |

|   | 5.4 | Power  | Bounds Evaluation                                                               | 51 |

|   |     | 5.4.1  | Maximum number of transitions                                                   | 51 |

|   |     | 5.4.2  | Minimum number of transitions                                                   | 54 |

|   |     | 5.4.3  | Estimation of node capacitances                                                 | 54 |

|   |     | 5.4.4  | Estimation of switching energy                                                  | 55 |

|   | 5.5 | Result | s                                                                               | 55 |

|   | 5.6 | Multip | ole Ambiguity Windows                                                           | 58 |

|   |     | 5.6.1  | Evaluation of Multiple Ambiguity Intervals                                      | 58 |

| 6 | PRO | DBABILITY PROPAGATION                          | 61 |  |  |  |  |  |

|---|-----|------------------------------------------------|----|--|--|--|--|--|

|   | 6.1 | Introduction                                   |    |  |  |  |  |  |

|   | 6.2 | 2 Assumptions                                  |    |  |  |  |  |  |

|   |     | 6.2.1 Gate Delays                              | 62 |  |  |  |  |  |

|   |     | 6.2.2 Primary Inputs                           | 62 |  |  |  |  |  |

|   |     | 6.2.3 Gate Outputs                             | 62 |  |  |  |  |  |

|   |     | 6.2.4 Correlation of inputs                    | 63 |  |  |  |  |  |

|   | 6.3 | Zero Gate Delays                               | 63 |  |  |  |  |  |

|   |     | 6.3.1 Terminology                              | 63 |  |  |  |  |  |

|   |     | 6.3.2 Methodology                              | 64 |  |  |  |  |  |

|   |     | 6.3.3 Power Estimation                         | 66 |  |  |  |  |  |

|   |     | 6.3.4 Results                                  | 66 |  |  |  |  |  |

|   | 6.4 | Non-zero Gate Delays                           | 66 |  |  |  |  |  |

|   |     | 6.4.1 Terminology                              | 68 |  |  |  |  |  |

|   |     | 6.4.2 Methodology                              | 69 |  |  |  |  |  |

|   |     | 6.4.3 Power Estimation                         | 70 |  |  |  |  |  |

|   |     | 6.4.4 Limitations                              | 72 |  |  |  |  |  |

| 7 | GLI | TCH POWER REDUCTION                            | 73 |  |  |  |  |  |

|   | 7.1 | Sensitivity analysis                           | 73 |  |  |  |  |  |

|   |     | 7.1.1 Procedure                                | 74 |  |  |  |  |  |

|   |     | 7.1.2 Results                                  | 76 |  |  |  |  |  |

|   | 7.2 | Glitch reduction using a latch                 | 77 |  |  |  |  |  |

|   |     | 7.2.1 Results                                  | 78 |  |  |  |  |  |

|   | 7.3 | Applications                                   | 80 |  |  |  |  |  |

|   |     | 7.3.1 Retiming for low power                   | 80 |  |  |  |  |  |

|   |     | 7.3.2 Insertion of latches with delayed clocks | 82 |  |  |  |  |  |

| 8 | CO  | NCLUSIONS                                      | 84 |  |  |  |  |  |

|   | 8.1 | Conclusions                                    | 84 |  |  |  |  |  |

|   | 8.2 | Future work                                    | 85 |  |  |  |  |  |

# LIST OF TABLES

| 3.1 | Spice Characterization of AND gate                                                                                                                                                  | 18         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.1 | Mean and Standard Deviations of Total Switching Energy due to both input and process variation for ISCAS '85 benchmark circuits                                                     | 32         |

| 4.2 | Standard deviation of distribution of switching energy due to process variation on Booth Multiplier and C880 circuits using $45\mathrm{nm}$ and $250\mathrm{nm}$ technology library | 36         |

| 4.3 | Analysis of gate count and average switching energy for Booth Multip and C880 circuits using $45\mathrm{nm}$ and $250\mathrm{nm}$ technology library                                | liei<br>37 |

| 4.4 | The percentage of glitch power to Total Dynamic Power for ISCAS '85 benchmark circuits                                                                                              | 41         |

| 5.1 | Controlling and non-controlling values for various gates                                                                                                                            | 45         |

| 5.2 | Comparison of computational time taken by complete Simulation and Ambiguity Window propagation for 500 input vector pairs and for 20% process variation                             | 58         |

# LIST OF FIGURES

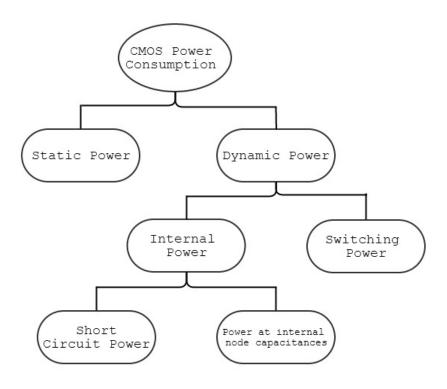

| 2.1  | CMOS Power Consumption                                                                                       | 9  |

|------|--------------------------------------------------------------------------------------------------------------|----|

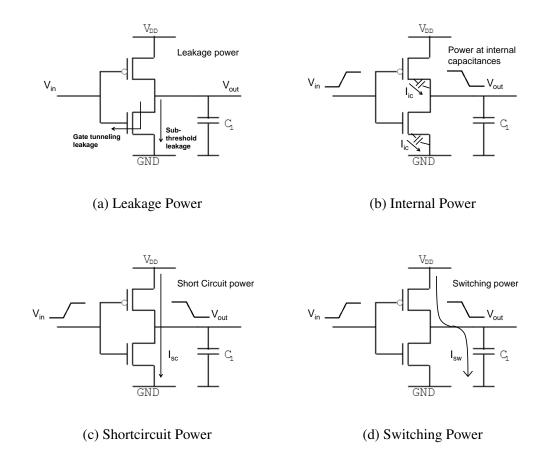

| 2.2  | The four different components of power in a CMOS inverter                                                    | 11 |

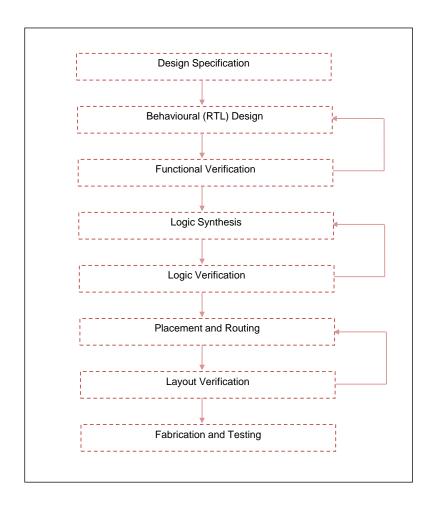

| 2.3  | VLSI Design Flow                                                                                             | 12 |

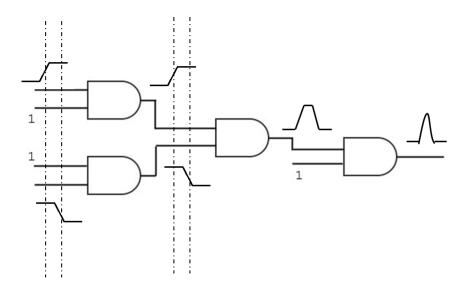

| 2.4  | An example of generation of glitches in a circuit                                                            | 14 |

| 3.1  | Spice characterization of AND gate                                                                           | 17 |

| 3.2  | Comparison of internal energy and switching energy                                                           | 18 |

| 3.3  | Transition time versus output load capacitance                                                               | 19 |

| 3.4  | Energy estimate by spice simulation versus theoretical energy consumed by output capacitance                 | 20 |

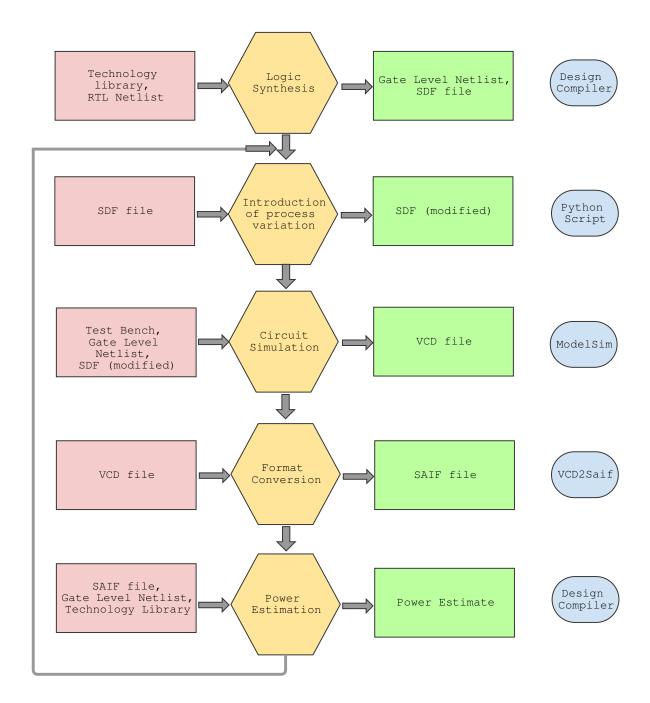

| 4.1  | Flowchart of Monte Carlo analysis using Design Compiler                                                      | 25 |

| 4.2  | Histogram for Monte Carlo analysis of energy dissipation for 10% standard deviation in process variation     | 26 |

| 4.3  | Histogram for Monte Carlo analysis of energy dissipation for 20% standard deviation in process variation     | 26 |

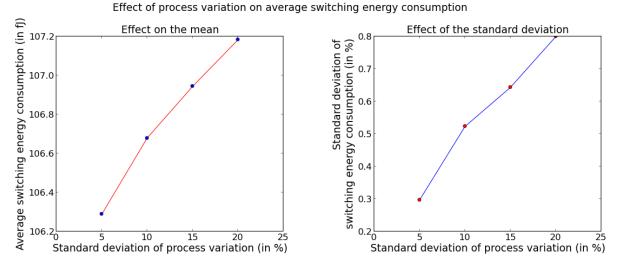

| 4.4  | Effect of process variation on switching energy for different standard deviations in process variation       | 27 |

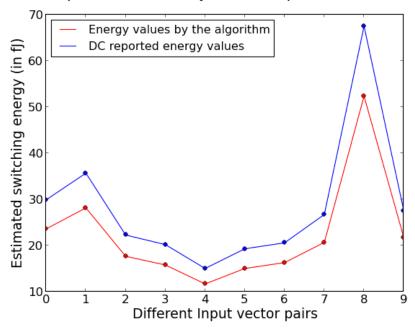

| 4.5  | Switching energy estimate by Design Compiler versus power extraction algorithm                               | 30 |

| 4.6  | Scatter plot of switching energy estimate by Design Compiler versus power extraction algorithm               | 31 |

| 4.7  | Histograms of switching energy for Booth Multiplier and C880 circuit at $45\mathrm{nm}$ and $250\mathrm{nm}$ | 32 |

| 4.8  | Histograms of impact of process variation on switching energy for specific input vector pairs                | 34 |

| 4.9  | Histograms of impact of process variation versus input variation on switching energy                         | 35 |

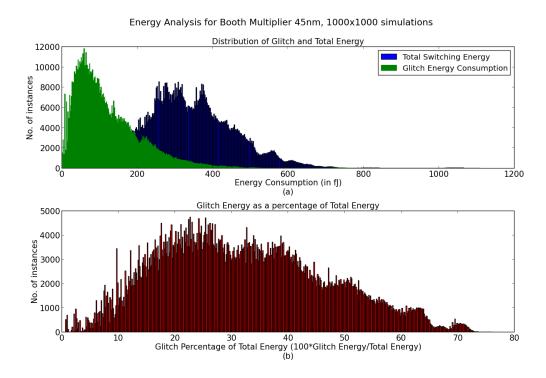

| 4.10 | Contribution of glitches to switching energy for Booth Multiplier circuit at $45\mathrm{nm}$                 | 39 |

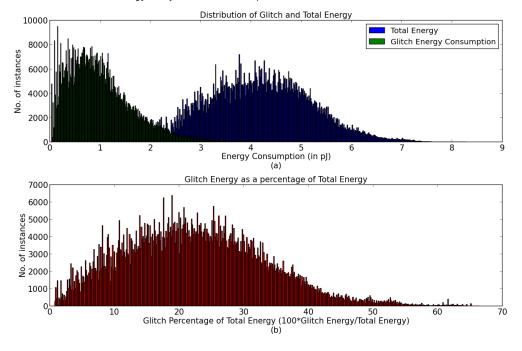

| 4.11 | Contribution of glitches to switching energy for Booth Multiplier circuit at $250\mathrm{nm}$                | 40 |

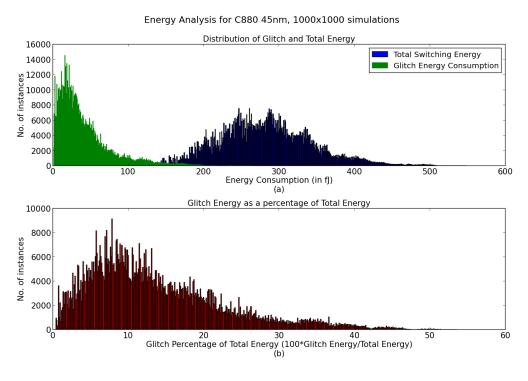

| 4.12 | Contribution of glitches to switching energy for C880 circuit at 45 nm                                       | 40 |

| 4.13 | Contribution of glitches to switching energy for C880 circuit at 250 nm                                          | 41 |

|------|------------------------------------------------------------------------------------------------------------------|----|

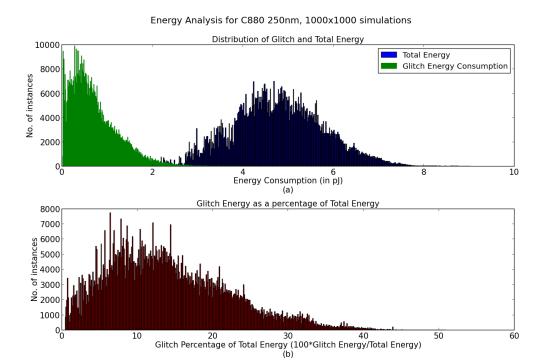

| 4.14 | Contribution of glitches to switching energy for some ISCAS '85 benchmark circuits                               | 42 |

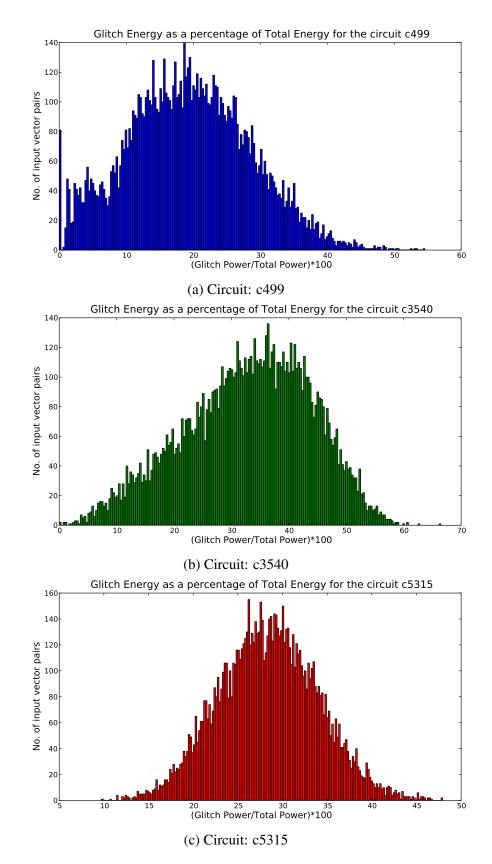

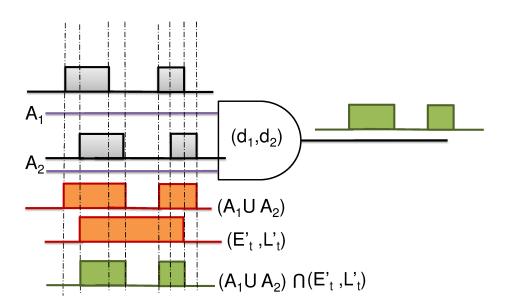

| 5.1  | Evaulation of Earliest Arrival time and Latest Stabilization time for different cases for an AND gate            | 49 |

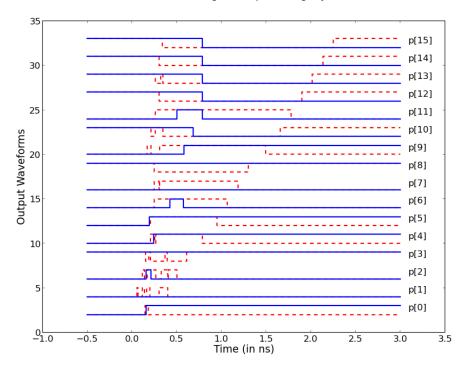

| 5.2  | Simulated waveforms of outputs of Booth Multiplier circuit along with ambiguity intervals                        | 52 |

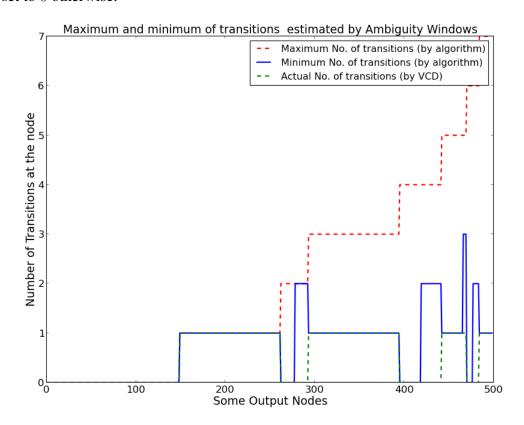

| 5.3  | Simulated number of transitions versus transition bounds estimated by ambiguity propagation method               | 54 |

| 5.4  | Maximum energy at each net by ambiguity propagation method versus simulation for C17, C432 and C1908 circuits    | 56 |

| 5.5  | Maximum energy at each net by ambiguity propagation method versus simulation for C880, C3540 and C499 circuits   | 57 |

| 5.6  | Evaluation of multiple ambiguity windows for an AND gate                                                         | 59 |

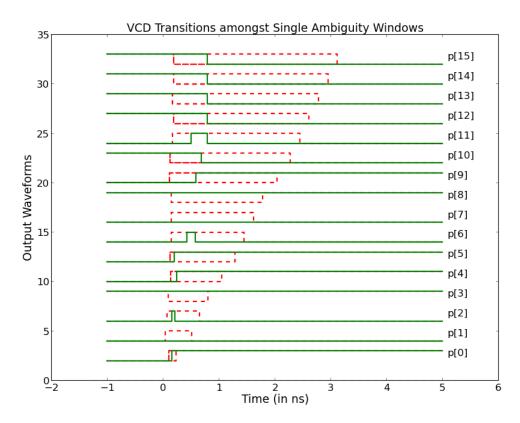

| 5.7  | Simulated waveforms of outputs of Booth Multiplier circuit along with multiple ambiguity intervals               | 60 |

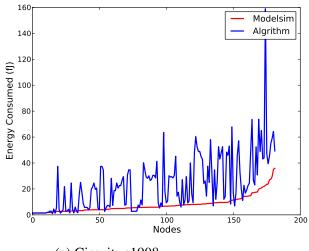

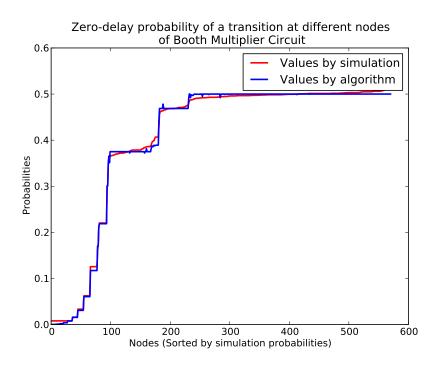

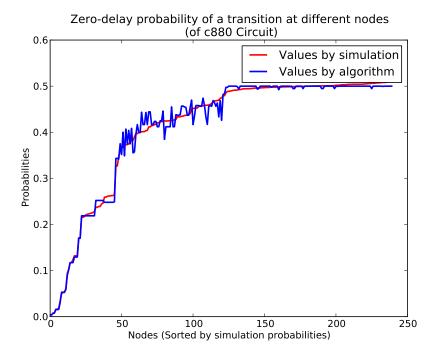

| 6.1  | Expected number of transitions at nodes by probability method and simulation for Booth Multiplier                | 67 |

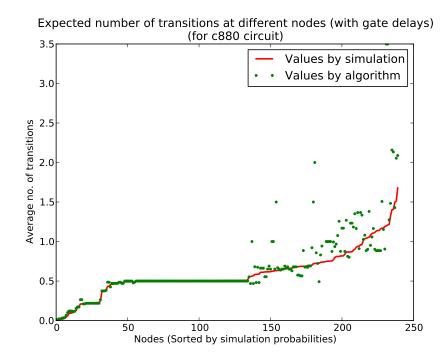

| 6.2  | Expected number of transitions at nodes by probability method and simulation for C880                            | 67 |

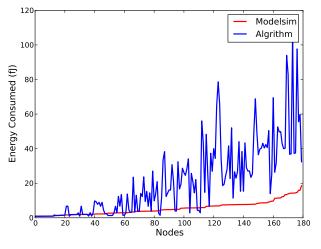

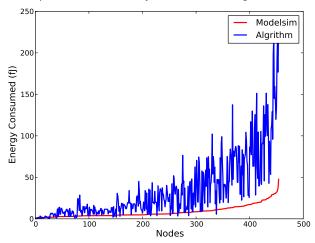

| 6.3  | Expected number of transitions at nodes by probability method and simulation for real delays                     | 71 |

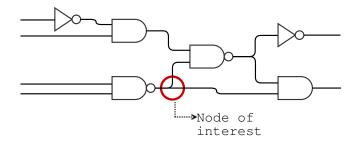

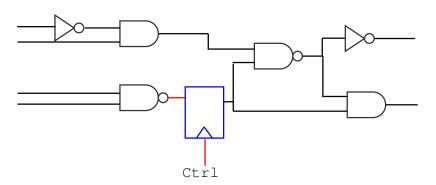

| 7.1  | Example circuit indicating node of interest                                                                      | 75 |

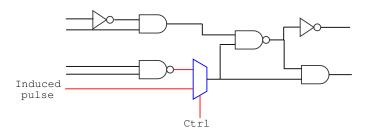

| 7.2  | Example circuit indicating placement of multiplexer at node of interest                                          | 75 |

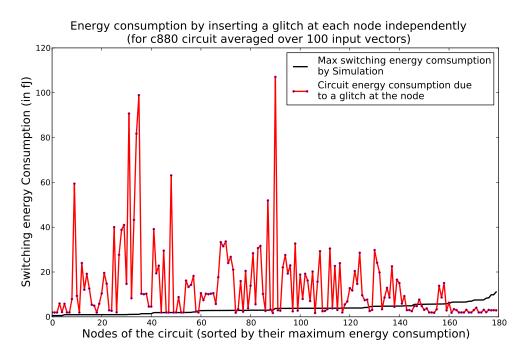

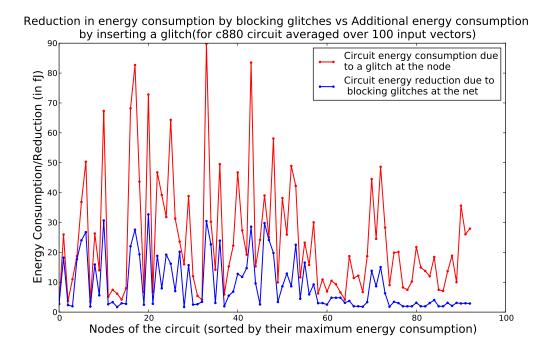

| 7.3  | Average energy consumed due to a glitch induced at intermediary nodes                                            | 76 |

| 7.4  | Example circuit indicating placement of latch at node of interest                                                | 77 |

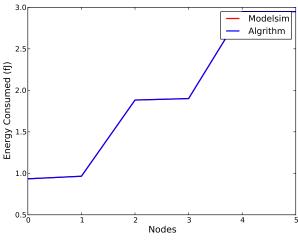

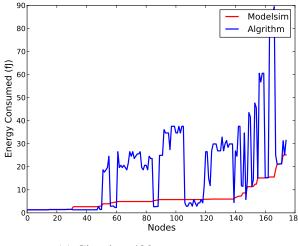

| 7.5  | Switching energy consumed when glitches at nets are blocked                                                      | 78 |

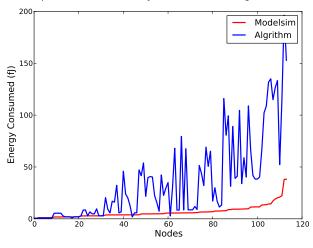

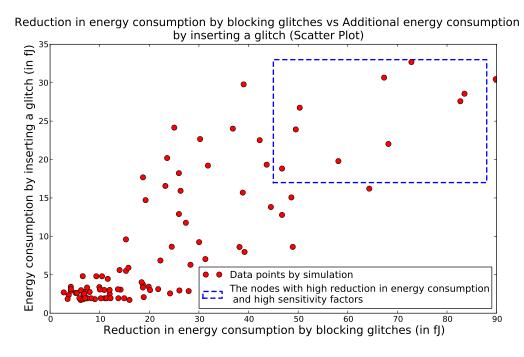

| 7.6  | Switching energy consumed when glitches are blocked versus glitches induced at intermediary nets                 | 79 |

| 7.7  | Scatter plot of switching energy consumed when glitches are blocked versus glitches induced at intermediary nets | 79 |

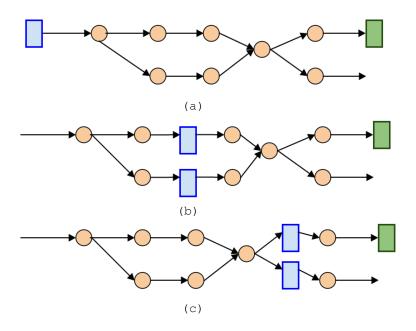

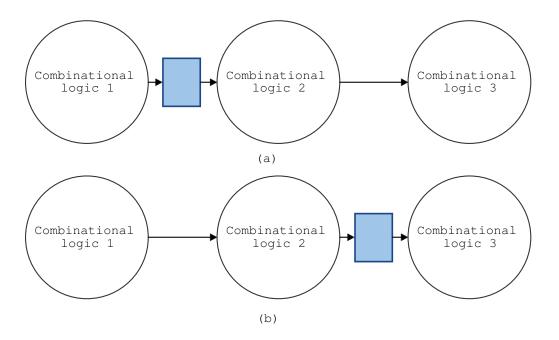

| 7.8  | Example of retiming on a sample circuit. (a): Sample circuit (b)and (c): Retimed circuit                         | 81 |

| 7.9  | Placement of registers at two different locations by retiming algorithm on a sample circuit                      | 82 |

# **ABBREVIATIONS**

**DC** Design Compiler

VCD Value Change Dump

**SAIF** Switching Activity Information File

**SDF** Standard Delay Format

**DAG** Directed Acyclic Graph

**CMOS** Complimentary Metal Oxide Semiconductor

**CAD** Computer Aided Design

**SoC** System on Chip

**RTL** Register Transfer Level

**SPICE** Simulation Program with Integrated Circuit Emphasis

**BDD** Binary Decision Diagrams

# **CHAPTER 1**

# INTRODUCTION

# 1.1 Motivation

The desirability of portable electronic systems has increased significantly over the years. The primary aspect of size of such a device is contributed by its battery, which has direct implications by power consumption of the system. The cost of cooling systems has also increased. Operation of systems at higher frequencies impose limitations on the overall power consumption of the system. Increasing density of CMOS circuits has added additional concerns to the problem of power dissipation. Various factors of system design like power-supply sizing, current requirements, heat sink/cooling arrangements and choice of devices within the system are directly determined by the system power consumption. Reduction of power is known to increase reliability of operation of the device. Hence, the power consumption of digital CMOS circuits has become one of the primary design constraints and is being actively researched for several decades now.

Power consumption is no longer a secondary issue in designing CMOS devices. The designer today has to design systems targeting all the three major design requirements simultaneously: *low power, high performance, small area*. The increasing complexity and high-performance requirements makes the task of designing low power systems challenging. This results in a need to make design decisions early and in accordance with power specifications of the system. System designers are now looking at architectural improvements and automated design methodologies from the stand point of implementation, circuit and logic topologies, digital architectures and algorithms used for low power design. This necessitates estimation of power consumption at every stage of system design cycle to ensure meeting of design specifications.

Apart from meeting average power specifications by the design, estimation of peak power consumption is also needed for better circuit reliability. Large amounts of current dissipation in a short span of time may cause problems of excessive heat generation, resulting in circuit damage in a few cases. It may also cause temporary changes in voltage lines causing operational failure of the circuit. Hence, estimation of maximum power consumption by the design is also crucial for exploring appropriate packaging and cooling options or optimizing power grid networks.

The fact that early and accurate power estimation is continuing to assume greater importance has been the strongest motivation for the present work.

# 1.2 Problem Statement

The key objectives of our work are:

- To identify and analyze the impact of process variation on the Dynamic Power Consumption of combinational CMOS circuits.

- To demonstrate the contribution of glitches to Dynamic Power Consumption and hence signify the need to minimize the propagation of glitches through large combinational blocks.

- To devise a novel time-efficient approach to identify the high glitch nets in a combinational circuit without Monte Carlo Simulations.

- To propose a heuristic to compute the set of nets in a combinational circuit which would result in maximal reduction of total power consumption of the circuit on blocking the glitches at those nets.

# 1.3 Related work

Several researchers have looked at the problem of reduction of CMOS power dissipation using varied approaches. Algorithms, both deterministic and probabilistic approaches have been proposed to efficiently estimate power consumption. Impact of process variation on switching energy consumption has also been actively researched for the past few years.

The paper by Najm (1994) presents a survey of various power estimation techniques. It describes the simulation based techniques for power estimation. It also enumerates the drawbacks like time-inefficiency and high dependence on input vectors by such approaches. It then describes the probabilistic approach to power estimation using signal probabilities and Binary Decision Diagrams (BDDs). The paper by Raghunathan

et al. (1996) looks at early power estimation and design optimization at Register Transfer Level (RTL). It analyzes glitch generation and propagation in data path blocks as well as control logic and suggests design optimization techniques for glitch reduction. Another paper by Najm (1995) also looks at power estimation at RTL. It calculates entropy of gates, given only its boolean implementation function and uses this metric to estimate power consumption at RTL. The paper by Anderson and Najm (2004) suggests a method to predict switching activities at nets and node capacitances early for FPGA designs. It presents a mathematical prediction model to estimate switching activities at nets by considering every glitch at a node to be generated at that node or propagated by its fan-in nodes. It also presents a mathematical model to estimate node capacitances early in the design along with noise considerations.

The paper by Benini et al. (1998) looks at power modeling at system level. The power manager interacts with the resources in the system and receives requests from the environment. This abstract model is used to estimate system level power information of the design. The paper by Dhanwada et al. (2012) presents a new approach called Power Contributor Modeling. In this paper, they separate independent components of power like capacitative switching, short circuit power and leakage power and models are built to estimate the contributions of these components. All the components are summed for individual cells to estimate power consumption. The paper by Qu et al. (2000) elaborates a method to estimate power consumption of microprocessors. They empirically build a power data bank, which contains the power information of various instructions and built-in functions. The execution information of the software run on the microprocessor is used along with the power data bank to estimate power consumption. There is some active research being done in behavioral level power estimation (Qu et al. (2000)). The paper by Buyuksahin and Najm (2005) suggests a high-level estimation of average switching activity, total capacitance and area by using a Boolean network representation of the design.

The paper by Hao *et al.* (2011) considers spatial correlation in process variation and suggests a methodology to estimate dynamic power consumption. It first establishes that variations in process parameters like channel length affect dynamic power consumption significantly. It then presents a method to compute dynamic power statistically at every net in the circuit using orthogonal polynomials and virtual grid based variables for process parameters with spacial correlation. The paper by Dinh *et al.* con-

siders impact of process variation on dynamic power consumption by modeling transition waveforms at inputs of every gate in the design. This paper also considers partial glitches by capturing probability and timing of events at the nets by segmenting these transition waveforms. The paper by Harish *et al.* (2007) presents a simulation based approach to estimating power in the presence of process variation. The process variation is assumed to have a Gaussian distribution. Simultaneous dependence on multiple process parameters is modeled using the statistical technique of Design of Experiments by performing a 3-level Face Centered Central Composite design.

The paper by Alexander and Agrawal (2009) suggests a simulation based approach to estimate bounds on the number of transitions at every net in the circuit. It assumes a bounded delay model for every gate in the design and propagates ambiguity intervals, which represent the minimum and maximum times during which the gate can have probable transitions due to an applied input vector pair. In this thesis, we implement some of the ideas discussed in this paper and propose some applications for the same. The paper by Meixner and Noll (2014) looks at power estimation at a higher level of abstraction. It proposes a methodology to pre-characterize glitch activities in functional blocks of combinational logic using signal statistics at every net in the design. It introduces new metrics like glitch occurrence, glitch width and glitch time to quantify statistical glitching properties on circuit nets. The major drawback of such an approach would be the necessity for time-consuming characterizations. Hence, this methodology is more suited for generic designs.

Some papers by Tsui *et al.* (1993) and Ghosh *et al.* (1992) suggest probabilistic approaches to computing power consumption in CMOS circuits. The paper by Tsui *et al.* (1993) explains the methodology to estimate static and transition probabilities at every net of the circuit and use these parameters to estimate dynamic power consumption of the circuit. It also accounts for correlation at the inputs of intermediary gates in the design while computing power. One major advantage of their methodology is that the algorithm uses real propagation delays for all the gates in the circuit. An improvisation of this approach has been suggested by the paper by Ghosh *et al.* (1992) where the static and transition probabilities are computed by calculating Boolean functions (disjoint covers) that cause switching at every gate in the design. We combine the ideas discussed in both the papers and implement them in this thesis.

The paper by Monteiro *et al.* (1993) looks at retiming algorithms from the perspective of low power. It suggests an iterative methodology to optimally place flip-flops in the circuit such that the timing constraints are not violated, the intended functionality is not altered and total power consumption is minimized.

# 1.4 Contributions

- We have analyzed the impact of process variation on switching energy consumption of combinational CMOS circuits using Monte Carlo analysis. We have also differentiated the contributions of variation in total switching energy due to process variation and due to variation in input stimuli.

- We have highlighted the contribution of glitches to switching energy consumption. For this, we have implemented a time-efficient power extraction algorithm for estimating switching power due to each input vector pair, given the gate-level netlist, technology library file and the VCD file. With this analysis, we signify the importance of reduction of glitches and their propagation in the circuit for achieving low power designs.

- We have implemented two algorithms, ambiguity propagation algorithm and probability propagation algorithm to estimate the average number of transitions at every net in the design and compute bounds on switching energy consumption. We also built an efficient event-driven simulation tool for zero delay simulation of combinational circuits.

- We have proposed a methodology to estimate the total switching energy of the circuit due to a glitch at one of the intermediary nets in the circuit. This analysis would highlight those nets in the circuit where the glitches need to be blocked for maximum switching energy reduction. We validate these results by estimating power reduction in the circuit when glitches at a net are blocked by a latch.

# Scope of the work

- The circuits that we have considered for our analysis are combinational and have a typical gate count ranging between 100 and 1000. We have analyzed the circuits at 45 nm and 250 nm technologies.

- We neglect partial glitches and non-linear input waveforms in all the gate level simulations.

- We have assumed inertial delay model for all the gates in the circuit.

- $\bullet$  Process variation is modeled by introducing a standard normal variation in propagation delays of all gates and by varying their standard deviations. We have not analyzed the effect of individual process parameters and we have assumed a constant source voltage ( $V_{\rm dd}$ ).

Most of our analysis uses only switching power to demonstrate dynamic power and is based on an assumption that internal power is either insignificant or proportional to the switching power. Also, since there is no clock for the combinational circuits, the energy dissipated per transition was considered as an indicator of power consumed, since power consumed is just average energy dissipated per clock period multiplied by the clock frequency.

# 1.5 Organization of the thesis

The reminder of the thesis is organized as follows:

### **Chapter 2: Power dissipation in CMOS circuits**

This chapter describes the various components of power dissipation in CMOS circuits. It also describes the typical VLSI Design Flow and the need for power estimation at various stages of chip design. An introduction to glitches and impact of process variation on switching energy consumption is also presented in this chapter.

#### **Chapter 3: Transistor Level Analysis**

This chapter details the analysis of power dissipation in circuits at the transistor level. Spice characterization of gates is explained with an example. The results of transistor level power dissipation for an AND gate and a combinational circuit have been presented.

#### **Chapter 4: Contribution of glitches to dynamic power consumption**

In this chapter, we present the detailed analysis of contribution of glitches to switching energy consumption of combinational circuits. We also show the individual and combined impact of process variation and variation in input stimuli on switching energy dissipation. We describe the time-efficient power extraction algorithm used for Monte Carlo analysis of the circuit.

#### **Chapter 5: Ambiguity Interval Propagation**

We discuss the ambiguity interval propagation algorithm used to estimate bounds on switching energy consumption of a combinational circuit. We suggest some improvisations on the existing algorithm for better estimation of maximum number of transitions at every net in the design. We also present the results obtained for power estimation by evaluation of multiple ambiguity intervals.

# **Chapter 6: Probability Propagation**

We discuss the probabilistic approach to estimation of switching energy consumption of a combinational circuit in this chapter. We present the results obtained by probability propagation under both zero delay and real delay scenarios. We also show how correlation in input signals of gates can impact power estimation using this approach.

#### **Chapter 7: Glitch Power Reduction**

In this chapter, we discuss the methodology for estimating power reduction by blocking glitches at various nodes in a combination circuit. We present the results of sensitivity analysis of each node to glitch power reduction and validate the same by latch-based glitch reduction approach. We hence, identify the high glitch activity nodes in the circuit.

#### **Chapter 8: Conclusion**

We present the conclusions and inferences drawn from the work done in the thesis. We propose the scope of the work ahead.

# **CHAPTER 2**

# POWER DISSIPATION IN CMOS CIRCUITS

We begin with a review of various components of power dissipation in digital CMOS circuits. We, then explain the typical VLSI Design flow and the need for power estimation at each level. The theory behind glitches and how they are generated is explained with an example. The final section explains process variation and how it impacts power dissipation in detail.

# 2.1 Components of Power

The need for low power devices led to the development of CMOS technologies. CMOS power consumption is primarily determined by two components of power: *Static power consumption* and *Dynamic power consumption*. CMOS devices have very low static power dissipation, owing to lower leakage power compared to other technologies. This power dissipation occurs in steady state, when all the signals in the design do not undergo any switching. However, an increase in operating frequencies of the systems has resulted in increased switching activity of the design. Hence, dynamic power consumption contributes majorly to overall power dissipation of the system. Charging and discharging of capacitances in the design adds primarily to this component of power dissipation.

The power dissipated by a digital CMOS circuit can be broadly classified into two categories.

- Static Power

- Dynamic Power

Figure 2.1 represents the various components of CMOS power consumption.

Figure 2.1: CMOS Power Consumption

# 2.1.1 Static Power

Static power is otherwise called leakage power. Leakage power is the power dissipated by a gate when it is not switching. This happens when the gate is static or inactive in the design. The primary component of leakage power is source-to-drain sub-threshold leakage, which is caused by reduced threshold voltages that prevent the gate from completely turning off. It is caused by currents that flow through the transistors in the gate, even when they are turned off. This component of power is becoming significant in newer technologies. Many-a-times, all sources of leakage power are lumped together into a single value and specified in the technology library for modeling purposes.

Leakage power is caused primarily by reverse biased pn junctions, the sub-threshold leakage current and the gate tunneling effect. This power is dissipated as long as the supply voltage is on. Several other factors like temperature also affect leakage power, due to its direct dependence on thermal voltage and threshold voltage.

# 2.1.2 Dynamic Power

Dynamic power is the power dissipated by a gate when it is active (or switching). A gate is active when the voltage at the net changes during a low to high transition or a high to low transition due to an applied stimulus. Dynamic power is further divided into two components.

- Switching Power

- Internal Power

## **Switching Power**

Switching power of a gate is the power dissipated by charging and discharging of the load capacitance at the output of the gate. The load capacitance is composed of interconnect wire capacitance as well as the input capacitances of the fan-out gates the output is driving. The amount of switching power depends on the switching activity of the gate. This in turn also depends on the operational frequency of the design.

$$SwitchingPower = f \times C_l \times V^2 \tag{2.1}$$

where f is the transition frequency,  $C_l$  is the output load capacitance and V is the supply voltage. Switching power is resulted by two kinds of transitions: *steady state transitions* and *glitches*. Steady state transitions are expected transitions at the nodes in the circuit due to applied stimulus. Glitches are unwanted transitions at the nodes. We will see more about glitches and how they are generated in further sections.

#### **Internal Power**

Internal power is the power dissipated within the boundary of the gate. There are two components of internal power.

- Short Circuit Power

- Power dissipated at internal capacitances

Figure 2.2: The four different components of power in a CMOS inverter.

#### **Short Circuit Power**

During the period when the transistors in a gate switch, there is a momentary short circuit current which flows through them. For a small amount of time, the transistors are all in the ON state and thus, provide a conducting path from supply line to ground. This happens for a small duration of time within the rise or fall time of the input signal to the gate.

#### Power dissipated at internal capacitances

During switching, the gate dissipates some amount of power by charging and discharging of capacitances internal to the gate. The intrinsic gate capacitances depend on the region of operation of the transistors.

Figure 2.2 explains the various components of power dissipation using an inverter as an example gate.

# 2.2 VLSI Design Flow

The VLSI design flow primary comprises of three stages: the *behavioral level*, describing the functionality of the design, the *gate level*, describing the form of implementation and the *physical level*, describing the physical implementation of the design. A simplified view of the design flow is represented in the flow chart (Figure 2.3) below.

Figure 2.3: VLSI Design Flow

In a typical VLSI design flow, we start with system specifications, which signify the intent of the design. These specifications are then converted to Register Transfer Level by architectural synthesis tools. Once the RTL is verified to meet the design specifications, logic synthesis is done by CAD tools to convert it to a gate level netlist. This netlist is then used for placement and routing procedure, after which the chip will be sent for fabrication. The verification of the design at every step plays a significant part of the design process. At every stage, all the design constraints, including power

consumption of the design have to be met to the specifications. In today's SoC designs, several circuit blocks are integrated together into a single system. While designing such complex systems, there is always a trade off between accuracy and computational speed in estimation of power consumption. Accurate estimates are obtained at later stages, when the gate level information is ready. Power estimation is traditionally performed at the transistor level by SPICE simulation at the end of the design flow. However, as the systems get more and more complex, this becomes a computationally intensive task. Moreover, power estimates from the later stages make redesigning of the system difficult and thereby, increasing the time-to-market. Gate level power estimation has become increasingly popular and active research is being done on the same. Power estimates at earlier levels like RTL are less accurate than gate level estimates. Algorithms to estimate power at earlier levels are being developed.

# 2.3 Glitches

Glitches are unwanted transitions at the output of a gate due to the skew in its input signals. This arises primarily due to unbalanced path delays in the circuit. When several paths arriving at one internal gate have different propagation delays, the gate undergoes several unnecessary transitions before settling to the correct logic level.

Consider the example shown in Figure 2.4. Due to path delays at earlier levels in the circuit, the two transitions at the inputs do not occur at the same time. They are shifted in time by a small amount. This results in a 0 - 1 - 0 transition at the final levels in the circuit. Observe that the glitch at the output do not undergo a complete 0 - 1 - 0 transition. Such transitions are called *partial glitches*. Partial glitches are those glitches whose pulse width is too short in comparison to gate delay. They are even more difficult to evaluate in the circuit. Since we assume inertial delay model for the gates in the design, we will not be considering partial glitch transitions in our analysis.

Switching energy consumption is altered by two kinds of transitions: *steady state transitions* and *glitches*. As we will see in further chapters, glitches contribute significantly to switching energy dissipation of the circuit. If glitches are generated at earlier levels in the circuit, they propagate further through the gates till the output. Hence,

Figure 2.4: An example of generation of glitches in a circuit

glitch transitions can give rise to several other glitch transitions further down the network. In larger designs, this increases switching power of the circuit significantly.

# 2.4 Process Variation

Process variations are the variations in parameters like oxide thickness, threshold voltage, channel length and interconnect wire properties introduced during the semiconductor fabrication process. They can be broadly classified into two categories: *inter-die* and *intra-die* variations. Inter-die variations are the variations on the same wafer lot across several dies. In this case, the parameters within an individual die remain constant. Intra-die variations are variations introduced within the same die during the fabrication process. In this case, some of the parameters within the same die vary across the surface area of the die. In today's nano-scale technologies, there is wider amount of process variation. Process variations, typically alter one or more of threshold voltage, channel length or operating temperature. This generates uncertainty in gate delays, thereby, altering switching energy consumption of the design. This effect varies from device to device. Glitch transitions are primarily dependent on gate delays of the circuit. Power supply fluctuations, interconnect noise and temperature fluctuations are some of

the factors which affect gate delays in the design. Contribution of glitches to switching energy consumption is increasingly becoming significant in nano-scale technologies.

The sub-threshold leakage current, which is a primary component of leakage power can be calculated by Equation (2.2).

$$I_{sub} = \mu_0 C_{ox} \frac{W}{L} V_t^2 e^{(\frac{V_{gs} - V_{th}}{nV_{th}})} (1 - e^{(\frac{-V_{ds}}{V_t})})$$

(2.2)

where  $\mu_0$  is effective mobility,  $C_{ox}$  is gate oxide capacitance per unit area, W is gate width, L is channel length,  $V_{gs}$  and  $V_{ds}$  are gate to source and drain to source voltages respectively,  $V_{th}$  is the threshold voltage,  $V_t = \frac{kT}{q}$  is the thermal voltage and n is a technology parameter.

As we can see from Equation (2.2), leakage power depends on threshold voltage, temperature and channel length. Hence, process variation has a direct impact on leakage power. However, it doesn't affect dynamic power directly. It alters the gate delays in the circuit, thereby increasing the number of glitch transitions in many cases. This in turn increases switching power as the number of transitions increases.

# **CHAPTER 3**

# TRANSISTOR LEVEL ANALYSIS

One of the primary objectives of our work is to identify the impact of process variation on switching energy consumption, and hence, estimate the contribution of glitches to switching energy. One of the most accurate ways of doing this is by a simulation at the transistor level across several inputs. However, an exhaustive simulation like this would be computationally time intensive. As explained in earlier sections, there is always a trade off between accuracy and computational speed in estimation of power. So, typically a gate level simulation is done to estimate the overall power consumption. The simulations at this level are done usually by CAD tools. These estimates will not consider partial glitches and non-linearity of waveforms at all the nets in the design. Hence, there will be some loss of accuracy with these estimates.

In this chapter, we will look at characterization of gates and simulation of larger combinational circuits at transistor level and how they compare to gate level power estimates using CAD tools.

# 3.1 Spice Characterization of gates

Power consumption by a logic gate depends on various environmental and process parameters. Logic family, topology and sizing of transistors, rail voltages, the output load capacitance the gate drives and the input stimulus are some of the primary factors which directly influence the power dissipated by the gate. Typically, CAD tools use the technology library file for the power characteristics of individual gates. The library file has information about the power consumed by each gate across several load capacitance values. In order to ensure that the power estimation at gate level by CAD tools adequately captures the impact of process variation on power consumption of the circuit, we first need to validate the same at transistor level using spice simulation. And to do that, the power characterization values in the library used by the CAD tools also need to be validated against values by the spice simulator being used for simulations.

This section deals with characterization of a logic gate in order to predict its energy consumption for various driving load capacitances.

# 3.1.1 Characterization of AND gate

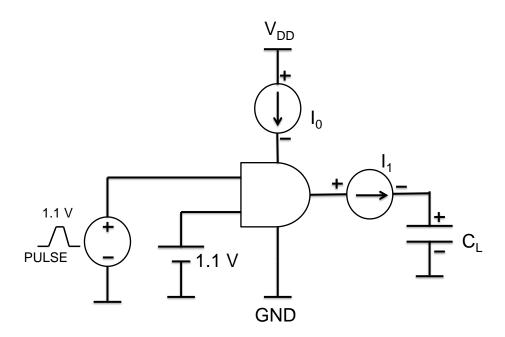

Characterization of a gate for power consumption is done for several values of input transition times and total output net capacitances. A rising or falling transition is given as one of the inputs while keeping the other input constant. 0 V voltage sources are used at various signals to measure the current flowing through those signals. Figure 3.1 shows the circuit used for the characterization.

Figure 3.1: Spice characterization of AND gate

The analysis is done on a two input AND gate using *Spice Opus* software. A pulse of voltage  $1.1\,V$  is used to give a rising or a falling transition at one of the inputs. The other input of AND gate is fed to a  $1.1\,V$  DC voltage source. The  $V_{\rm DD}$  rail is kept at  $1.1\,V$  and GND rail at  $0\,V$ . Simulation is done for several values of load capacitance  $C_{\rm LOAD}$ . The  $0\,V$  voltage sources at the  $V_{\rm DD}$  rail and at the output of the AND gate measure the current flowing in those signals. A rising transition with a rise time of 0.00117378 ns is given to one of the inputs of the AND gate. PTM  $45\,\mathrm{nm}$  technology model file is used for spice simulation.

Table 3.1: Spice Characterization of AND gate

| Output      | Transition | Peak    | Total Energy | $E_{consumed}$                |            |                            |

|-------------|------------|---------|--------------|-------------------------------|------------|----------------------------|

| Capacitance | Time       | Current | Consumed     | $-\mathrm{E}_{\mathrm{load}}$ | $E_{load}$ | $0.5 \times \mathrm{CV^2}$ |

| Capacitance | (ps)       | (mA)    | (fJ)         | (fJ)                          | (fJ)       | (fJ)                       |

| 0.365616    | 13.6       | 0.154   | 2.37         | 2.13                          | 0.242      | 0.221198                   |

| 1.89304     | 23.7       | 0.191   | 4.14         | 2.88                          | 1.25       | 1.14529                    |

| 3.78609     | 36.3       | 0.207   | 6.41         | 3.90                          | 2.51       | 2.29058                    |

| 7.57217     | 62.0       | 0.221   | 10.8         | 5.96                          | 4.87       | 4.58116                    |

| 15.1443     | 114        | 0.232   | 20.5         | 10.4                          | 10.1       | 9.1623                     |

| 30.2887     | 220        | 0.241   | 38.8         | 18.7                          | 20.1       | 18.3247                    |

| 60.5774     | 431        | 0.244   | 74.4         | 35.3                          | 39.0       | 36.6493                    |

The following inferences are drawn from Table 3.1.

- The transition time almost proportionally increases with load capacitance.

- The peak current is relatively constant for all loads.

- The value  $E_{load}$ , which is obtained by spice simulation is nearly equal to theoretical value of energy consumed by the load capacitance,  $0.5 \, C \, V^2$ .

- Power dissipated in the internal capacitances of the gate is negligible in comparison to short circuit power.

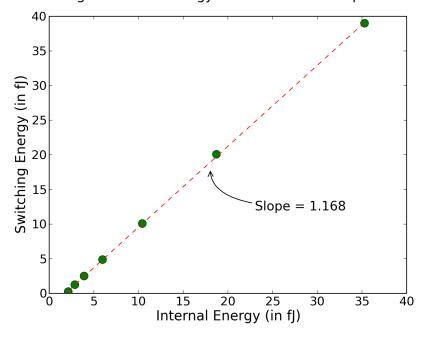

Switching vs Internal Energy for different load capacitances

Figure 3.2: A comparison of contributions of internal energy and switching energy to dynamic power for different load capacitances for a 2-input AND gate

Figure 3.2 shows the contribution of internal energy and switching energy to dynamic power consumption of AND gate for various values of output load capacitance. We observe that both the components, switching energy and internal energy significantly contribute to overall dynamic power consumption of the gate. They also increase with increase in output load capacitance of the gate.

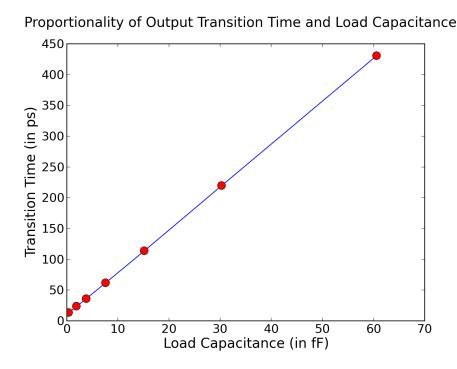

Figure 3.3: Transition time of the signal at the output node versus output load capacitance for a 2-input AND gate

Figure 3.3 shows the transition times of the signal at the output node of the AND gate for several values of output load capacitances. We observe that the transition time is nearly proportional to the output load capacitance.

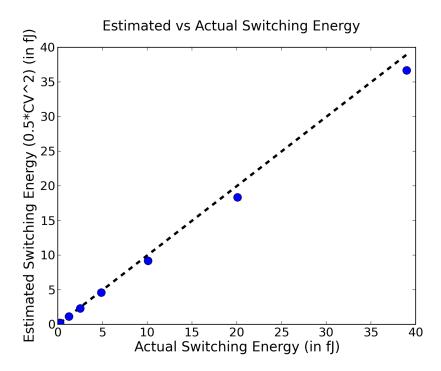

Figure 3.4 compares the energy estimate for the load obtained by spice simulation and its theoretical estimate of  $0.5 \text{ CV}^2$ . We observe that the two values are nearly equal.

# 3.2 Transistor level simulation of a combinational circuit

In the previous section, we characterized a two input AND gate and analyzed the contribution of various sources of power dissipation. In this section, we look at a combi-

Figure 3.4: A comparison of the energy estimate obtained by spice simulation and theoretical value of energy consumed by output load capacitance for a 2-input AND gate

national circuit and estimate power consumed by the circuit at transistor level. We also analyze the pros and cons of power estimation at transistor level.

A combinational circuit is modeled as a network of transistors, voltage and current sources at the transistor level. Spice simulator solves for the node current and voltage equations using Kirchoff's laws. The spice simulation then captures the voltage and current waveforms at all the signals in the circuit due to the applied input stimulus. A gate level power estimate doesn't account for partial glitches and non-linearity in waveforms at the nodes of the circuit. Hence, the estimates obtained at gate level aren't as accurate as transistor level estimates.

The primary advantage of transistor level analysis is the high accuracy of power estimates as compared to gate level estimates. Transistor level estimation considers non-linearity of waveforms at inputs of the gates and partial glitches in the circuit. However, it is highly time intensive. Gate level estimation, on the other hand, is time efficient comparatively and easier to model. There is loss of accuracy at gate level owing to negligence of partial glitches and non-linearity of waveforms at inputs of gates in the circuit.

The circuit that is simulated is an 8 × 8 Booth Multiplier circuit. NanGate 45 nm technology file is used. Synopsys Design Compiler converts the verilog RTL netlist of the circuit into a gate level netlist. This is then converted into an equivalent transistor level netlist using the tool Calibre. Since the netlist file rendered by Calibre will not have input sources, the netlist is then modified using a Python script to form an Eldo spice simulation file. Appropriate pulse waveforms are applied at the input voltage sources to match with the input pairs used by Synopsys Design Compiler. The total power dissipation by the circuit is estimated then by Eldo spice simulator. Eldo spice simulator converts every logic gate in the circuit into its corresponding transistor level sub-circuit. These sub-circuits are then simulated at transistor level for an applied stimulus. Synopsys Design Compiler uses the characterized power estimates from NanGate 45 nm technology file for each gate in its power estimation.

We observed that Eldo spice simulation takes about 10-15 minutes for simulating Booth Multiplier circuit for one input vector pair. Monte Carlo analysis of switching energy consumption of circuits would be highly time-consuming and hence, transistor level simulation was not taken forward in our analysis.

# **CHAPTER 4**

# CONTRIBUTION OF GLITCHES TO DYNAMIC POWER CONSUMPTION

Power consumption of a CMOS circuit is contributed primarily by static leakage power and dynamic power due to switching activities at nodes in the circuit. The switching activities at various nodes in the circuit are caused by two kinds of transitions. The first kind of transition is the expected steady state transition at each node due to an applied stimulus to the circuit. The second kind of transitions are caused by unbalanced delays in various paths in the circuit. These transitions are called glitches and they contribute significantly to the switching power of the circuit. When several stages of combinational logic are pipelined together, glitches generated at earlier stages propagate further down the network, resulting in significant increase in overall power consumption of the design. Glitch estimation at Register Transfer level is highly inaccurate. Typically, it is estimated at gate level.

As seen in chapter 2, process variation also significantly impacts the number of glitch transitions generated in the network. Process variations are the variations in parameters like oxide thickness, threshold voltage, channel length and interconnect wire properties introduced during the semiconductor fabrication process. We also saw that process variation does not have a direct impact on switching energy consumption, but alters delays of gates in the circuit, thereby generating glitches. Some of parameters majorly altered by process variation includes Threshold Voltage  $(V_t)$ , Temperature (T) and Channel Length (L).

In this chapter, we will see the impact of process variation on combinational circuits and contribution of glitches to overall switching energy consumption of the circuit in detail.

# 4.1 Impact of process variation on switching energy

One of the most accurate ways of modeling process variation is by introducing variation in individual parameters like temperature or threshold voltage independently and estimating power. Process variation can cause both intra-die and inter-die variations. Intra-die variations can have spacial correlation between several parameters within a die. Hence, modeling process variation at a parametric level, inclusive of several correlations is difficult. We assume that the variation on individual parameters are independent. Process variation alters delays of gates in the circuit. Hence, we lump the effect on individual parameters together and model the variation at gate level. We do so by introducing a standard normal variation on the propagation delays of all the gates in the circuit. We do a Monte Carlo analysis by simulating the circuit many times over in order to obtain the distribution of switching energy consumption.

# 4.1.1 Monte Carlo Analysis using Design Compiler

Process variation is modeled by introducing a standard normal variation in propagation delays of all the gates in the circuit. The circuit is simulated many times, each time modifying the delays of all the gates in the circuit. The simulation is also done for several values of standard deviation of the normal distribution being introduced. The detailed procedure of the simulation is explained below.

#### **Procedure**

Step 1: The RTL netlist of the circuit is converted into a gate level netlist using Synopsys Design Compiler (DC). DC takes a technology library file as input. The RTL netlist is read in and compiled by the compiler. It then translates the design into a technology-independent design. It also optimizes the design at architectural level, logic level and gate level. Next, the cells in the technology-independent design is mapped to the corresponding cells in the technology library file. The propagation delays of all the gates and interconnect delays of all the nodes of the circuit are annotated in the Standard Delay Format file. DC generates the gate level netlist and the SDF files as the output.

**Step 2:** The standard normal variation in propagation delays of all the gates in the circuit is introduced by modifying the SDF file, generated as output in the previous step. For every gate, the SDF file contains annotations of the minimum, typical and maximum propagation delay for a rising transition as well as for a falling transition for each input of the gate to its output. A normal variation is induced on each of these propagation delay values using a Python script in every iteration of the simulation.

**Step 3:** The circuit is then simulated by a CAD tool *ModelSim* from *Mentor Grpahics*. The gate level netlist, the SDF file and a test bench of the circuit are given as inputs to *ModelSim*. The test bench contains the input stimulus applied to the circuit. The tool then generates a Value Change Dump (VCD) file after simulation. This file contains a series of time-ordered value changes of all the signals in the circuit in the given simulation.

**Step 4:** The VCD file is converted into a SAIF file. SAIF is the format compatible with *Synopsys DC*.

**Step 5:** The SAIF file, gate level netlist and the technology library file are given as inputs to *Synopsys DC*. This then estimates the various components of power dissipated in the circuit using the transitions of the signals annotated in the SAIF file.

**Step 6:** The circuit is simulated many times, by repeating steps 2-5. We then obtain the profile of power dissipation in the circuit for the introduced process variation.

Figure 4.1 depicts a flowchart of the procedure used for Monte Carlo analysis of power consumption using Design Compiler.

## Results

An  $8 \times 8$  Booth Multiplier circuit is simulated for one input vector pair. The SDF file is modified and simulated 1000 times. NanGate  $mathrm45\,nm$  technology library is used as the library file for linking the design.

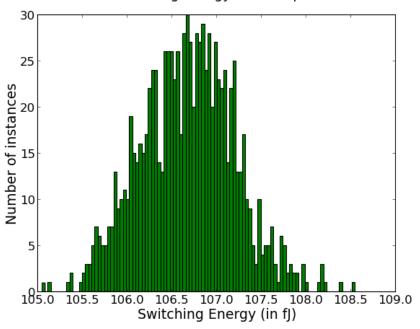

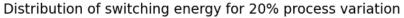

Figures 4.2 and 4.3 show the histograms for Monte Carlo analysis of power

Figure 4.1: Flowchart of the procedure used for Monte Carlo Power Estimation Analysis using Design Compiler

## Distribution of switching energy for 10% process variation

Figure 4.2: Histogram for Monte Carlo analysis of energy dissipation in Booth Multiplier circuit for a 10% standard deviation in process variation. SDF file is modified 1000 times and simulated for one input vector pair. Circuit is synthesized using NanGate 45 nm library.

Figure 4.3: Histogram for Monte Carlo analysis of energy dissipation in Booth Multiplier circuit for a 20% standard deviation in process variation. SDF file is modified 1000 times and simulated for one input vector pair. Circuit is synthesized using NanGate 45 nm library.

dissipation in Booth Multiplier circuit for a 10% and 20% standard deviation in process variation respectively. One input vector pair was simulated for 1000 different SDF files.

Figure 4.4: Effect of process variation on average switching energy consumption in Booth Multiplier circuit for different values of standard deviation in process variation. SDF file is modified 1000 times and simulated for one input vector pair for each value of standard deviation. Circuit is synthesized using NanGate 45 nm library.

Figure 4.4 shows the effect of process variation on overall average switching energy consumption of the circuit. The circuit was simulated for 5%, 10%, 15% and 20% standard deviation in process variation. As we can see from the figure, both mean and standard deviation of total switching energy consumption of the circuit increases with increase in standard deviation in process variation. The mean and standard deviation of total switching energy consumption of the circuit were computed for 1000 simulations of modification of SDF file for one input vector pair.

Different input vector pairs cause a different number of transitions in the nodes of the circuit, thereby resulting in different total switching energy consumption values. The analysis so far was done for one specific input vector pair. In order to eliminate the effect of variation in switching energy consumption due to different inputs, we need to simulate the circuit for several input vector pairs. The bottleneck of the procedure described in this section is that the power estimation of the circuit using  $Design\ Compiler$  is computationally a time intensive step. Invoking and running the tool for  $10^6$  runs (1000 different inputs and 1000 modifications of SDF file each) would lower the computational efficiency of the process. This necessitates an alternative efficient ap-

proach to estimate power using the VCD output generated by *ModelSim*. The standard deviation in process variation was set as 20% for all the analysis in the reminder of the chapter.

## **4.1.2** Power Extraction algorithm for Monte Carlo Analysis

We propose a time-efficient algorithm to primarily estimate switching energy consumption of a circuit. This algorithm also allows us to selectively compute power dissipated in a specified time interval (or for a particular input vector pair) and even segregate the power consumption due to glitches from the total switching energy. It is based on the simple principle that the switching power at any node can be independently computed just by knowing the number of transitions and capacitance of that node.

$$Switching Energy = \sum_{i \in all nodes} t_i \times \frac{1}{2} C_i V^2$$

(4.1)

where  $t_i$  is the number of transitions at node i,  $C_i$  is the capacitance at node i and V is the supply voltage.

Total switching energy of the circuit can be evaluated by equation (4.1). It is equal to the sum of switching energies at every net in the design.

#### Inputs of the algorithm

- VCD file generated by *ModelSim* after simulation of the circuit.

- Gate level netlist of the circuit

- Technology library used for logic synthesis of the design

#### Output of the algorithm

The primary output of the algorithm is the total switching energy dissipated by the circuit. The algorithm also allows us to estimate switching energy for each input vector pair. It can also output the switching energy estimates for a particular net in the circuit.

#### **Procedure**

The algorithm assumes that the steps 1-3 of the procedure described in the above subsection are carried out and the VCD file has been generated after simulation of the circuit by *ModelSim*.

**Step 4:** The number of rising and falling transitions at every net in the design is evaluated by parsing the VCD file by a Python script. This estimates the total number of rising transitions and the total number of falling transitions at every net in the circuit, thereby estimating the total number of toggles in the circuit.

**Step 5:** The rising and falling input capacitances of all the fan-out gates of a net are summed individually and a look-up table is created for rising and falling capacitances at every net in the circuit. This is done once for a particular circuit. The rising and falling capacitances for each net are then extracted from this look-up table in each simulation.

Step 6: The value of number of rising transitions at a net is multiplied with the corresponding rising capacitance value and the number of falling transitions is multiplied with the corresponding falling capacitance. These two values are added and multiplied with  $V^2$ . This value is then evaluated for every net in the circuit and summed together to obtain the total switching energy of the circuit.

**Note:** In this approach, a Python script is used to estimate switching power dissipation of the circuit. The circuit is simulated many times for several modifications of the SDF file. However, unlike in the previous approach where the circuit had to be simulated for each applied input for each SDF, this approach enables us to provide all the inputs together in the test bench and simulate the circuit just once for a particular SDF file.

#### Results

The power extraction algorithm is validated by simulating an 8×8 Booth Multiplier circuit for 100 different input vector pairs and using the SDF file generated by *Synopsys*

Design Compiler during logic synthesis. The NanGate 45 nm library is used as technology library. The overall switching energy of the circuit for each applied input vector pair is evaluated by both the Design Compiler approach and by our power extraction algorithm.

Comparison of power estimation by DC & from power estimation algorithm

Figure 4.5: Comparison of overall switching energy consumption of Booth Multiplier circuit by Design Compiler and power extraction algorithm for different input vector pairs, considering a standard SDF file and NanGate 45 nm technology library.

Figure 4.5 shows the comparison between the switching energy of the circuit obtained by both the approaches for some applied input vector pairs. This figure indicates that the values obtained by both the approaches are almost proportional. This is more clearly observed from the scatter plot shown in figure 4.6. In this figure, the energy estimates of the circuit for 100 input vector pairs obtained by both the approaches have been depicted. The deviation from the power reported by DC is because DC also includes wireloads for the nodes which are ignored in our computation.

Comparison of power estimation by DC & from power estimation algorithm

Figure 4.6: Comparison of overall switching energy consumption of Booth Multiplier circuit by Design Compiler and power extraction algorithm for 100 input vector pairs, considering a standard SDF file and NanGate 45 nm technology library.

# 4.2 Analysis of impact of input variation and process variation on switching energy consumption

# 4.2.1 Combined impact of input variation and process variation

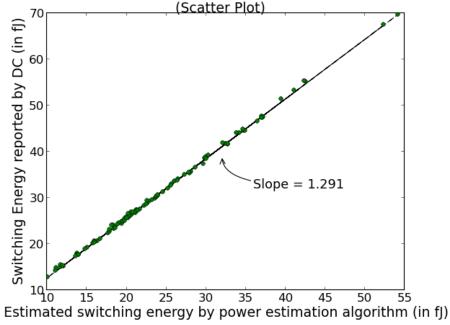

Total switching energy dissipation in a circuit is affected by variation in input stimulus as well as process variation. In this subsection, we see the impact of simultaneous variation in input stimulus and process variation. We also observe this impact across two different technologies,  $45\,\mathrm{nm}$  and  $250\,\mathrm{nm}$  for two circuits, an  $8\times8\,\mathrm{Booth}$  Multiplier and an ISCAS85 benchmark circuit c880, which is an  $8-\mathrm{bit}$  ALU. The circuits are simulated by power extraction algorithm using the approach mentioned in the above subsection. 1000 input vector pairs are applied to the circuits and for each input vector applied, SDF files are modified 1000 times. Two technology libraries,  $45\,\mathrm{nm}$  and  $250\,\mathrm{nm}$  were used for simulating the circuits.

Figure 4.7 shows the distributions of power dissipation for two circuits, Booth Multiplier and c880 at two different technologies,  $45\,\mathrm{nm}$  and  $250\,\mathrm{nm}$ . The his-

#### Energy Distribution for 1000x1000 MonteCarlo Simulations

Figure 4.7: Histograms of total switching energy distribution for Booth Multiplier and C880 circuit at  $45\,\mathrm{nm}$  and  $250\,\mathrm{nm}$ . Circuits are simulated for 1000 input vector pairs and SDF files are modified 1000 times.

Table 4.1: Mean and Standard Deviations of Total Switching Energy due to both input and process variation for ISCAS '85 benchmark circuits

|         | Total Switching Energy Consumption (fJ) |                    |                    |  |

|---------|-----------------------------------------|--------------------|--------------------|--|

| Circuit | Mean                                    | Standard Deviation | Overall Range      |  |

| c17     | 3.49                                    | 2.08               | 0 - 9.66           |  |

| c1908   | 237.81                                  | 69.09              | 57.81-580.18       |  |

| c3540   | 688.80                                  | 199.88             | 94.43 - 1413.14    |  |

| c432    | 115.01                                  | 40.43              | 23.53 - 349.36     |  |

| c499    | 182.99                                  | 35.92              | 70.14 - 372.91     |  |

| c6288   | 19172.87                                | 2822.48            | 5019.21 - 27702.34 |  |

| c880    | 160.90                                  | 49.79              | 44.61 - 391.08     |  |

tograms represent the total switching energy distribution combining the effects of both process variation and input variation. This analysis is done for the ISCAS '85 benchmarks, and the statistical parameters & range of the variation in switching energy distribution have been tabulated in table 4.1.

As we can infer from these distributions and the table, switching energy consumption does have a signification variation (when inputs and process parameters are varied) regardless of the circuit or the technology.

## 4.2.2 Impact of process variation versus input variation

We have seen earlier that the variation in power dissipation of the circuit is caused by both variation in applied input stimulus as well as process variation. In the previous section, we observed their combined impact on switching energy consumption of circuits. In this section, we separate and analyze the impact of both the variations on total switching energy of the circuit.

Just as in the previous simulation, an  $8 \times 8$  Booth Multiplier circuit is simulated using  $45\,\mathrm{nm}$  technology library file, 1000 input vector pairs are applied to the circuit and for each pair the SDF file is modified 1000 times (an over-all of  $10^6$  simulations).

For a particular input vector pair, we plot the distribution of switching energy of the circuit for 1000 modifications of the SDF file. This would represent the impact of process variation alone on switching energy. We can do this for many input pairs to capture the overlap. We also take a standard SDF file, generated during logic synthesis by *Synopsys Design Compiler* and simulate the circuit for 1000 different applied input vector pairs. Hence, we identify the impact of process variation by keeping the input stimulus constant and the impact of variation in input stimulus by keeping the gate delays constant.

We observe that the impact of process variation for each input vector pair follows a normal distribution and the mean of the distribution is equal to the total switching energy of the circuit for that input vector pair for the standard SDF file. We also observe that the impact of variation in input stimuli on switching energy is far more significant than the impact of process variation on the same.

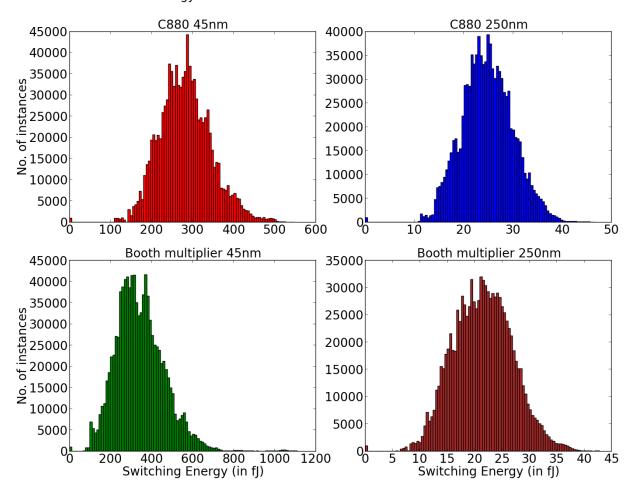

# Components of Process Variation and Input Variation to variation in Energy Consumption

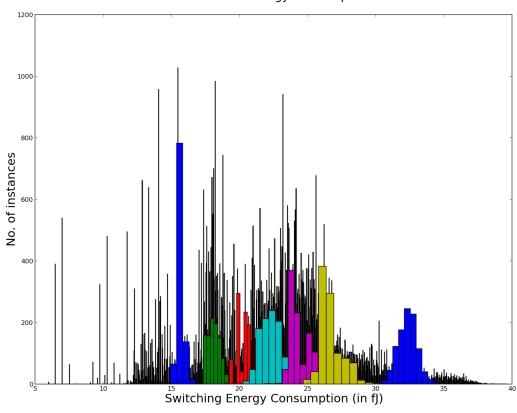

Figure 4.8: Histograms of impact of process variation for specific input vector pairs on total switching energy for Booth Multiplier circuit at  $45\,\mathrm{nm}$  technology. SDF file is modified 1000 times for each input vector pair.

Figure 4.8 shows the histograms of switching energy distribution for different input vector pairs due to process variation. The different colored histograms correspond to switching energy variation with just process variation for different input vector pairs. The overall distribution of switching energy due to the combined effects of process variation and input stimuli variation is also shown in the background in black color. This figure not only indicates that the variation in switching energy due to process variation is a normal distribution for every input vector pair but also that the overall distribution of switching energy is a superposition of many small normal distributions for several input vector-pairs (where the mean of power distribution of all the input-vector pairs spans over a wide range).

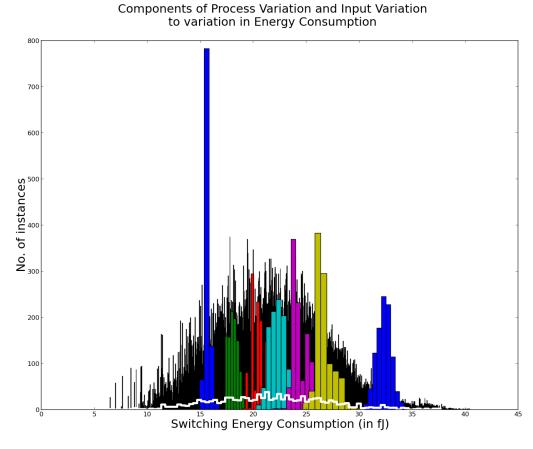

Figure 4.9: Histograms of impact of process variation versus input variation on total switching energy for Booth Multiplier circuit at  $45\,\mathrm{nm}$  technology. SDF file is modified 1000 times for each input vector pair to identify impact of process variation. 1000 input vector pairs are applied to the circuit and simulated using standard SDF file to identify impact of input variation. Outline of impact input variation (for a particular SDF file) is shown in white.

Figure 4.9 shows the impact of process variation versus impact of variation in input stimuli on total switching energy consumption of the circuit. The impact of variation

in input stimuli (for a particular SDF file) on switching energy of the circuit is plotted in white and superimposed on the histograms of the impact of process variation. We can see that the standard deviation for power distribution with input variations (for one SDF file) is much greater than that of power distribution with process variation (for one input vector pair).

The standard deviation of total switching energies of the circuit for one input vector pair and 1000 modifications of the SDF file is computed. This value of standard deviation signifies the impact of process variation on total switching energy of the circuit (for one applied input vector pair). This process is repeated for 1000 input vector pairs. The maximum and average of all the obtained values of standard deviation are computed for both the circuits across the two technologies ( $45 \, \mathrm{nm}$  and  $250 \, \mathrm{nm}$ ).

Table 4.2 shows the maximum and average of all the standard deviation values obtained by the process explained above. The table also shows the range of total switching energy of the circuits. From the values of maximum standard deviation mentioned in the table, we infer that for some input vector pairs, there is a significant impact of process variation on switching energy. Since the difference between average and maximum values indicated in the table is small, we infer that there is definitely a significant impact of process variation on switching energy for every applied input vector pair.

Table 4.2: Standard deviation of distribution of switching energy due to process variation on Booth Multiplier and C880 circuits using  $45\,\mathrm{nm}$  and  $250\,\mathrm{nm}$  technology library

| Circuit    | Technology       | Maximum            | Average            |

|------------|------------------|--------------------|--------------------|

|            |                  | standard deviation | standard deviation |

| Booth      | $45\mathrm{nm}$  | 124.21 fJ          | 115.96 fJ          |

| Multiplier |                  |                    |                    |

| Booth      | $250\mathrm{nm}$ | $5.63\mathrm{pJ}$  | $5.37\mathrm{pJ}$  |

| Multiplier |                  |                    |                    |

| C880       | $45\mathrm{nm}$  | 67.19 fJ           | 63.33 fJ           |

| C880       | $250\mathrm{nm}$ | $5.32\mathrm{pJ}$  | $5.16\mathrm{pJ}$  |