# MODELING OF CHARGES AND CAPACITANCES IN SOI-LDMOS TRANSISTORS

A Project Report

submitted by

#### PRASAD SARANGAPANI

in partial fulfilment of the requirements

for the award of the degree of

BACHELOR OF TECHNOLOGY (ELECTRICAL ENGINEERING)

and

MASTER OF TECHNOLOGY

(MICROELECTRONICS AND VLSI DESIGN)

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS.

MAY 2013

# THESIS CERTIFICATE

This is to certify that the thesis titled **Modeling of Charges and Capacitances in SOI-LDMOS Transistors**, submitted by **Prasad Sarangapani**, to the Indian Institute of Technology, Madras, for the award of the degree of **Master of Technology and Bachelor of Technology (Dual Degree)**, is a bona fide record of the research work done by him under our supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

**Prof. Amitava Dasgupta**

Research Guide Professor Dept. of Electrical Eng. IIT-Madras, 600 036

Place: Chennai

Date: July 7, 2013

**Prof. Anjan Chakravorty**

Research Guide Associate Professor Dept. of Electrical Eng. IIT-Madras, 600 036 Prof. Nandita Dasgupta

Research Guide Professor Dept. of Electrical Eng. IIT-Madras, 600 036

## **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my mentors Dr. Amitava Dasgupta, Dr. Anjan Chakravorty and Dr. Nandita Dasgupta, without whose able guidance this project would not have been possible. Key ideas of this thesis are due to the weekly brainstorming sessions with them. I am indebted to Dr. Anjan Chakravorty for patiently listening to my problems and providing insights and ideas to solve them.

I would like to thank Mr. Ujwal Radhakrishna whose thesis has been taken as a basis for the work in this thesis. Despite his busy schedule at MIT, he not only answered my doubts through mails and phone calls, but also ran simulations and gave me some crucial parameter values for Verilog-A. I would also like to thank Ms. Noel Augustine for teaching me Verilog-A and Spectre, Mr. G. Vijaya Kumar for the useful discussions that we had on LDMOS modeling and for teaching me the nuances of IPE editor and for Mr. Khamesh Kumar for helping me out with MEDICI simulations.

I am deeply indebted to my friends Vignesh, Siddharth, Sudharshan, Abhishek, Bhargava, Bharath and Numaan a.k.a The Gangs of VLSIpur, Bharath Kumar, Karthik Ram and Vasuki for making my five years of stay at IIT-Madras memorable and enjoyable. They have not only helped me during the crucial stages of my academic life and also been part of infinite treat sessions and birthday bashes which I will remember forever.

All this would not have been possible without the support and encouragement of my father, mother and sister who have played a pivotal role throughout my life. I am greatly indebted to them. Finally, I would like to thank the Almighty for making everything possible.

**ABSTRACT**

KEYWORDS: LDMOS; Compact Modeling; Capacitances; Charge Partition.

Lateral double diffused MOSFET (LDMOS) has garnered a lot of interest these days

due to its ease of integration with low voltage circuitry to form high voltage integrated

circuits (HVICs), capable of handling hundreds of volts. Designing HVICs require

accurate LDMOS models capable of predicting parameters over wide ranges of voltages

and temperatures. In recent years, LDMOS has been integrated into RF circuits and this

calls for accurate prediction of DC and high frequency behavior. Hence modeling DC

static currents and capacitances is essential.

In this thesis, a physics based compact model for SOI-LDMOS is presented which

aims to accurately predict various capacitances and static currents in the device. Various

capacitances are realized by modeling the charges present in the device and by parti-

tioning them across various terminals. MM20 HVMOS is a standard LDMOS model

which provides a partitioning scheme in LDMOS known as Modified Ward-Dutton par-

tition. Arguing from continuity and current equations, we show that such a partition

function will be physically inconsistent and provide an alternative partition function for

LDMOS.

Comparison of the model with device simulation show that the model exhibits rea-

sonable accuracy over a wide range of bias voltages. Several reasons are provided for

the inaccuracies in the capacitance plots and methods are proposed to mitigate them.

ii

# TABLE OF CONTENTS

| A  | ACKNOWLEDGEMENTS                   |                              |                                          |    |  |  |  |  |  |  |  |

|----|------------------------------------|------------------------------|------------------------------------------|----|--|--|--|--|--|--|--|

| Al | ABSTRACT                           |                              |                                          |    |  |  |  |  |  |  |  |

| Ll | LIST OF FIGURES ABBREVIATIONS      |                              |                                          |    |  |  |  |  |  |  |  |

| Al |                                    |                              |                                          |    |  |  |  |  |  |  |  |

| N  | NOTATION                           |                              |                                          |    |  |  |  |  |  |  |  |

| 1  | INT                                | INTRODUCTION                 |                                          |    |  |  |  |  |  |  |  |

|    | 1.1                                | Overvi                       | iew of power semiconductor devices       | 1  |  |  |  |  |  |  |  |

|    | 1.2                                | Curren                       | nt scenario in LDMOS transistor modeling | 2  |  |  |  |  |  |  |  |

|    | 1.3                                | Object                       | ives                                     | 4  |  |  |  |  |  |  |  |

|    | 1.4                                | Structu                      | are of the thesis                        | 4  |  |  |  |  |  |  |  |

| 2  | ANA                                | ANALYSIS OF PHYSICAL EFFECTS |                                          |    |  |  |  |  |  |  |  |

|    | 2.1                                | Device                       | Structure                                | 5  |  |  |  |  |  |  |  |

|    | 2.2                                | Static                       | Currents                                 | 7  |  |  |  |  |  |  |  |

|    |                                    | 2.2.1                        | Potential drop in Reg-I                  | 8  |  |  |  |  |  |  |  |

|    |                                    | 2.2.2                        | Potential drop in Reg-II                 | 8  |  |  |  |  |  |  |  |

|    |                                    | 2.2.3                        | Potential drop in Reg-III                | 9  |  |  |  |  |  |  |  |

|    | 2.3                                | Region                       | nal Charges                              | 10 |  |  |  |  |  |  |  |

| 3  | MODEL AND VERILOG-A IMPLEMENTATION |                              |                                          |    |  |  |  |  |  |  |  |

|    | 3.1                                | Static                       | current model                            | 16 |  |  |  |  |  |  |  |

|    |                                    | 3.1.1                        | Formulation of current in channel region | 17 |  |  |  |  |  |  |  |

|    |                                    | 3.1.2                        | Formulation of current under gate oxide  | 19 |  |  |  |  |  |  |  |

|    |                                    | 3.1.3                        | Formulation of current under field oxide | 21 |  |  |  |  |  |  |  |

|    | 3.2                                | Charge model                 |                                          |    |  |  |  |  |  |  |  |

|    |                                    | 3.2.1                        | Ward-Dutton (WD) Partitioning Scheme     | 23 |  |  |  |  |  |  |  |

|   |     | 3.2.2   | Modified Ward-Dutton (MWD) partitioning scheme    | 25 |

|---|-----|---------|---------------------------------------------------|----|

|   |     | 3.2.3   | Formulation of charge in channel region           | 31 |

|   |     | 3.2.4   | Formulation of charge in drift region             | 33 |

| 4 | RES | SULTS A | AND DISCUSSION                                    | 36 |

|   |     | 4.0.5   | Static LDMOS currents                             | 36 |

|   |     | 4.0.6   | LDMOS Charges and Capacitances                    | 37 |

|   |     | 4.0.7   | Transient Currents                                | 47 |

|   |     | 4.0.8   | Reasons for inaccuracies in the capacitance plots | 51 |

| 5 | CO  | NCLUS   | IONS AND SCOPE FOR FUTURE WORK                    | 54 |

|   | 5.1 | Findin  | gs of the thesis                                  | 54 |

|   | 5.2 | Scope   | for future work                                   | 55 |

| A | MO  | DEL PA  | ARAMETERS                                         | 56 |

| В | ME  | DICI SO | OURCE CODE                                        | 57 |

| C | VEF | RILOG-  | -A SOURCE CODE                                    | 59 |

# LIST OF FIGURES

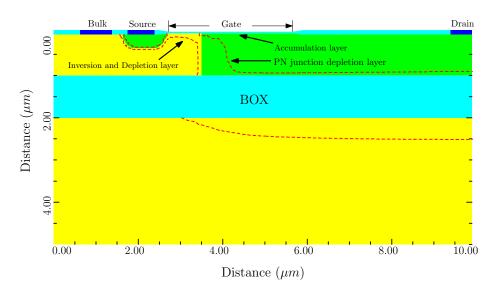

| 2.1 | Schematic of cross section of SOI-LDMOS                                                                        | 6  |

|-----|----------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Doping profile of device along $Si - SiO_2$ interface                                                          | 7  |

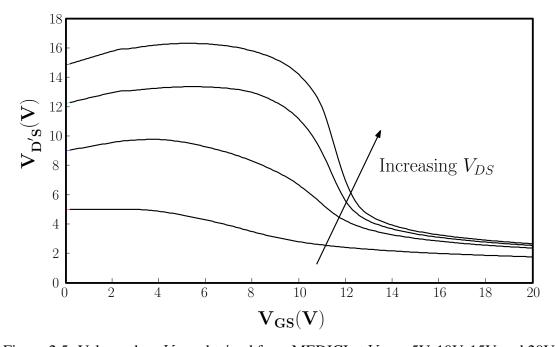

| 2.3 | $I_d - V_{DS}$ plots simulated for $V_{GS}$ = 5V, 10V, 15V and 20V, in MEDICI.                                 | 8  |

| 2.4 | Voltage drop $V_{DiS}$ obtained from MEDICI at $V_{DS}$ = 5V, 10V, 15V and 20V                                 | 11 |

| 2.5 | Voltage drop $V_{D'S}$ obtained from MEDICI at $V_{DS}$ = 5V, 10V, 15V and 20V                                 | 11 |

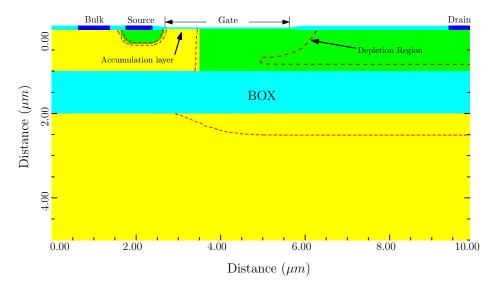

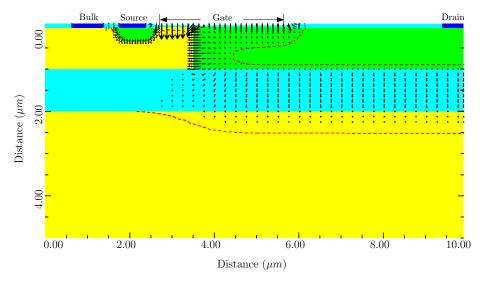

| 2.6 | Depletion Regions for $V_{GS}$ of -1 V and $V_{DS}$ of 10 V                                                    | 12 |

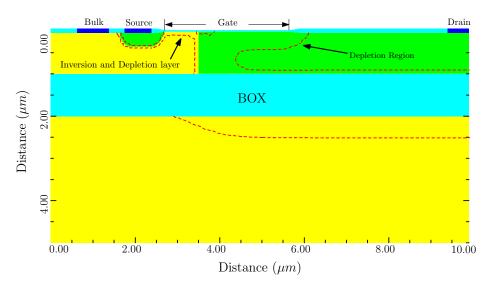

| 2.7 | Depletion Regions for $V_{GS}$ of 5 V and $V_{DS}$ of 10 V                                                     | 12 |

| 2.8 | Depletion Regions for $V_{GS}$ of 7 V and $V_{DS}$ of 10 V                                                     | 13 |

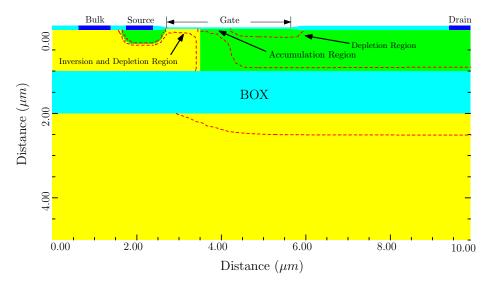

| 2.9 | Depletion Regions for $V_{GS}$ of 10 V and $V_{DS}$ of 10 V                                                    | 13 |

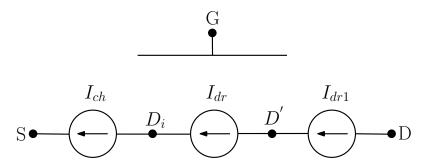

| 3.1 | EC Model for static MOSFET currents                                                                            | 16 |

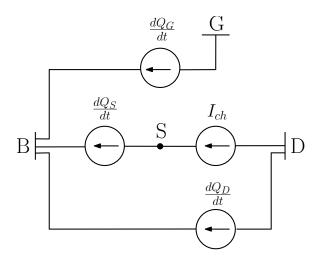

| 3.2 | EC Model for static and dynamic currents in NMOSFET                                                            | 25 |

| 3.3 | EC Model for static and dynamic MOSFET currents - MM20                                                         | 27 |

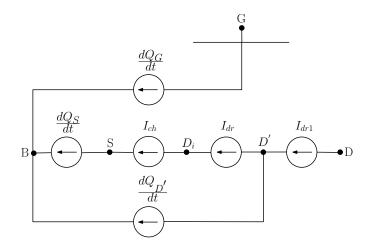

| 3.4 | EC Model for static and dynamic MOSFET currents                                                                | 30 |

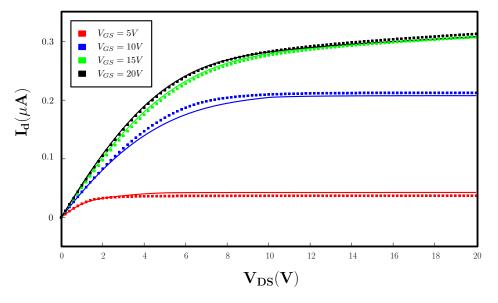

| 4.1 | Comparison of $I_D - V_{DS}$ plots simulated for $V_{GS} = 5$ , 10, 15 and 20 V, in MEDICI with the model      | 36 |

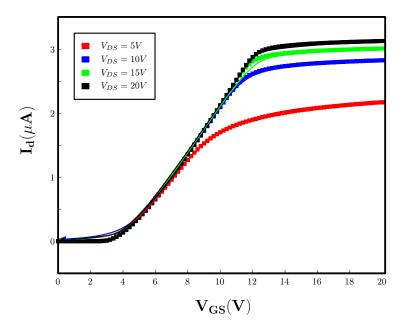

| 4.2 | Comparison of $I_D - V_{GS}$ plots simulated for $V_{DS} = 5$ , 10, 15 and 20 V, in MEDICI with the model      | 37 |

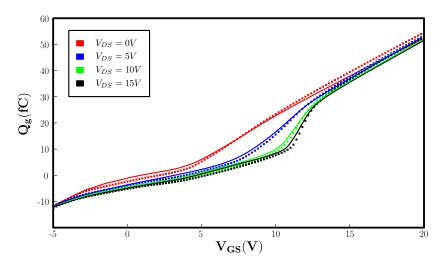

| 4.3 | Comparison of $Q_G - V_{GS}$ plots simulated for $V_{DS} = 0$ , 5, 10 and 15, in MEDICI with the model         | 38 |

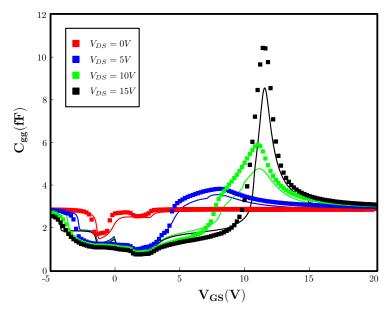

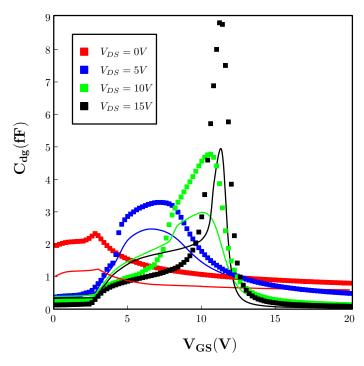

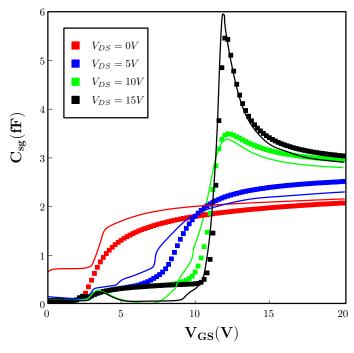

| 4.4 | Comparison of $C_{GG} - V_{GS}$ plots simulated for $V_{DS} = 0$ , 5, 10 and 15, in MEDICI with the model      | 39 |

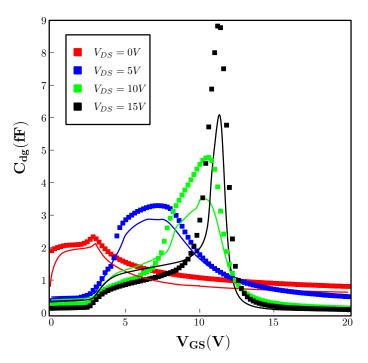

| 4.5 | Comparison of $C_{DG} - V_{GS}$ plots simulated for $V_{DS} = 0$ , 5, 10 and 15, in MEDICI with the model      | 39 |

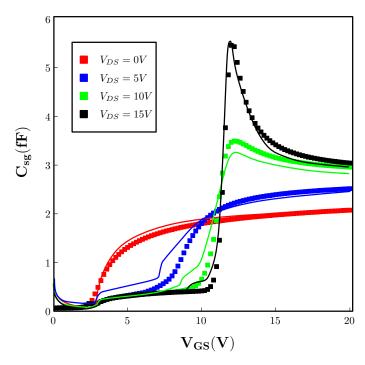

| 4.6 | Comparison of $C_{SG} - V_{GS}$ plots simulated for $V_{DS} = 0$ , 5, 10 and 15, in MEDICI with the model      | 40 |

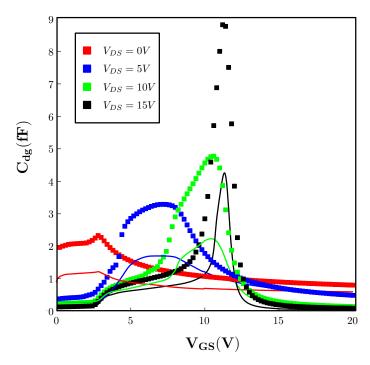

| 4.7 | Comparison of $C_{DG}-V_{GS}$ plots simulated for $V_{DS}=0,5,10$ and 15, in MEDICI with the MM20 model        | 41 |

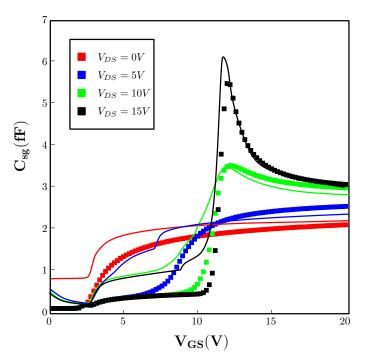

| 4.8 | Comparison of $C_{SG} - V_{GS}$ plots simulated for $V_{DS} = 0$ , 5, 10 and 15, in MEDICI with the MM20 model | 41 |

| 4.9  | Comparison of $C_{DG} - V_{GS}$ plots simulated for $V_{DS} = 0$ , 5, 10 and 15, in MEDICI with the modification done to MM20 model | 42 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.10 | Comparison of $C_{SG}-V_{GS}$ plots simulated for $V_{DS}=0$ , 5, 10 and 15, in MEDICI with the modification done to MM20 model     | 42 |

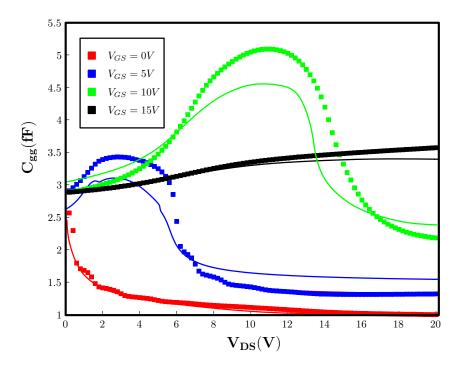

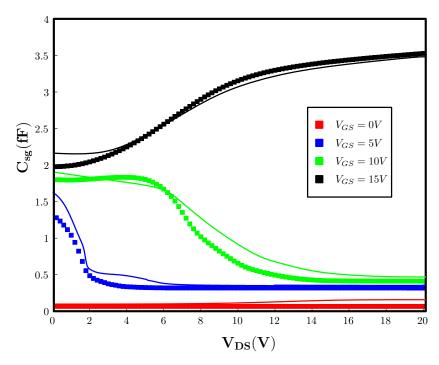

| 4.11 | Comparison of $C_{GG} - V_{DS}$ plots simulated for $V_{GS} = 0$ , 5, 10 and 15, in MEDICI with the model                           | 43 |

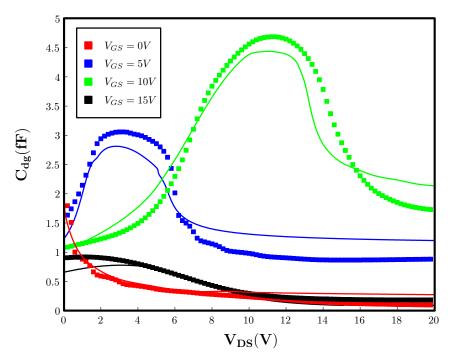

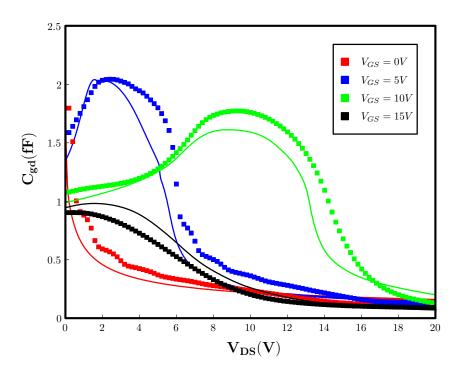

| 4.12 | Comparison of $C_{DG}-V_{DS}$ plots simulated for $V_{GS}=0$ , 5, 10 and 15, in MEDICI with the model                               | 43 |

| 4.13 | Comparison of $C_{SG}-V_{DS}$ plots simulated for $V_{GS}=0,5,10$ and 15, in MEDICI with the model                                  | 44 |

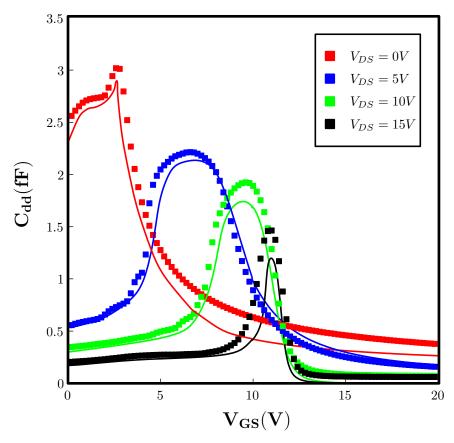

| 4.14 | Comparison of $C_{DD}-V_{GS}$ plots simulated for $V_{DS}=0, 5, 10$ and 15, in MEDICI with the model                                | 44 |

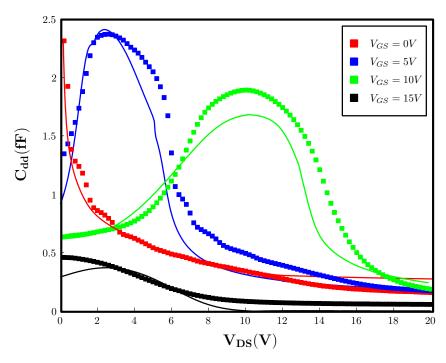

| 4.15 | Comparison of $C_{DD}-V_{DS}$ plots simulated for $V_{GS}=0$ , 5, 10 and 15, in MEDICI with the model                               | 45 |

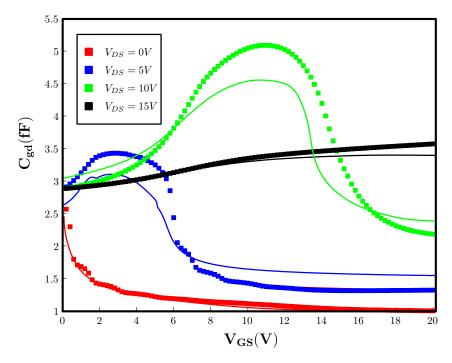

| 4.16 | Comparison of $C_{GD}-V_{GS}$ plots simulated for $V_{DS}=0$ , 5, 10 and 15, in MEDICI with the model                               | 45 |

| 4.17 | Comparison of $C_{GD} - V_{DS}$ plots simulated for $V_{GS} = 0$ , 5, 10 and 15, in MEDICI with the model                           | 46 |

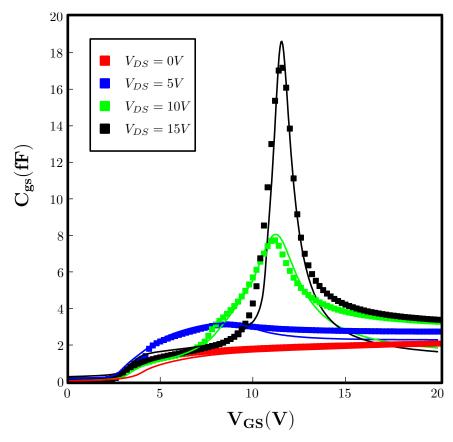

| 4.18 | Comparison of $C_{GS}-V_{GS}$ plots simulated for $V_{DS}=0,5,10$ and 15, in MEDICI with the model                                  | 46 |

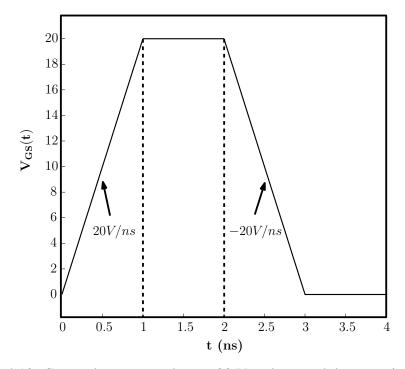

| 4.19 | Gate voltage ramped up to $20\ V$ and ramped down again to $0\ V$                                                                   | 47 |

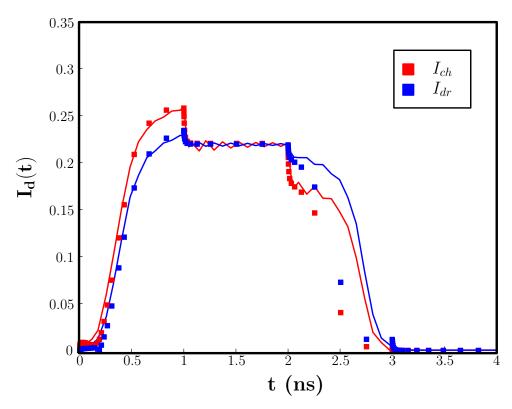

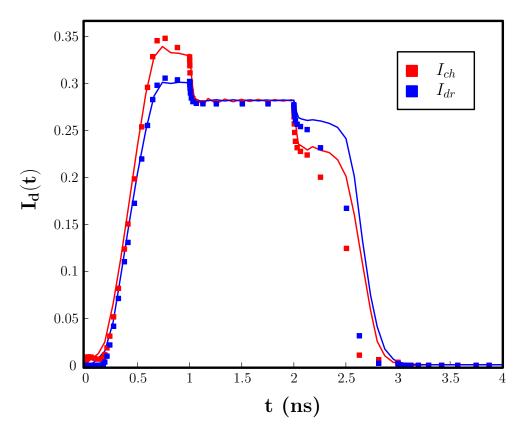

| 4.20 | Response of $I_{ch}$ and $I_{dr}$ when $V_{GS}$ is ramped up and ramped down keeping $V_{DS}$ =5V                                   | 48 |

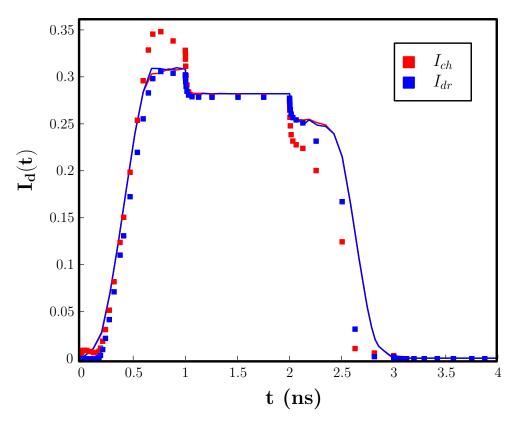

| 4.21 | Response of $I_{ch}$ and $I_{dr}$ when $V_{GS}$ is ramped up and ramped down keeping $V_{DS}$ =10V                                  | 48 |

| 4.22 | Response of $I_{ch}$ and $I_{dr}$ from MM20 model when $V_{GS}$ is ramped up and ramped down keeping $V_{DS}$ =10V                  | 49 |

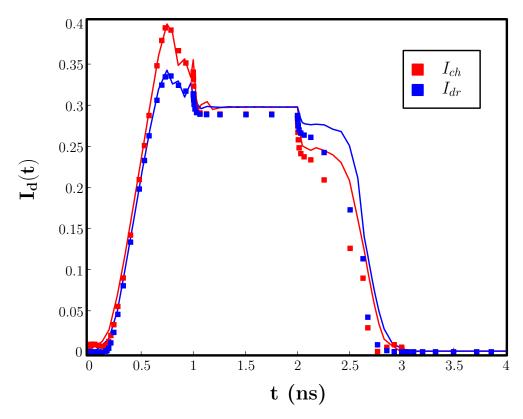

| 4.23 | Response of $I_{ch}$ and $I_{dr}$ when $V_{GS}$ is ramped up and ramped down keeping $V_{DS}$ =15V                                  | 50 |

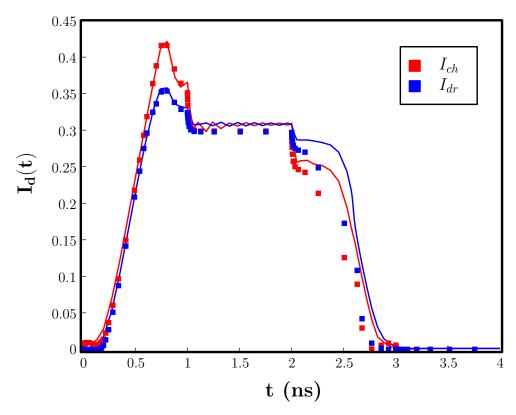

| 4.24 | Response of $I_{ch}$ and $I_{dr}$ when $V_{GS}$ is ramped up and ramped down keeping $V_{DS}$ =20V                                  | 50 |

| 4 25 | Flectric Field lines for $V_{GG}$ of 4 V and $V_{DG}$ of 10 V                                                                       | 52 |

# **ABBREVIATIONS**

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor

**SOI** Silicon On Insulator

**BOX** Buried Oxide

**LDMOS** Lateral Double Diffused MOS

**VDMOS** Vertical Double Diffused MOS

**HVIC** High Voltage Integrated Circuit

**RFIC** Radio Frequency Integrated Circuit

**JFET** Junction Field Effect Transistor

NMOS N-channel MOSFET

**PMOS** P-channel MOSFET

**DC** Direct Current

**AC** Alternating Current

**WD** Ward-Dutton

MWD Modified Ward-Dutton

#### **NOTATION**

$V_{GS}$  Gate to source voltage  $V_{GB}$  Gate to bulk voltage

$V_{GC}$  Gate to quasi-Fermi level voltage

$V_{DS}$  Drain to source voltage  $V_{DiS}$  Voltage drop across channel

$V_{D'D_i}$  Voltage drop across drift region under gate oxide  $V_{DD'}$  Voltage drop across drift region under field oxide

$V_{sat,ch}$  Channel saturation voltage  $V_{sat,dr}$  Reg-II saturation voltage

$V_{DiS,eff}$  Effective voltage drop in channel  $V_{D'D_i,eff}$  Effective voltage drop in Reg-II

$I_{DS}$  Drain to source current  $I_{ch}$  Channel region current  $I_{dr}$  Current in Reg-II  $I_{dr1}$  Current in Reg-III

$L_{ch}$  Length of channel region

$L_{dr}$  Length of Reg-II Length of Reg-III W Width of LDMOS  $C_{ox}$  Oxide capacitance  $t_{ox}$  Oxide thickness

A Cross section area of LDMOS

$t_{si}$  Silicon film thickness  $t_{BOX}$  Thickness of buried oxide  $N_{dr}$  Doping concentration in Reg-II

$V_T$  Thermal voltage  $\epsilon_{si}$  Permittivity of silicon  $\psi_s^{ch}$  Surface potential in channel  $\psi_s^{dr}$  Surface potential in Reg-II

$Q_{inv}$  Inversion charge per unit area in Reg-I

$Q_{gate}^{ch}$  Gate charge in Reg-I

$Q_{n}^{dr}$  Total drift charge per unit area in Reg-II  $Q_{acc}^{dr}$  Accumulation charge per unit area in Reg-II  $Q_{dep}^{dr}$  Depletion charge per unit area in Reg-II Inversion charge per unit area in Reg-II

$Q_{gate}^{dr}$  Gate charge in Reg-II  $n_{ch}$  Charge density in Reg-II  $n_{dr}$  Charge density in Reg-II

$Q_G$  Charge assigned to gate terminal  $Q_D$  Charge assigned to drain terminal  $Q_S$  Charge assigned to source terminal

$Q_B$  Charge assigned to bulk terminal  $Q_{D_i}$  Charge assigned to  $D_i$  terminal  $Q_{D'}$  Charge assigned to D' terminal

au Time lag between conduction currents in Reg-I and II

$V_{FB}^{ch}$  Flat band voltage in channel  $V_{FB}^{dr}$  Flat band voltage in Reg-II  $v_{sat}$  Saturation velocity of electrons  $\mu_{ch}$  Effective mobility in channel  $\mu_{dr}$  Effective mobility in Reg-II  $\mu_{dr1}$  Zero field mobility in Reg-III

Velocity saturation parameter in channel  $\theta_{3,ch}$  $\theta_1$ Channel mobility reduction parameter  $\theta_2$ Channel mobility reduction parameter  $\theta_{3,dr}$ Velocity saturation parameter in Reg-II Velocity saturation parameter in Reg-III  $\theta_{dr1}$  $\theta_{1,dr1}$ Velocity saturation parameter in Reg-III  $\lambda_{ch}$ Channel length modulation parameter Drift length modulation parameter  $\lambda_{dr1}$  $C_{ij}$ Capacitance between terminals i and j

# **CHAPTER 1**

#### INTRODUCTION

# 1.1 Overview of power semiconductor devices

Power semiconductor devices have become industry's choice today in designing high voltage integrated circuits (HVICs). They have come a long way since the inception of bipolar junction transistors and thyristors. They were initially introduced by Texas Instruments in 1954 but it took almost a decade for them to find practical applications in high voltage circuits. Thyristors were the first class of power devices but they had the disadvantage of poor switching speed and difficulty of integration. Advances in silicon fabrication technology let to the development of novel device structures such as power MOSFETs. These devices were introduced in late seventies (Adler *et al.*, 1984) and they paved way for the development of new generation of devices. The power MOSFETs were developed by converting a conventional MOSFET into an asymmetric device to improve the reverse blocking capability of the device(Declercq and Plummer, 1976). This ultimately led to the creation of lateral double diffused metal oxide semiconductors (LDMOS) transistors.

One of the main advantages of LDMOS devices is that they can be easily integrated with low voltage circuitry and continue to be industry standard even today for medium voltage power applications. On the other hand, they suffer from low current rating and breakdown voltage on-resistance trade off. To increase the voltage handling capabilities of this device, one has to increase the length of lightly doped drain region across which the reverse voltage is dropped. This increases the area requirements of the device.

To circumvent this problem, vertical double diffused MOS (VDMOS) technology was developed. VDMOS provides larger current ratings and higher breakdown voltage compared to LDMOS(Temple and Gray, 1979), but requires complicated process steps and integration with low voltage circuitry is not easy. Though VDMOS finds applications in high voltage industries, medium power applications are still dominated by LDMOS devices.

Nowadays, HVICs and power integrated circuits (PICs) are replacing discrete elements such as DC-DC converter, switch mode power supplies and power amplifiers (Sakamoto *et al.*, 1999),(Perugupalli *et al.*, 1998),(Tsui *et al.*, 1992). Integration of high and low voltage circuits on the same chip improves the overall performance and reduces the chip size. PICs are used as a bridge between power load and low voltage digital logic(Tsui *et al.*, 1995),(Baliga, 1991). They are also useful in Power line communications (PLCs) where digital information is transmitted over a power line. LDMOS devices form an integral part of many of these interesting applications.

# 1.2 Current scenario in LDMOS transistor modeling

As LDMOS technology is finding its use in interesting consumer and automotive applications, it becomes imperative to model LDMOS transistors. A recent trend is the processing of LDMOS devices on silicon on insulator (SOI) platform. LDMOS fabricated on SOI substrate have several advantages like lower leakage currents, higher latchup, higher packing density and reduced parasitics(Holland and Igic, 2006). SOI enables isolation between power devices and low voltage circuitry which is essential in smart power ICs. Thus compact models for SOI-LDMOS transistors capable of modeling device characteristics over wide range of bias and temperature and for various lengths is essential for a fail safe design of power integrated circuits.

There have been many approaches for modeling LDMOS transistors. Two main approaches followed are (i) macro-modeling and (ii) compact modeling. Macro modeling procedure consists of trying to describe the behavior of device through a circuit consisting of several discrete elements or modules. As the number of effects rises, the number of elements in the circuit increases and results in increase in computation time and convergence problems. There are many existing macro models based on SPICE which consider SPICE models for MOSFETs, JFETS and diodes to model LDMOS(van der Pol et al., 2000),(Darwish, 1986),(Trivedi et al., 1999). One such macro model uses BSIM4 to model the MOSFET and JFET to model drift region and a shorted PMOS transistors to model capacitance behavior of drift region(Yang et al., 2008). These models have a large number of non-physical model parameters.

Compact modeling, on the other hand, maintains device unity through a set of self

consistent expressions which are able to produce device behavior. All internal node equations are solved in the model itself, thereby reducing computation time. Also, the expressions obtained are from physical principles and do away with non-physical parameters introduced in macro-modeling. There are several compact models available for SOI-LDMOS, important among them being HiSIM-HV (Oritsuki *et al.*, 2010), EKV model(Bucher *et al.*, 1998),(Sallese and Porret, 2000),(Chauhan *et al.*, 2006*a*) and MM20 HVMOS model(MM2, 2008). In this thesis, MM20 model developed by NXP semiconductors is used as a basis upon which further formulations have been built. It is a surface potential based model and takes into account channel and drift region under the gate oxide. It does not model the region under field oxide and hence cannot be used for high voltage devices. The effect of quasi-saturation in drift region under field oxide is considered in (Lekshmi *et al.*, 2009).

Apart from accurately predicting the DC characteristics of a device, a good model must also accurately predict various capacitances which are important for the AC characteristics of the device. With the integration of LDMOS in high speed circuits such as RFICs, predicting the high speed performance of LDMOS becomes important. In literature, there have been few detailed studies on modeling capacitances in devices such as LDMOS and SOI-LDMOS and some of them have resulted in model development(Frre et al., 2001),(Aarts et al., 2005),(Shi et al., 2013),(Wang et al., 2013). One of the basic principles used for modeling capacitances is charge partitioning. The charges are modeled accurately and then they are partitioned between different terminals of the device based on Ward-Dutton partition principle(Oh et al., 1980). MM20 model uses a modified version of Ward-Dutton model to obtain various capacitances. It does not clearly explain the basis behind such a partition and charge modeling also has some inherent approximations. Also, the match obtained between the device and model simulations are not satisfactory.

Recently, (Aarts et al., 2004),(Aarts et al., 2006) and (Roy et al., 2007) have shown that in the presence of lateral doping (which is inherently present in LDMOS) and field dependent mobility, it is not possible to obtain a partition function. This poses a big problem in modeling the capacitances. (Aarts et al., 2006) and (Roy et al., 2007) give a procedure to calculate the capacitance based on small signal analysis. Though the analysis is physically consistent, the final expressions obtained are extremely complex to be implemented in a compact model.

Therefore, there is a need for a comprehensive charge model which accounts for aforementioned effects. In this thesis, an extensive model to describe the static and dynamic characteristics of SOI-LDMOS is proposed. MM20 model serves as a starting point for describing various currents and charges in the device. The model considers field dependent mobility reduction, velocity saturation in channel and quasi saturation in the drift region. A modification to the MM20 charge partitioning scheme is proposed and physical reasoning behind such a partition is explained.

# 1.3 Objectives

The main objectives of this thesis are.

- To analyze the behavior of SOI-LDMOS in channel, drift region under gate oxide and drift region under field oxide for various gate and drain bias voltages.

- To analyze the charges present in the device and provide a physics based partition model to partition charges between various terminals.

- To predict various capacitances from the charge model thus developed.

#### 1.4 Structure of the thesis

The thesis is organized as follows.

#### • Chapter 2: Analysis of physical effects

This chapter deals with analysis of voltage drops in different regions along with various charges in the device. The device behavior is analyzed with the help of MEDICI simulation results.

#### • Chapter 3: Model and Verilog-A implementation

In this chapter, compact model to explain these physical effects is proposed. The model uses MM20 model for channel and drift region under gate oxide and quasi-saturation model to model the region under field oxide. The charges are modeled according to MM20 model and a modification to the existing partition model is proposed.

#### • Chapter 4: Results and discussions

Static models and various capacitances are compared with MEDICI simulation results. Various proposals to improve the charge model are proposed.

#### • Chapter 5: Conclusions

Contributions offered by with work are presented. Scope for future work is listed.

#### **CHAPTER 2**

# ANALYSIS OF PHYSICAL EFFECTS

The high voltage lateral MOSFET device, where the extension of the gate electrode works as a field plate, is one of the interesting structures in mainstream HV technologies. The structure of LDMOS is different from conventional MOSFET due to the presence of an extended drain region and non-uniform lateral doping in the channel region which makes its behavior complex compared to the normal MOSFET.

In this chapter, we focus on analyzing the physical effects which appear under static conditions. Firstly, the effect of gate and drain voltages on the static currents are analyzed. This analysis is useful when we explain the current formulations of various regions. Next, various charges that are present in the channel and the drift region will be studied under the application of various gate and drain bias. For the purpose of these studies, commercially available two-dimensional (2-D) device simulator MEDICI (Med, 2003) is used.

#### 2.1 Device Structure

SOI-LDMOS is an asymmetric structure with a drift region located between the channel and the drain terminal. Schematic of the cross-section of device is as shown in Fig 2.1. The channel region is self aligned to the gate and is formed by p-type diffusion creating a p-well under the gate. This results in non-uniform doping in channel with doping concentration gradually decreasing from the source end to the other end of the channel region. The source is then formed by a  $n^+$  diffusion. Since there are two lateral doping processes involved, this device is called as laterally double diffused MOSFET. One should note that the doping of the channel region is not constant throughout and decreases from source side to drain side. This causes complexity in current and charge modeling. The n-drift region sustains the reverse voltage and hence is lightly doped in comparison to channel. Thus, the depletion region at the junction of channel and drift region extends far more into the drift region to sustain high voltages. The gate electrode

covers the surface of the channel and part of the drift region. The gate oxide and the field oxide are of different thickness. A thicker field oxide helps in reducing the gate drain overlap capacitance and improves the speed of the device. The active part of the device is separated from the bulk by a thick buried oxide which improves dielectric isolation and minimizes parasitics.

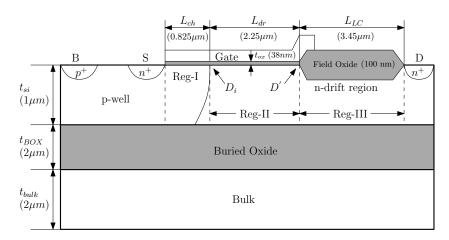

Figure 2.1: Schematic of cross section of SOI-LDMOS.

From the figure it is clear that there are three important regions marked by Reg-I, II and III. Reg-I corresponds to the channel region in the p-well, Reg-II to the drift region with the gate oxide at its surface and Reg-III to the drift region underneath the field oxide. Transition between Reg-I and Reg-II is denoted by  $D_i$  and between Reg-II and Reg-III is denoted by D'.

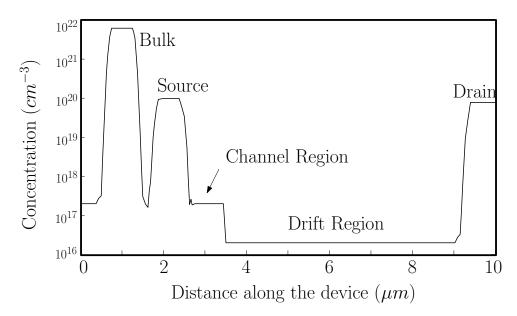

The doping profile of the device along a lateral cutline close to the  $Si-SiO_2$  interface is shown in Fig 2.2. Here we assume that the doping profile in the channel region is uniform though it has a lateral variation in practice. Drift region has the lowest doping to sustain high voltages. For the device under discussion, p-well has a doping concentration of  $2\times 10^{17}~cm^{-3}$ . The drift region has a doping concentration of  $2\times 10^{16}~cm^{-3}$ , ten times lower than the channel region to withstand high voltages. The length of channel region is  $0.825\mu m$ , length of drift region under gate oxide is  $2.25\mu m$  and that under the field oxide is  $3.45\mu m$ . Gate oxide thickness is 38 nm and field oxide thickness is 100 nm. Total length of the device is  $10\mu m$ . Thickness of the active region is  $1\mu m$  and thickness of buried oxide is  $2\mu m$ .

Figure 2.2: Doping profile of device along  $Si - SiO_2$  interface.

# 2.2 Static Currents

In order to provide accurate model for the SOI-LDMOS, its electrical behavior must be thoroughly analyzed and understood. This requires separation of device structure into three distinct regions i.e. Reg-I, II and III. This separation is not physical but only to understand the model better. This helps in modeling the MOSFET currents and forms the basis for understanding various charges present in different regions. During the current and charge analysis, it is assumed that the source and bulk terminals are shorted. Hence,  $V_{GS}$  and  $V_{GB}$ ,  $V_{DS}$  and  $V_{DB}$  are used interchangeably. Current modeling has been dealt in great detail in (Lekshmi, 2009) and (Radhakrishna, 2011). This thesis tries to explain the current modeling in a concise manner and gives some modifications and explanations for better clarity.

When  $V_{GS}$  is greater than the threshold voltage of the channel, electrons are attracted to form an inversion layer<sup>1</sup>. Since there is a gate overlap in the drift region, an accumulation region is formed. Now, if  $V_{DS}$  is applied, electrons move from the source terminal through the inversion layer in Reg-II into Reg-III and will drift through the accumulation region into Reg-III and finally into drain contact.

Potentials drops across Reg-I, II and III are studied to explain the  $I_d - V_{DS}$  charac-

<sup>&</sup>lt;sup>1</sup>Since doping in channel is assumed to be constant, threshold voltage is same throughout the channel. In practice, threshold voltage varies across the channel from source to drain due to lateral doping.

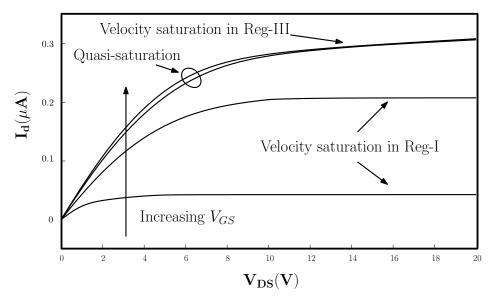

teristics of the device as shown in Fig 2.3.

Figure 2.3:  $I_d - V_{DS}$  plots simulated for  $V_{GS}$  = 5V, 10V, 15V and 20V, in MEDICI.

## 2.2.1 Potential drop in Reg-I

For low values of  $V_{GS}$ , as  $V_{DS}$  is increased, drop across the channel increases. This is because Reg-II is already in accumulation condition and has high conductivity. As  $V_{DS}$  is increased further, the lateral electric field in this region increases and reaches the critical value. Beyond this point, voltage in Reg-I saturates. This is velocity saturation in Reg-I which leads to current saturation. This can be seen in Fig 2.3 for  $V_{GS}$  values of 5 V and 10 V. At high values of  $V_{GS}$ , conductivity of Reg-I and Reg-II is high as these regions are in inversion and accumulation mode respectively. As  $V_{DS}$  is increased, the electric field in Reg-I does not reach the critical value because the voltage drop is really small in this regime. Thus while saturation of current at low values of  $V_{GS}$  is governed by Reg-I, saturation at higher values of  $V_{GS}$  is not governed by Reg-I.

# 2.2.2 Potential drop in Reg-II

For low values of  $V_{GS}$ , when  $V_{DS}$  is increased, drop in Reg-II increases but at a lower rate compared to Reg-I. This is attributed to the high conductivity of the accumulation region. After Reg-I voltage saturates, remaining potential is dropped across Reg-II and in this regime, voltage drop in Reg-II increases at a much faster rate. From this, one can conclude that current saturation at low values of  $V_{GS}$  is governed only by Reg-I and not

by Reg-II. At higher values of  $V_{GS}$ , voltage drop is really low due to high conductivity of this region. Hence, even when  $V_{DS}$  is increased, critical field is never attained in this region.

# 2.2.3 Potential drop in Reg-III

At low values of  $V_{GS}$ , potential drop in Reg-III increases at a reduced slope for lower values of  $V_{DS}$ . However, when  $V_{DS}$  is increased beyond 10 V, the voltage drop rate rises with  $V_{DS}$ . This is because Reg-I would have saturated by then and voltage drop across Reg-II is small. Electric field saturation is not reached at low values of  $V_{GS}$ . When  $V_{GS}$  is increased beyond 10 V, potential drop across Reg-I and II is small and most of the voltage is dropped across Reg-III. When  $V_{DS}$  is increased in this regime, velocity saturation occurs in Reg-III, which leads to current saturation. Any further increase in  $V_{GS}$  will have no effect on current as Reg-III is not affected by the gate terminal (as shown in Fig 2.3 for  $V_{GS}$  values of 15 V and 20 V). This effect is termed as quasi-saturation and is dominant in high voltage LDMOS devices. At high  $V_{GS}$ , velocity saturation occurs at the drain end of Reg-III and with increased  $V_{DS}$  saturation point moves towards source side leading to drift length modulation and slight increase in current.

# 2.3 Regional Charges

In order to get a reasonable model for capacitances<sup>2</sup> in SOI-LDMOS, one must first look at various charges present in the device. Once the charges are modeled properly, capacitances can be derived from them using the relation

$$C_{ij} = (2\delta_{ij} - 1)\frac{\partial Q_i}{\partial V_i}$$

(2.1)

where (i,j) corresponds to set of terminals (D, G, S, B) and  $\delta_{ij}$  is the Kronecker delta. This calls for analyzing the charges in different bias regimes and modeling them appropriately. For current modeling, it was sufficient to look at values of  $V_{GS}$  greater than the threshold voltage. Whereas, for charge modeling one must also model for negative bias voltages<sup>3</sup>. In Reg-I of LDMOS, when  $V_{GS}$  is less than the flatband voltage of the channel  $V_{FB,ch}$ , an accumulation layer of positive charges is created. When  $V_{GS}$  goes beyond  $V_{FB,ch}$ , negative depletion charges are created. Inversion layer of electron appears when the gate voltage goes beyond the threshold voltage of the channel.

In Reg-II, one must note that the reference voltage is not the bulk voltage as the region is not connected to the bulk terminal. Hence one cannot use the same argument above and one must be careful in determining the condition for accumulation, inversion and depletion. The reference voltage in Reg-II is  $V_C$ , the Quasi-Fermi potential which varies from  $V_{DiS}$  at the junction of channel and drift region to  $V_{D'S}$  which is at the junction of Reg-II and Reg-III. Hence, one cannot decide the region of operation without knowing the bias values of internal nodes. When  $V_{GC}$  is less than the flat band voltage of the drift region  $V_{FB,dr}$ , positive depletion charges are present. A positive inversion layer is created only when the bias voltage is a large negative value. When  $V_{GC}$  is greater than  $V_{FB,dr}$ , accumulation layer of electron is created. Since for a given value of  $V_{GS}$  and  $V_{DS}$ ,  $V_C$  varies across the drift region, accumulation and depletion regions can simultaneously exist at different portions of the drift region.

<sup>&</sup>lt;sup>2</sup>By capacitances, we mean the small signal capacitances defined between various terminals.

$<sup>^3</sup>C_{gg}$  for a MOSFET/LDMOS in the negative  $V_{GS}$  regime acts as a constant value capacitor and is used in ICs where bias independent capacitance is needed. Hence, one also models for negative bias voltages so as to accurately predict those constant capacitance values.

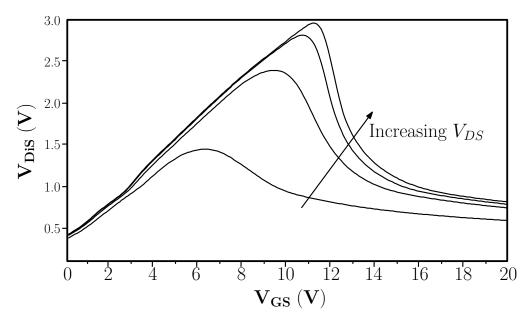

Figure 2.4: Voltage drop  $V_{DiS}$  obtained from MEDICI at  $V_{DS}$  = 5V, 10V, 15V and 20V.

Figure 2.5: Voltage drop  $V_{D'S}$  obtained from MEDICI at  $V_{DS}$  = 5V, 10V, 15V and 20V.

Fig 2.4 and 2.5 show the variation of  $V_{DiS}$  and  $V_{D'S}$  as a function of  $V_{GS}$  for various values of  $V_{DS}$ . From these two figures, one can observe that for a given value of  $V_{GS}$ , the quasi-Fermi potential  $V_C$  is higher in the case of  $V_{D'S}$  than  $V_{DiS}$ . This implies that the potential drop  $V_{GC}$  would be more negative in region near D' than  $D_i$ . Therefore, when  $V_{GS}$  is increased, the region near  $D_i$  will develop an accumulation layer first and then this accumulation layer will spread to other regions of Reg-II as  $V_{GS}$  rises further.

Figure 2.6: Depletion Regions for  $V_{GS}$  of -1 V and  $V_{DS}$  of 10 V.

Figure 2.7: Depletion Regions for  $V_{GS}$  of 5 V and  $V_{DS}$  of 10 V.

Fig 2.6 shows the depletion layers in the device when  $V_{GS}=-1~{\rm V}$  and  $V_{DS}=10~{\rm V}$ . Since the gate voltage is less than the flatband voltage in the channel region an accumulation region is created. Similarly, in the drift region a depletion region exists as  $V_{GC}$  is less than the flatband voltage of the drift region. When  $V_{GS}=5~{\rm V}$ , inversion layer is created in the channel region. Drift region, on the other hand is still in depletion mode as  $V_{GC} < V_{FB,dr}$  even when the gate voltage is 5 V. This is evident from Fig 2.7.

Figure 2.8: Depletion Regions for  $V_{GS}$  of 7 V and  $V_{DS}$  of 10 V.

Figure 2.9: Depletion Regions for  $V_{GS}$  of 10 V and  $V_{DS}$  of 10 V.

Now, when  $V_{GS}=7$  V, drift region near the channel goes into accumulation mode whereas the region near field oxide is still in depletion mode. This is because  $V_{GC}>V_{FB,dr}$  near the channel region but  $V_{GC}< V_{FB,dr}$  near the field oxide region as seen in Fig 2.8. If the gate voltage is increased further to 10 V,  $V_{GC}>V_{FB,dr}$  throughout the drift region. Hence, the drift region is completely in accumulation mode now as shown in Fig 2.9.

Charges in Reg-III can be neglected due to the thick field oxide present. Due to the thickness of this oxide, this region is not affected by variations in the gate voltage. It merely acts as a resistor whose value depends on the mobility and the doping concentration of the region. Apart from charges present in Reg-I and II, one must also pay attention to the depletion region formed at the junction of channel and drift region. Any

variation in gate or drain voltage affects the quasi-Fermi level in the drift region, which in turn changes the depletion charge concentration. This variation of charge in the p-n junction with respect to gate/drain voltage can contribute to the capacitance term which needs to be accounted for. From the analysis carried out in this chapter, the following conclusions can be made

- MOSFET current saturation is due to velocity saturation in Reg-I at lower  $V_{GS}$  and due to quasi-saturation at higher  $V_{GS}$ .

- In Reg-I, positive accumulation charges are present when  $V_{GB} < V_{FB,ch}$  and negative inversion and depletion charges are present when  $V_{GB} > V_{FB,ch}$ .

- In Reg-II, positive depletion charges are present when  $V_{GC} < V_{FB,dr}$  and negative accumulation charges are present when  $V_{GC} > V_{FB,dr}$ .

- Reg-III need not be taken into consideration for charge modeling. The depletion charges present in the junction between channel and drift region must be taken into account.

#### **CHAPTER 3**

#### MODEL AND VERILOG-A IMPLEMENTATION

A comprehensible model for any device must be capable of predicting the device performance over a wide range of biases, temperatures and device geometries. Since SOI-LDMOS forms an integral part of HVICs, accurate modeling of these devices is necessary to ensure fail-safe design of HVIC circuits.

Any LDMOS model must have the following features:

- Accurate modeling of AC/DC terminal currents and the nodal charges in linear, saturation and off modes.

- Continuity of device models in different regions and continuity in their derivatives and double derivatives<sup>1</sup>.

- Conservative nature of charge model.

- Accurate modeling of capacitances to predict the dynamic behavior of the device.

- Modeling high frequency behavior where device operates in Non-Quasi static regime.

- Capability to model impact ionization and snapback and in turn predict SOA.

- Capability to model self heating which requires temperature dependence of model parameters.

- Modeling various types of noise i.e. 1/f noise, thermal noise etc.

- Scalability of the model over wide range of bias, geometries and temperatures.

Among the models available for LDMOS, one can separate them into two distinct categories - macro modeling and compact modeling. Macro model describes the behavior of the device by treating it as a combination of several discrete circuit elements. As the number of physical effects needed to model increases, the number of discrete elements also increases. This results in increase in the number of internal nodes of the device. This not only increases the computational cost but may also result in convergence issues. On the other hand, compact modeling accurately describes the device

<sup>&</sup>lt;sup>1</sup>Needed to model harmonic distortion.

behavior through a set of self consistent expressions. Since the internal nodes present in the device are solved in the model itself while solving the self consistent expressions, there is a significant reduction in computation time. Also, these expressions are derived from physical principles and can accurately predict certain phenomenon like quasi-saturation, snapback. Hence, compact modeling is preferred over macro modeling.

In this chapter, a comprehensive static and dynamic model of SOI-LDMOS is presented. The model provides an improvement over one of the currently existing compact models, MM20 model. The model incorporates surface potential based approach to model MOS transistor current and charges and accurately predicts in all regions of operations such as accumulation, depletion and inversion. It also provides a modified partition function to partition the charges to get a better model for various capacitances.

# 3.1 Static current model

The MOSFET current is affected by Reg-I, Reg-II and Reg-III of the device. The MOSFET current is modeled using three current sources (Lekshmi, 2009), (Radhakrishna, 2011) as shown in Fig 3.1. Here,  $I_{ch}$  is the current in the channel which is a function of the potential drop,  $V_{DiS}$ . The potential drop across Reg-II is given by  $V_{D'Di}$  and it determines the current flowing through Reg-II, given by  $I_{dr}$ . The current through Reg-III is  $I_{dr1}$  and it is a function of the potential drop across Reg-III, given by  $I_{DD'}$ . The current source models are explained in the following subsections.

Figure 3.1: EC Model for static MOSFET currents.

#### 3.1.1 Formulation of current in channel region

Channel current is modeled using a surface potential approach. The drift and diffusion components of the current are altogether given by

$$I_{ch} = \frac{W\mu_{ch}}{L_{ch}} \left( \int_{\psi_{s,0}}^{\psi_{s,L}} (-Q_{inv}) d\psi_s + V_T (Q_{inv,L} - Q_{inv,0}) \right)$$

(3.1)

where W is the channel width,  $\mu_{ch}$  is the channel mobility taking into account the effect of lateral and vertical electric fields.  $L_{ch}$  is the channel length,  $\psi_s$  is the surface potential,  $V_T$  is the thermal voltage and  $Q_{inv}$  is the inversion charge per unit area given as  $Q_{inv} = -C_{ox}V_{inv}$  with  $Q_{inv,0}$  and  $Q_{inv,L}$  being the inversion charges at the source and the drain  $(D_i)$  terminals. Inversion potential  $V_{inv}$  is given by

$$V_{inv} = V_{GB} - V_{FB,ch} - \psi_s - k_{ch}\sqrt{\psi_s}$$

(3.2)

where  $V_{GB}$  is the applied gate to bulk voltage,  $V_{FB,ch}$  is the flatband voltage of the channel region and  $k_{ch}$  is the channel body effect coefficient. If we use the above expression for  $V_{inv}$  to obtain the channel current, one would not be able to express the current term completely in terms of the potential drop  $V_{DiS}$ . This is due to the square root term present in the equation. Hence, one desires to linearize  $V_{inv}$  with respect to some potential.  $\psi_{s,o}$ , the surface potential at the source side is chosen as a reference and  $V_{inv}$  is approximated with respect to that. Upon linearizing we get

$$V_{inv} = V_{inv,0} - \zeta \left( \psi_s - \psi_{s,0} \right) \tag{3.3}$$

with  $\zeta = \left(1 + \frac{k_{ch}}{2\sqrt{\psi_{s,0}}}\right)$  and the inversion potential on the source side is given by

$$V_{inv,0} = V_{inv} \mid_{\psi_s = \psi_{s,0}} = V_{GB} - V_{FB,ch} - \psi_{s,0} - k_{ch} \sqrt{\psi_{s,0}} + m_{DIBL} V_{DiS}$$

(3.4)

where  $\psi_{s,0} = 2V_T ln \left(\frac{N_{ch}}{n_i}\right)^2$ ,  $N_{ch}$  is doping concentration of the channel and  $n_i$  is the intrinsic carrier concentration.  $m_{DIBL}$  accounts for drain induced barrier lowering (applicable only in the case of short channel). Using (3.2), (3.3) and (3.4), (3.1) can be

When  $V_{GB}$  is beyond the threshold voltage of the channel one can approximately write  $\psi_{s,0} = 2\phi_f + V_{SB}$ , where  $\phi_f = V_T ln\left(\frac{N_{ch}}{n_i}\right)$ .

simplified as

$$I_{ch} = \frac{W\mu_{ch}C_{ox}}{L_{ch}} \left( V_{inv,0} - \frac{1}{2}\zeta\Delta\psi_s + \zeta V_T \right) \Delta\psi_s \tag{3.5}$$

where  $\Delta \psi_s = \psi_{s,L} - \psi_{s,0}$ . Mobility reduction due to lateral fields which accounts for velocity saturation is given by

$$\mu_{ch} = \frac{\mu_{eff,ch}}{1 + \theta_{3.ch} \Delta \psi_s} \tag{3.6}$$

where  $\theta_{3,ch}=\frac{\mu_{0,ch}}{L_{ch}v_{sat}}$  is the parameter that takes care of velocity saturation in the channel, where  $\mu_{0,ch}$  is the zero field channel mobility and  $v_{sat}$  is the saturation velocity in channel.  $\mu_{eff,ch}$  accounts for mobility reduction due to the vertical field and is given by

$$\mu_{eff,ch} = \frac{\mu_{0,ch}}{\left(1 + \theta_1 V_{inv,0} + \theta_2 \left(\sqrt{\psi_{s,0}} - \sqrt{\psi_{s,0} \mid_{V_{SB}=0}}\right)\right)}$$

(3.7)

where  $\theta_1$  and  $\theta_2$  are model parameters. Substituting (3.6) and (3.7) in (3.5) and by replacing  $\Delta \psi_s = \psi_{s,L} - \psi_{s,0}$  by  $V_{DiS}^3$ , gives the channel current as

$$I_{ch} = \frac{W\mu_{ch}C_{ox}}{L_{ch}} \left( V_{inv,0} - 0.5\zeta V_{DiS} + \zeta V_T \right) V_{DiS}.$$

(3.8)

This equation is true only until the onset of saturation. To incorporate saturation into the model, one must find  $\frac{dI_{ch}}{dV_{DiS}}$   $|_{V_{DiS}=V_{sat,ch}}=0$ . This gives us the channel saturation potential  $(V_{sat,ch})$  as

$$V_{sat,ch} = \frac{\frac{2V_{inv,0}}{\zeta}}{1 + \sqrt{1 + \frac{2\theta_{3,ch}V_{inv,0}}{\zeta}}}.$$

(3.9)

The final expression of channel current then becomes

$$I_{ch} = (1 + \lambda_{ch} V_{DiS}) \frac{W \mu_{eff,ch} C_{ox}}{L_{ch}} \frac{(V_{inv,0} - 0.5 \zeta V_{DiS,eff} + \zeta V_T) V_{DiS,eff}}{(1 + \theta_{3,ch} V_{DiS,eff})}$$

(3.10)

where  $\lambda_{ch}$  is the channel modulation parameter and  $V_{DiS,eff}$  is the minimum of  $V_{DiS}$  and  $V_{sat,ch}$ . In order to ensure that the current curve is smooth and differentiable at all points, appropriate smoothing function is used which smoothly connects the  $I_{ch}$  before  $V_{sat,ch}$  with the saturation current value  $I_{ch,sat}$ .

<sup>&</sup>lt;sup>3</sup>Note: Difference between the surface potential  $\Delta \psi_s$  is equal to the applied potential  $V_{DiS}$  only beyond the threshold voltage.

#### 3.1.2 Formulation of current under gate oxide

The drift current formulation is done in terms of the Quasi-Fermi potential as opposed to the surface potential formulation for the channel current. The current in Reg-II can be written as

$$I_{dr} = \frac{W\mu_{dr}}{L_{dr}} \int_{V_{D_i}}^{V_{D'}} \left(-Q_n^{dr}\right) dV_c \tag{3.11}$$

where W is the drift region width  $L_{dr}$  is the drift region length and  $\mu_{dr}$  is Reg-II mobility taking into effect of mobility reduction due to lateral and vertical electric fields. In the channel current formulation, flow of electrons was only through the inversion layer but in Reg-II, flow of electrons is through accumulation, depletion and the bulk. Hence one must take all these charges into account while formulating  $Q_n^{dr}$ . Hence, one can express  $Q_n^{dr}$  as

$$Q_n^{dr} = -q N_{dr} t_{si} + Q_{acc}^{dr} - Q_{dep}^{dr}, V_{GC} > V_{FB,dr}$$

$$Q_n^{dr} = -q N_{dr} t_{si} - Q_{inv}^{dr} - Q_{dep}^{dr}, V_{GC} < V_{FB,dr}$$

(3.12)

where  $N_{dr}$  is the doping concentration,  $t_{si}$  is the silicon film thickness,  $Q_{acc}^{dr}$ , the accumulation charge per unit area,  $Q_{inv}^{dr}$  is the inversion charge per unit area and  $Q_{dep}^{dr}$  is the depletion charge per unit area. The first term accounts for electron flow through the bulk of Reg-II<sup>4</sup>, the second and third terms are for electron flow through the accumulation/inversion and the depletion layers. One must note that depending upon the value of  $V_C$ , one can have accumulation, inversion or depletion charges. Since the bias voltages are sufficiently positive, contribution from inversion charges is really negligible. One can write the potential balance equation in Reg-II as

$$V_{GC} = V_{FB,dr} + \psi_s^{dr} - \frac{(Q_{surf}^{dr} - Q_{dep}^{dr})}{C_{or}}$$

(3.13)

where  $Q_{surf}^{dr}$  is  $+Q_{acc}^{dr}$  or  $-Q_{inv}^{dr}$  depending upon the value of  $V_{GC}$ . One can rewrite the above expression in terms of charges as

$$(Q_{surf}^{dr} - Q_{den}^{dr}) = Q_{oute}^{dr} = -C_{ox} (V_{GC} - V_{FB,dr} - \psi_s^{dr}).$$

(3.14)

<sup>&</sup>lt;sup>4</sup>Note that the expression  $qN_{dr}t_{si}$  is an approximation. In depletion condition most of the silicon film in Reg-II is depleted and the contribution from bulk charge will be less than  $qN_{dr}t_{si}$ . However, under accumulation condition, this expression holds true.

Based on the region of operation one can make appropriate approximation to the above expression. When  $V_{GC} > V_{FB,dr}$ , accumulation layer will be formed and depletion charge is negligible. Also, under accumulation condition, most of the voltage drop occurs across the gate oxide and value of surface potential is negligible. Hence, one can rewrite (3.14) as

$$Q_{qate}^{dr} = -C_{ox} \left( V_{GC} - V_{FB,dr} \right). {(3.15)}$$

When  $V_{GC} < V_{FB,dr}$ , depletion charges will be in abundance and there will be negligible inversion charge (as long as voltage below the threshold voltage of Reg-II). One can express  $Q_{dep}^{dr}$  as  $k_{dr}C_{ox}\sqrt{-\psi_s^{dr}}$  where  $k_{dr}$  is the body coefficient of Reg-II. One can rewrite (3.14) as

$$-k_{dr}C_{ox}\sqrt{-\psi_{s}^{dr}} = -C_{ox}\left(V_{GC} - V_{FB,dr} - \psi_{s}^{dr}\right). \tag{3.16}$$

Solving the above quadratic expression gives us an expression for  $Q_{gate}^{dr}$  which is

$$Q_{gate}^{dr} = k_{dr}C_{ox}\left(-0.5k_{dr} + \sqrt{(0.5k_{dr})^2 - (V_{GC} - V_{FB,dr})}\right). \tag{3.17}$$

Total charge  $Q_n^{dr}$  can now be written as

$$Q_n^{dr} = -qN_{dr}t_{si} + Q_{qate}^{dr} = -qN_{dr}t_{si} - C_{ox}\left(V_{GC} - V_{FB,dr} - \psi_s^{dr}\right). \tag{3.18}$$

Following the same approach as previous section, one can linearize the above charge with respect to the terminal  $D_i$ . If we consider  $V_n^{dr} = -\frac{Q_n^{dr}}{C_{ox}}$ , then one can write  $V_n^{dr}$  as

$$V_n^{dr} = V_n^{dr} \mid_{V_c = V_{D_i}} - (V_c - V_{D_i})$$

(3.19)

where the linearization coefficient is one<sup>5</sup> The mobility reduction due to lateral and perpendicular fields is modeled similar to the channel region as follows

$$\mu_{dr} = \frac{\mu_{eff,dr}}{\left(1 + \theta_{3,dr} V_{D'D_i}\right)} \tag{3.20}$$

<sup>&</sup>lt;sup>5</sup>Dependence of  $\psi_s$  on  $V_c$  is neglected to get a linearization coefficient of one. This is valid in accumulation region where the value of  $\psi_s$  is negligible. However, neglecting it in the depletion region is debatable.

where  $\theta_{3,dr}=\frac{\mu_{0,dr}}{L_{dr}v_{sat}}$  is the parameter that takes into account velocity saturation in Reg-II, with  $v_{sat}$  being the saturation velocity<sup>6</sup> and  $\mu_{0,dr}$  being the zero field mobility.  $\mu_{eff,dr}$  account for the mobility reduction due to vertical field and is given by

$$\mu_{eff,dr} = \frac{\mu_{0,dr}}{\left(1 + \theta_{acc} \left(0.5 V_{GD_i} + 0.5 V_{GD'} - V_{FB,dr}\right)\right)}$$

(3.21)

where  $\theta_{acc}$  is a model parameter. Substituting (3.19 , 3.21) in (3.11) gives Reg-II current as

$$I_{dr} = \frac{W\mu_{dr}C_{ox}}{L_{dr}} \left( V_n^{dr} \mid_{V_c = V_{D_i}} -0.5V_{D'D_i} \right) V_{D'D_i}.$$

(3.22)

This model is only till the onset of saturation. To model saturation, one must compute the saturation potential by forcing  $\frac{dI_{dr}}{dV_{D'D_i}} \mid_{V_{D'D_i}=V_{sat,dr}} = 0$ . This gives the Reg-II saturation potential as

$$V_{sat,dr} = \frac{2V_n^{dr} \mid_{V_c = V_{D_i}}}{1 + \sqrt{1 + 2\theta_{3,dr} V_n^{dr} \mid_{V_c = V_{D_i}}}}.$$

(3.23)

The final expression for Reg-II is given by

$$I_{dr} = \frac{W\mu_{eff,dr}C_{ox}}{L_{dr}} \frac{\left(V_n^{dr} \mid_{V_c = V_{D_i}} -0.5V_{D'D_{i,eff}}\right)V_{D'D_{i,eff}}}{\left(1 + \theta_{3,dr}V_{D'D_{i,eff}}\right)}$$

(3.24)

where  $V_{D'D_i,eff}$  is the effective potential drop across Reg-II which is the minimum of  $V_{D'D_i}$  and  $V_{sat,dr}$ . The transition from linear region to the saturation region is made differentiable by using appropriate smoothing function.

# 3.1.3 Formulation of current under field oxide

The drift region under the field oxide can be modeled as a resistor since that region is not affected by the gate potential. However, one must note that it is this region which is responsible for quasi-saturation at higher gate voltages. After the onset of quasi-saturation, drift length modulation occurs resulting in increase in current with drain voltage. Hence these two effects must be taken into account while modeling in this

<sup>&</sup>lt;sup>6</sup>Note: Saturation velocity in channel and drift region are different

region. One can write the current flowing through this region as

$$I_{dr1} = \frac{(1 + \lambda_{dr1} V_{DD'}) q N_{dr1} \mu_{dr1} V_{DD'} W t_{si}}{L_{LC} \left(1 + \theta_{1,dr1} \frac{V_{DD'}}{L_{LC} E_C}\right)^{1/\theta_{dr1}}}$$

(3.25)

where  $N_{dr1}$  is the drift layer doping concentration,  $\mu_{dr1}$  is the effective mobility taking into account velocity saturation,  $V_{DD'}$  is the potential drop in Reg-III and  $t_{si}$  is silicon film thickness. The drift length modulation parameter is given by  $\lambda_{dr1}$ . Model parameters  $\theta_{1,dr1}$  and  $\theta_{dr1}$  account for velocity saturation in this region.

The current models  $I_{ch}$ ,  $I_{dr}$  and  $I_{dr1}$  derived in (3.10), (3.24) and (3.25) are used in the model circuit as shown in Fig 3.1. These three current sources are in series and under any bias, each of these current sources must converge to the same value. The potential drops  $V_{DiS}$ ,  $V_{D'D_i}$  and  $V_{DD'}$  get adjusted so that  $I_{ch}$ ,  $I_{dr}$  and  $I_{dr1}$  have the same value.

# 3.2 Charge model

Various capacitances of LDMOS can be calculated only if the charges in various regions are modeled appropriately. Before analyzing the charges present in LDMOS, looking at the charge formulation in a normal MOSFET is important. Once the MOSFET charge model becomes clear, one can extrapolate the same concepts to LDMOS with minor variations. Let us consider a 4 terminal NMOSFET and try calculating various capacitances present in the device. Note that by capacitance, one implies that it is the small signal capacitance which is defined as  $C_{ij} = (2\delta_{ij} - 1) \frac{\partial Q_i}{\partial V_j}$  where  $(i, j) \in (G, D, S, B)$  and  $Q_i$  is the charge associated with each terminal. From charge conservation principle, one can write

$$Q_G + Q_D + Q_S + Q_B = 0. (3.26)$$

The gate charge is negative of the sum of charges present beneath the gate oxide viz. depletion and inversion/accumulation charges. Let  $q_{dep}$  be the depletion charge per unit area and  $q_{surf}$  be the surface charge per unit area.  $q_{surf}$  is the inversion charge if  $V_{GB} > V_{FB}$  else is the accumulation charge  $q_{acc}$ . Gate charge  $Q_G$  can now be defined

as follows

$$Q_G = -W \int_0^{L_{ch}} (q_{surf} + q_{dep}) dx$$

(3.27)

where W is the width and  $L_{ch}$  is the channel length of the device. It is assumed that the charges vary only along the length of the device and variation along the width is uniform.  $q_{dep}$  is attributed to the bulk terminal as depletion charges are fixed charges. Now,  $q_{surf}$  has to be partitioned between the drain and source terminal so that

$$Q_D + Q_S = W \int_0^{L_{ch}} q_{surf} dy.$$

(3.28)

Partitioning between the source and drain charge is achieved through the Ward-Dutton partition function (Ward and Dutton, 1978), (Oh *et al.*, 1980). The formulation of partition function is explained in next section.

#### 3.2.1 Ward-Dutton (WD) Partitioning Scheme

Current transport equation for an NMOSFET can be written as

$$I(x,t) = qW\mu_n n_s(x,t) \frac{\partial V}{\partial x}$$

(3.29)

where  $n_s$  is the electron concentration per unit area along the length of the device and V is the quasi-Fermi level which ranges from  $V = V_{SB}$  at x = 0 to  $V = V_{DB}$  at x = L. This derivation assumes that mobility is constant throughout the length of the device and that the device operates in the quasi-static regime. The current continuity equation (neglecting generation and recombination) can be written as

$$\frac{\partial n_s}{\partial t} = -\frac{1}{qW} \frac{\partial I(x,t)}{\partial x}.$$

(3.30)

The electron concentration  $n_s(x,t)$  is a function of both position and time. It can alternatively be represented in terms of the quasi-Fermi potential and gate potential as

$$n_s(x,t) \equiv n_s (V(x,t), V_G(t)) = n_s (V, V_G)$$

(3.31)

where the position dependence is incorporated into the quasi-Fermi potential and the time dependence is incorporated into both quasi-Fermi and gate potentials. This representation is useful while integrating the charge in future. (3.30) is integrated from 0 to x and the obtained I(x,t) is substituted back in (3.29) to get

$$qW \int_{0}^{x} \frac{\partial n_{s}(x',t)}{\partial t} dx' = -q\mu W n_{s}(V,V_{G}) \frac{\partial V}{\partial x} + I(0,t).$$

(3.32)

Integrating the above equation again from x = 0 to x = L and solving for I(0) one gets

$$I(0,t) = \frac{q\mu W}{L} \int_{V_{SB}(t)}^{V_{DB}(t)} n_s(V, V_G) dV + \frac{qW}{L} \int_0^L \int_0^x \frac{\partial n_s(x', t)}{\partial t} dx' dx$$

(3.33)

where the first term on the RHS is the conduction current as defined in (3.29), and the second term is the displacement current. The above equation can be re-written as

$$I(0,t) = I_0(t) - \frac{d}{dt} \left\{ -q \frac{W}{L} \int_0^L \int_0^x n_s(x',t) dx' dx \right\}.$$

(3.34)

Now, one can write the source transient current  $I_S(t)$  as a linear combination of steady state current  $I_0(t)$  and as a derivative of the source charge, where the source charge  $Q_S$  is

$$Q_S = -q \frac{W}{L} \int_0^L \int_0^x n_s(x', t) dx' dx$$

$$= -qW \int_0^L \left(1 - \frac{x}{L}\right) n_s(x, t) dx.$$

(3.35)

A similar derivation when done for the drain charge, gives us

$$Q_D = -qW \int_0^L \left(\frac{x}{L}\right) n_s(x, t) dx. \tag{3.36}$$

Since  $n_s(x,t)$  is the electron concentration in the inversion region,  $-qn_s(x,t)$  will be the inversion charge per unit area. Hence, one can write the source and drain charges as

$$Q_D = W \int_0^L \frac{x}{L} q_{inv} dx$$

$$Q_S = W \int_0^L \left(1 - \frac{x}{L}\right) q_{inv} dx.$$

(3.37)

Figure 3.2: EC Model for static and dynamic currents in NMOSFET.

The x/L factor linearly partitions the inversion charge between the source and drain terminals and it is called as the Ward-Dutton (WD) partition factor. To summarise, charges associated with various terminals can be written as

$$Q_G = -W \int_0^{L_{ch}} (q_{surf} + q_{dep}) dx$$

$$Q_D = W \int_0^L \frac{x}{L} q_{inv} dx$$

$$Q_S = W \int_0^L \left(1 - \frac{x}{L}\right) q_{inv} dx$$

$$Q_B = -\left(Q_G + Q_D + Q_S\right).$$

(3.38)

The above charge model is implemented in an equivalent circuit as shown in Fig 3.2. Here the charges are represented as displacement current terms connected from respective terminals to bulk. By charge conservation, bulk displacement current term is automatically calculated. The procedure shown above for calculating charges is used in LDMOS charge modeling with slight variations as discussed in the following section.

# **3.2.2** Modified Ward-Dutton (MWD) partitioning scheme

WD partition deals with partitioning charges in a MOSFET. One can apply the same principle to an LDMOS which has 3 distinct internal regions present in it, namely Reg-I, II and III. Reg-I and Reg-II, show capacitive effects due to the influence of gate

terminal. Reg-III, on the other hand, is modeled purely as a resistor with no capacitive effects in that region. MEDICI simulations also agree with this conjecture. Hence, it is sufficient if one considers Reg-I and II for the charge model. LDMOS, with Reg-I and II can be thought of as a device with two distinct internal regions and an internal node designated by  $D_i$ .

Firstly, the partition scheme adopted by MM20 model(MM2, 2008),(Grabinski and Gneiting, 2010) will be discussed. This model provides a partitioning scheme known as Modified WD partitioning, but does not provide a physical basis behind it. Also, this model does not fit well with the device simulations. This section aims to derive the Modified WD partition scheme from first principles and highlight the error committed during the derivation. Apart from that, it also provides an alternative to this partition scheme which is physically sound and is shown to be reasonably accurate with device simulations.

Let us consider Reg-I and Reg-II of LDMOS with terminals S,  $D_i$  and D' as shown in Fig 2.1. Modified WD partitioning provides a partition scheme as follows

$$Q_{G} = W \left[ \int_{0}^{L_{ch}} \left( qn_{ch} + qn_{dep} \right) dx + \int_{0}^{L_{dr}} \left( qn_{dr} \right) dx \right]$$

$$Q_{D'} = W \left[ \int_{0}^{L_{ch}} \left( \frac{x}{(L_{ch} + L_{dr})} \left( -qn_{ch} \right) \right) dx + \int_{L_{ch}}^{L_{ch} + L_{dr}} \left( \frac{x}{(L_{ch} + L_{dr})} \left( -qn_{dr} \right) \right) dx \right]$$

$$Q_{S} = W \int_{0}^{L_{ch}} \left( \left( 1 - \frac{x}{(L_{ch} + L_{dr})} \right) \left( -qn_{ch} \right) \right) dx$$

$$+ W \int_{L_{ch}}^{L_{ch} + L_{dr}} \left( \left( 1 - \frac{x}{(L_{ch} + L_{dr})} \right) \left( -qn_{dr} \right) \right) dx$$

$$Q_{B} = - \left( Q_{G} + Q_{D}' + Q_{S} \right)$$

$$(3.39)$$

where  $n_{ch}$  and  $n_{dr}$  are the electron densities in the channel and drift region which appear in the current formulation ( $n_{ch}$  is typically the inversion charge in the channel region and  $n_{dr}$  is the accumulation and depletion charges in the drift region) and  $n_{dep}$  is the depletion charge density in the channel region.

Figure 3.3: EC Model for static and dynamic MOSFET currents - MM20.

Fig 3.3 shows the equivalent circuit model of MM20 model. The charges are assigned to four terminals viz. gate, terminal D', source and bulk. From each of these terminals a displacement current source  $\frac{dQ}{dt}$  is connected to the bulk terminal which acts as a reference for our analysis. Due to the circuit topology and by charge conservation,  $\frac{dQ_B}{dt}$  is calculated automatically. Note that there is no explicit displacement current source from the drain terminal. This is because the region between terminal D' and drain does not contain any charge quantity that varies with bias. Though there is no explicit connection to the drain terminal, internal displacement currents ensure that a time varying current flows from drain whenever there is a variation in gate, drain or source bias.

One can try deriving the above result from fundamental equations and check its validity. Current equation for any region can be written as

$$I(x,t) = qW\mu n_s(x,t)\frac{\partial V(x,t)}{\partial x}.$$

(3.40)

Continuity relation (neglecting recombination and generation) is given by

$$\frac{\partial n_s(x,t)}{\partial t} = -\frac{1}{qW} \frac{\partial I(x,t)}{\partial x}.$$

(3.41)

Following the approach similar to sec 3.2.1, integration of the above equation is done with respect to x, with limits ranging from 0 to x and again with respect to x with limits

ranging from 0 to  $L_{ch} + L_{dr}$  to give

$$\frac{qW}{(L_{ch} + L_{dr})} \int_0^{L_{ch} + L_{dr}} \int_0^x \frac{\partial n_s(x', t)}{\partial t} dx' dx = -\frac{qW\mu}{L_{ch} + L_{dr}} \int_{V_{SB}}^{V_{D'B}} n_s(V, V_G) dV + I(0, t).$$

(3.42)

The above equation can be reduced to give

$$I(0,t) = \frac{(L_{ch}I_{ch}(t) + L_{dr}I_{dr}(t))}{L_{ch} + L_{dr}} - \frac{qW}{L_{ch} + L_{dr}} \frac{d}{dt} \left\{ \int_{0}^{L_{ch} + L_{dr}} \int_{0}^{x} \frac{\partial n_{s}(x',t)}{\partial t} dx' dx \right\}.$$

(3.43)

The displacement current term can be reduced to give

$$I(0,t) = \frac{(L_{ch}I_{ch}(t) + L_{dr}I_{dr}(t))}{L_{ch} + L_{dr}} - W\frac{d}{dt} \left\{ \int_{0}^{L_{ch}} \left( 1 - \frac{x}{L_{ch} + L_{dr}} \right) (-qn_{ch}) dx \dots + \int_{L_{ch}}^{L_{ch} + L_{dr}} \left( 1 - \frac{x}{L_{ch} + L_{dr}} \right) (-qn_{dr}) dx \right\}.$$

(3.44)

One can observe that the displacement current term obtained in the above expression is exactly equal to the MM20 expression. Total current is equal to the sum of conduction and displacement current only if the first term can be written as  $I_{conduc}(t)$ . Note that only under steady state condition,  $I_{ch}(t)$  is equal to  $I_{dr}(t)$  and only then the first term can be written as a single current term. If the system is not in steady-state then  $I_{ch}$  need not be equal to  $I_{dr}$  and one cannot equate the second term completely to the displacement current<sup>7</sup>. The first expression will have some contribution to the displacement term which has been neglected in the MM20 modeling. Since they assume that  $I_{ch}(t)$  and  $I_{dr}(t)$  are equal at all points of time, the two current sources are in series. Now one is interested in finding out the additional term that needs to be included in the displacement current expression, given the fact that these two conduction currents are forced to be equal. The expression for source current can be written as

$$I(0,t) = \frac{(L_{ch}I_{ch}(t) + L_{dr}I_{dr}(t))}{L_{ch} + L_{dr}} - W\frac{dQ_S}{dt}$$

(3.45)

Under small signal analysis, let us assume that  $I_{ch}(t)$  lags  $I_{dr}(t)$  by a constant time delay  $\tau$ . This implies that

$$I_{ch}(t) = I_{dr}(t - \tau) \tag{3.46}$$

<sup>&</sup>lt;sup>7</sup>This arises because the two regions are electrostatically different and under a transient input, both the currents will achieve the same value only when the input stabilizes to a steady state value. However, these two currents will be same if Reg-I and Reg-II were electrostatically identical.

If we transform (3.45) to Fourier domain, and use the above relation then we get

$$I(0,t) = \frac{L_{ch}I_{dr}e^{-j\omega\tau} + L_{dr}I_{dr}}{L_{ch} + L_{dr}} - j\omega Q_S$$

(3.47)

If one operates at a frequency  $\omega$  such that  $\omega \tau$  is a small quantity, then  $e^{-j\omega\tau}$  can be approximated as  $1-j\omega\tau$ . If this approximation is invoked in (3.47), then the source current can be written as

$$I(0,t) = I_{dr}(t) - j\omega \left\{ Q_S + \frac{L_{ch}I_{dr}\tau}{L_{ch} + L_{dr}} \right\}$$

$$= I_{dr}(t) - \frac{d}{dt} \left\{ Q_S + \frac{L_{ch}I_{dr}\tau}{L_{ch} + L_{dr}} \right\}$$

(3.48)

The above expression for source current now has been completely separated into conduction term and a displacement current with a correction to the displacement current. MM20 have neglected this correction to their equivalent circuit model. It is shown in sec 4.0.6 that adding the correction term to the MM20 model does give an improvement to the capacitance model. Note that this correction term is based on the assumption that the time delay  $\tau$  is a constant. Hence, it can work only in cases where this assumption holds true and cannot be generalised for any condition.

The problem faced in MM20 model where the total current cannot be expressed as a sum of conduction and displacement current for any given condition can be overcome if we do not consider Reg-I and Reg-II together and treat each one of them separately. WD partition as seen in sec 3.2.1 can be applied to each region to get terminal charges  $Q_S$ ,  $Q_{D_i}$  and  $Q_{D'}$ . Note that this approach never makes an assumption that the conduction currents  $I_{ch}(t)$  and  $I_{dr}(t)$  should be equal. Hence, the new partition model can be

expressed as

$$Q_{G} = W \left[ \int_{0}^{L_{ch}} (qn_{ch} + qn_{dep}) dx + \int_{0}^{L_{dr}} (qn_{dr}) dx \right]$$

$$Q_{S} = W \int_{0}^{L_{ch}} \left( 1 - \frac{x}{L_{ch}} \right) (-qn_{ch}) dx$$

$$Q_{D_{i}} = W \int_{0}^{L_{ch}} \left( \frac{x}{L_{ch}} \right) (-qn_{ch}) dx + W \int_{0}^{L_{dr}} \left( 1 - \frac{x}{L_{dr}} \right) (-qn_{dr}) dx$$

$$Q_{D'} = W \int_{0}^{L_{dr}} \left( \frac{x}{L_{dr}} \right) (-qn_{dr}) dx$$

$$Q_{B} = -\left( Q_{G} + Q'_{D} + Q_{D_{i}} + Q_{S} \right)$$

(3.49)

where  $D_i$  gets contribution both from channel and drift regions. This model can be implemented in an equivalent circuit as shown in Fig 3.4. The total gate charge is computed from both channel and drift regions and is modeled as a displacement current  $\frac{dQ_G}{dt}$  from gate to bulk. Other terminal charges are modeled as  $\frac{dQ}{dt}$  current sources from the respective terminals to bulk. Note that bulk is chosen as a reference terminal and connecting all the displacement current sources ensures that charge conservation is maintained.  $Q_B$  is not calculated explicitly and the connection of current sources in the topology given in the figure gives  $Q_B$  automatically.

Figure 3.4: EC Model for static and dynamic MOSFET currents.

Note that this model is valid under all conditions as current in each region is expressed as a sum of conduction and displacement currents. The modification that this model offers against MM20 is the addition of an extra displacement current source from  $D_i$  terminal to the bulk.

#### 3.2.3 Formulation of charge in channel region

Since the channel region of SOI-LDMOS is structurally similar to NMOSFET, charge modeling should be similar to MOS charge modeling. Charges that are of interest to us are the depletion and inversion/accumulation charges. Depletion charge  $q_{dep}$  can be written as

$$q_{dep} = -sgn\left(\psi_s^{ch}\right) C_{ox} k_{ch} \sqrt{abs\left(\psi_s^{ch}\right)}$$

(3.50)

where  $\psi^{ch}_s$  is the surface potential of the channel and sgn is the signum function. The above expression holds good for all regions of operations ranging from accumulation, depletion to inversion. Inversion/accumulation charge<sup>8</sup> is given as

$$q_{surf} = -C_{ox} \left( V_{GB} - V_{FB,ch} - \psi_s^{ch} - sgn\left(\psi_s^{ch}\right) k_{ch} \sqrt{abs\left(\psi_s^{ch}\right)} \right). \tag{3.51}$$

Potentials  $V_{dep}$  and  $V_{surf}$  can be defined as  $V_{dep} = -\frac{q_{dep}}{C_{ox}}$  and  $V_{surf} = -\frac{q_{surf}}{C_{ox}}$  so that the analysis of charges can be done completely in terms of potentials. Since  $V_{dep}$  and  $V_{surf}$  are non-linear functions of surface potential, approximations of these charges are done with respect to the source terminal (similar to Sec 3.1.1) as

$$V_{dep} = V_{dep} \mid_{\psi_s^{ch} = \psi_{s,0}^{ch}} + (\zeta - 1) \left( \psi_s^{ch} - \psi_{s,0}^{ch} \right)$$

$$V_{surf} = V_{surf} \mid_{\psi_s^{ch} = \psi_{s,0}^{ch}} - \zeta \left( \psi_s^{ch} - \psi_{s,0}^{ch} \right)$$

(3.52)

where  $\zeta=\left(1+\frac{1}{2\sqrt{abs(\psi^{ch}_{s,0})}}\right)$ . The charges have now been defined and approximated with respect to the source terminal. To obtain the final gate, source and drain expressions, one must know the variation of charge densities as a function of x. Hence, one must find the dependence of  $\psi_s$  with x so that the charges can be expressed as a function of x. To obtain that, one uses the channel current expression. The channel

<sup>&</sup>lt;sup>8</sup>Shall henceforth be called as surface charge to avoid ambiguity.

current can be written as

$$I_{ch} = W\mu_{ch}C_{ox}\left(V_{surf}\frac{d\psi_s}{dx} - V_T\frac{dV_{surf}}{dx}\right)$$

(3.53)

where the parameters in the equations are as defined in sec 3.1.1. Only modification that has been made to this equation has been changing  $V_{inv}$  to  $V_{surf}$  to make the analysis generic for any given gate bias. Incorporating the linearization made in (3.52) and integrating the above expression from 0 to x, one obtains

$$I_{ch}x = W\mu_{ch}C_{ox} \left[ \int_{\psi_{s,0}}^{\psi_{s}(x)} \left( V_{surf,0} - \zeta \left( \psi_{s} - \psi_{s,0} \right) \right) d\psi_{s} + \zeta V_{T} \int_{\psi_{s,0}}^{\psi_{s}(x)} d\psi_{s} \right]. \quad (3.54)$$

Upon replacing  $I_{ch}$  with (3.5) and simplifying one can get

$$x = L_{ch} \left[ \frac{(V_{surf,0} + \zeta \psi_{s,0} + \zeta V_T) (\psi_s(x) - \psi_{s,0}) - \zeta \left(\frac{\psi_s(x)^2 - \psi_{s,0}^2}{2}\right)}{\left(V_{inv,0} - \frac{1}{2}\zeta \Delta \psi_s + \zeta V_T\right) \Delta \psi_s} \right]. \quad (3.55)$$

Instead of expressing  $\psi_s$  as a function of x, x has been represented as a function of  $\psi_s$ . This is to make future integration calculations simpler. Since the drain and source terminals for the channel region in LDMOS are  $D_i$  and S terminals, charge partitioning is done between those two terminals. Now one can proceed to calculate various charges as follows

$$Q_{G}^{ch} = WC_{ox} \int_{0}^{L_{ch}} \left( V_{surf,0} + V_{dep,0} \right) - \left( \psi_{s}(x) - \psi_{s,0} \right) dx$$

$$Q_{D_{i}}^{ch} = -WC_{ox} \int_{0}^{L_{ch}} \left( \frac{x}{L_{ch}} \right) \left( V_{surf,0} - \zeta \left( \psi_{s}(x) - \psi_{s,0} \right) \right) dx$$

$$Q_{S}^{ch} = -WC_{ox} \int_{0}^{L_{ch}} \left( 1 - \frac{x}{L_{ch}} \right) \left( V_{surf,0} - \zeta \left( \psi_{s}(x) - \psi_{s,0} \right) \right) dx.$$

(3.56)

<sup>&</sup>lt;sup>9</sup>If  $\psi_s$  is represented as a function of x, then one encounters polynomial under square root during the integration computation which is cumbersome to solve. Writing x in terms of  $\psi_s$  results in solving quadratic expression under integral.

After integration, various charge expressions are

$$Q_{G}^{ch} = C_{ox}WL_{ch} \left[ V_{GB} - V_{FB}^{ch} - \frac{1}{2} \left( \psi_{sD_{i}} + \psi_{ss} \right) + \frac{F_{ch}}{12\zeta} \Delta V_{GT} \right]$$

$$Q_{D_{i}}^{ch} = -\frac{C_{ox}}{2}WL_{ch} \left[ \bar{V}_{GT} - \frac{\Delta V_{GT}}{6} \left( 1 - \frac{F_{ch}}{2} - \frac{F_{ch}^{2}}{20} \right) \right]$$

$$Q_{S}^{ch} = -\frac{C_{ox}}{2}WL_{ch} \left[ \bar{V}_{GT} - \frac{\Delta V_{GT}}{6} \left( 1 - \frac{F_{ch}}{2} - \frac{F_{ch}^{2}}{20} \right) \right]$$

(3.57)

where

$$\Delta V_{GT} = V_{surf,0} - V_{surf,L_{ch}}, \ \bar{V}_{GT} = \frac{V_{surf,0} + V_{surf,L_{ch}}}{2}, \ F_{ch} = \frac{\Delta V_{GT}}{\bar{V}_{GT} + \zeta V_{T}}.$$

(3.58)